- 94.50 KB

- 2022-04-22 11:48:16 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

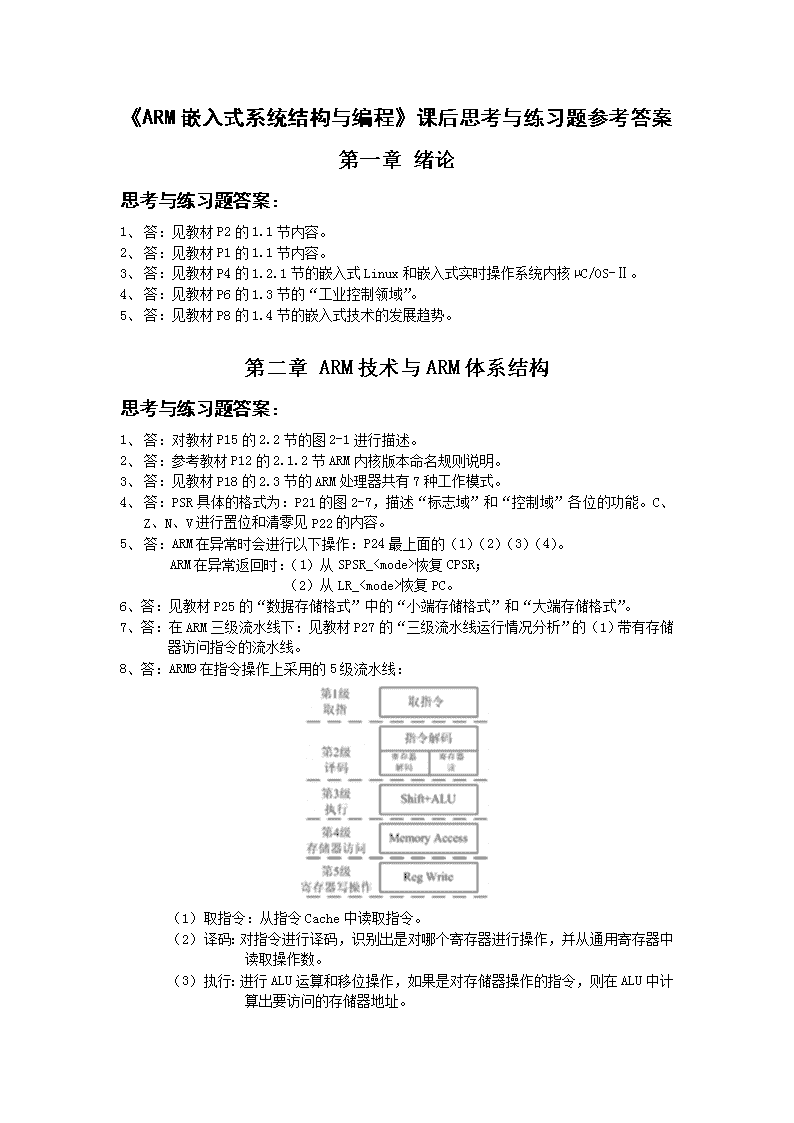

'《ARM嵌入式系统结构与编程》课后思考与练习题参考答案第一章绪论思考与练习题答案:1、答:见教材P2的1.1节内容。2、答:见教材P1的1.1节内容。3、答:见教材P4的1.2.1节的嵌入式Linux和嵌入式实时操作系统内核µC/OS-Ⅱ。4、答:见教材P6的1.3节的“工业控制领域”。5、答:见教材P8的1.4节的嵌入式技术的发展趋势。第二章ARM技术与ARM体系结构思考与练习题答案:1、答:对教材P15的2.2节的图2-1进行描述。2、答:参考教材P12的2.1.2节ARM内核版本命名规则说明。3、答:见教材P18的2.3节的ARM处理器共有7种工作模式。4、答:PSR具体的格式为:P21的图2-7,描述“标志域”和“控制域”各位的功能。C、Z、N、V进行置位和清零见P22的内容。5、答:ARM在异常时会进行以下操作:P24最上面的(1)(2)(3)(4)。ARM在异常返回时:(1)从SPSR_恢复CPSR;(2)从LR_恢复PC。6、答:见教材P25的“数据存储格式”中的“小端存储格式”和“大端存储格式”。7、答:在ARM三级流水线下:见教材P27的“三级流水线运行情况分析”的(1)带有存储器访问指令的流水线。8、答:ARM9在指令操作上采用的5级流水线:(1)取指令:从指令Cache中读取指令。(2)译码:对指令进行译码,识别出是对哪个寄存器进行操作,并从通用寄存器中读取操作数。(3)执行:进行ALU运算和移位操作,如果是对存储器操作的指令,则在ALU中计算出要访问的存储器地址。

(1)存储器访问:如果是对存储器访问的指令,用来实现数据缓冲功能(通过数据Cache);如果不是对存储器访问的指令,本级流水线为一个空的时钟周期。(2)寄存器回写:将指令运算或操作结果写回到目标寄存器中。9、答:见教材P29的“5级流水线互锁分析”的内容。第二章ARM指令集寻址方式思考与练习题答案:1、答:见教材P32的3.1节中“2.指令条件码”的内容。2、答:当指令的算术运算发生异常时,V标志位置1。例如:两个正数相加,其结果为一负数;或者两个负数相加,其结果为一正数,都会置V标志位。3、答:每一个立即数是由一个8位的常数进行32位循环右移偶数位得到的,其中循环右移的位数是由一个4位二进制数的两倍表示的,即:=immed_8进行32位循环右移(2*rotate_4)位,符合这一条件的都为合法的立即数。(1)0x54300B0101010000110000不合法(2)0x1080B000100001000111101000010(3)0x3040B001100000100111111000001(4)0x5010B010100000001不合法(5)0xfb100000B1111101100010000000000000000不合法(6)0x3340000B001100110100000000000000100111001101(7)0x3FC0000B001111111100000000000000100101111111(8)0x1FE00000B0001111111100000000000000000不合法(9)0x55800000B0101010110000000000000000000不合法(10)0x7F8000B01111111100000000000不合法(11)0x39C0000B001110011100000000000000100111100111(12)0x1FE800000B00011111111010000000000000000000不合法4、答:见教材P33的3.2节图3-1移位操作功能描述。5、答:ARM数据处理指令具体的寻址方式有5种:见教材P33的“2.具体寻址类型”内容。如果程序计数器PC作为目标寄存器,会产生程序发生跳转。6、答:

在Load/Store指令寻址中,字、无符号字节的Load/Store指令寻址有三种,具体见教材P36的3.3.2节内容。在Load/Store指令寻址中,半字、有符号字节寻址有两种,具体见教材P40的3.3.3节内容。它们之间的差别:在半字、有符号字节寻址中,没有Addressing_mode中的偏移量通过寄存器移位得到的形式。1、答:见教材P45的“2.内存操作”内容。2、答:见教材P46的四种类型的堆栈工作方式。栈操作指令寻址和块拷贝Load/Store指令之间的对应关系见教材P46的表3-10。3、答:见教材P46的3.5节的“1.协处理器加载/存储指令的寻址方式”的内容。4、答:(1)MOVR0,R1Cond00IopcodeSRn(R0)Rd(R0)operand2(R1)11100001101000000000000000000001(2)MOVR1,#0x198Cond00IopcodeSRn(R0)Rd(R0)operand2111000111010000000001111011001100x198:000110011000111101100110(3)ADDEQSR1,R2,#0xABCond00IopcodeSRn(R2)Rd(R1)operand200000010100100100001000010101011(4)CMPR2,#OxabCond00IopcodeSRn(R2)0000operand211100011010000100000000010101011(5)LDRR0,[R1,#4]Cond01IPU0WLRnRdaddressing_mode11100101100100010000000000000100(6)STRRO,[R1,R1,LSL,#2]!Cond01IPU0WLRnRdaddressing_mode11100111101000010000000100000001(7)LDRHR0,[R1,#4]Cond000PUIWLRnRdoffset_H1SH1offset_L11100001110100010000000010110100(8)LDRSBR0,[R2,#-2]!Cond000PUIWLRnRdoffset_H1SH1offset_L11100001011100100000000011010010(9)STRBR1,[R2,#0xA0]Cond01IPU1WLRnRdaddressing_mode11100101110000100001000010100000(10)LDMIAR0,{R1,R2,R8}Cond100PU0WLRnregister_list11101000100100000000000100000110(11)STMDBR0!,{R1-R5,R10,R11}Cond100PU0WLRnregister_list11101001001000000000110000111110(12)STMEDSP!,{R0-R3,LR}Cond100PU0WLRnregister_list11101000001011010100000000001111

第一章ARM指令集系统思考与练习题答案:1、答:ARM指令可以分为:数据处理指令、分支指令、加载/存储指令、批量加载/存储指令、交换指令、程序状态寄存器处理指令、协处理器操作指令和异常产生指令八类。无条件执行的指令有:由程序标号给出目标地址的跳转指令BLX、断点中断指令BKPT。2、答:(1)两个64位数的加法操作:R1和R0中存放了一个64位数据(作为被加数),R0存放数据的低32位;R2和R3中存放了另一个64位数据(作为加数),R2中存放低32位数据。运算结果送回到[R1:R0]中(R0存放低32位)。ADDSR0,R0,R2;低32位相加并影响标志位ADCR1,R1,R3;高32位相加再加上C标志位(进位值)(2)两个64位数的减法操作:使用SBC指令和SUBS指令联合使用可以实现两个64位操作数相减。如果R1和R0中存放了一个64位数据(作为被减数),R0存放数据的低32位;R2和R3中存放了另一个64位数据(作为减数),R2中存放低32位数据。运算结果送回到[R1:R0]中(R0存放低32位)。SUBSR0,R0,R2;低32位相减并影响标志位SBCR1,R1,R3;高32位相减再减去C标志位的反码(3)求一个64位数的负数操作:如果R1和R0中存放了一个64位数据,R0存放数据的低32位;寄存器R4和R5中放置其负数,其中R4放置低32位的数据。RSBSR4,R0,#0;0减去低32位并影响标志位RSCR5,R1,#0;0减去高32位再减去C标志位的反码3、答:LDRB指令的二进制编码格式为:Cond01IPU1WLRnRdaddressing_modeLDRSB指令的二进制编码格式为:Cond000PUIWLRnRdadrr_mode1SH1adrr_mode它们之间的区别是:LDRB指令和LDRSB指令编码格式中内存地址构成格式不一样;在功能上LDRB指令所加载的寄存器高24位清0,而LDRSB指令则用符号位扩展。4、答:CMPR0,#0语句功能:判断R0是否等于0并影响标志位;MOVEQR1,#0语句功能:当R0等于0时,MOVEQ指令执行,则R1等于0;MOVGTR1,#1语句功能:当R0等于正数时,MOVGT指令执行,则R1等于1。此程序段所实现的操作是:判别R0中的值是正数还是0。5、答:(1)MVNR0,#0(2)MOVR0,#0SUBR0,R0,#1(3)MOVR0,#0xFFFFFFFF6、答:(1)MOVR0,0x10(2)MOVR0,R1,ASR#4(3)ADDR1,R2,R2LSL#1(4)RSBR0,R0,#0

1、答:/*************************************************************寄存器使用说明:*R0:队列指针*R1:加载队列中的数据*R4:队列数据的累加结果*************************************************************/.globalstart.textstart:LDRR0,=DataZone@初始化队列起始地址;MOVR4,#0@结果寄存器初始化为0;AddNum:LDRBR1,[R0],#1@加载队列中的数据到R1寄存器;CMPR1,#0@判断R1的值是否为0;BLXstop@如果R1的值小于或等于0则停止累加;ADDR4,R4,R1@累加求和;BAddNum@继续循环;stop:BstopDataZone:.space10,0x10@在存储单元中申请10个字节的连续空间并用0x10填充;.zero5@在存储单元中申请5个字节的连续空间并用0填充;.end2、答:(1)MOVEQR0,R1(2)LDREQR0,[R1,R2](3)LDRR0,[R1,#-4](4)LDRR0,[R1,R6]!3、答:(1)将存储器地址为R3-4的字数据读入R2,并将地址R3-4写入到R3;(2)将存储器地址为R0的字数据读入R0,并将地址R0+R2写入到R0;(3)将存储器地址为R3+R2*4的字数据读入R1,并将地址R3+R2*4写入R3;(4)将存储器地址为R2-2的字节数据读入R0的低8位,将R0的高24位用符号位扩展,并将地址R2-2写入R2;(5)将R1的低8位存入存储器地址为R2+0xA0的字节中;(6)将内存单元R0所指向的地址单元以字为单位后增的方式读取到R1,R2,R8中,低地址编号的字数据内存单元对应低编号的寄存器;(7)将R1-R5,R10,R11以先减的方式存储到以R0为起始地址的递减内存中,R0最终指向存放R11的地址单元。4、答:ARM指令支持原子操作,主要是用来对信号量的操作,因为信号量操作的要求是做原子操作,即在一条指令中完成信号量的读取和修改操作。SWP数据交换指令就能完成此功能,能在一条指令中实现存储器和寄存器之间交换数据。5、答:在进入IRQ中断处理程序时,首先计算返回地址,并保存相关的寄存器:SUBR14,R14,#4STMFDSP!,{R0-R3,R12,LR}如果IRQ中断处理程序返回到被中断的进程则执行下面的指令:

LDMFDSP!,{R0-R3,R12,PC}∧该指令从数据栈中恢复寄存器R0-R3和R12的值,将返回地址返回到PC中,并将SPSR_irq值复制到CPSR中。1、答:.equUser_Mode,0x10.equMode_Mask,0x1F.equNOINT,0XC0MRSR0,CPSR@读取CPSRBICR0,R0,#Mode_MaskORRR1,R0,User_Mode|NOINT@修改MSRCPSR_cxsf,R1@写回CPSR,进入用户模式第一章Thumb指令思考与练习题答案:1.答:优势:Thumb指令集具有较高的代码密度,较低的存储器功耗。2.答:Thumb指令可以分为:数据处理指令、存储器操作指令、分支指令和软中断指令。Thumb指令有条件执行指令,它是条件分支指令B{cond}label。3.答:4.答:方法一:MOVR1,#0xAMULR0,R1方法二:'

您可能关注的文档

- vf习题答案.doc

- vf练习答案.doc

- Foxpro_实用教程课本及辅导教材参考答案第三版(新).doc

- Word操作练习题(解析和答案).doc

- xml习题1答案(南信大专用).doc

- XML基础教程课后习题解答.doc

- x《初级会计电算化》习题六(含答案解析).doc

- zhujiao054+《民事诉讼法学》习题答案.doc

- [高中政治]《经济生活》第1单元考点练习题[含参考答案].doc

- 《ASPNET动态网站开发教程(第三版)》各章习题参考答案.doc

- 《AutoCAD简明教程》第2版-习题答案.doc

- 《C++程序设计教程 第2版》教学素材习题04答案.doc

- 《C程序设计》课后习题答案(4-6章).doc

- 《C程序设计》课后习题答案(第8章).doc

- 《C语言》期末考试模拟复习题一(含答案).doc

- 《C语言程序设计(何钦铭 颜晖 主编)》习题8答案.doc

- 《C语言程序设计》第6章习题答案.doc

- 《C语言程序设计案例教程》练习题答案.docx

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明