- 897.26 KB

- 2022-04-22 11:27:39 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'思考与习题参考答案

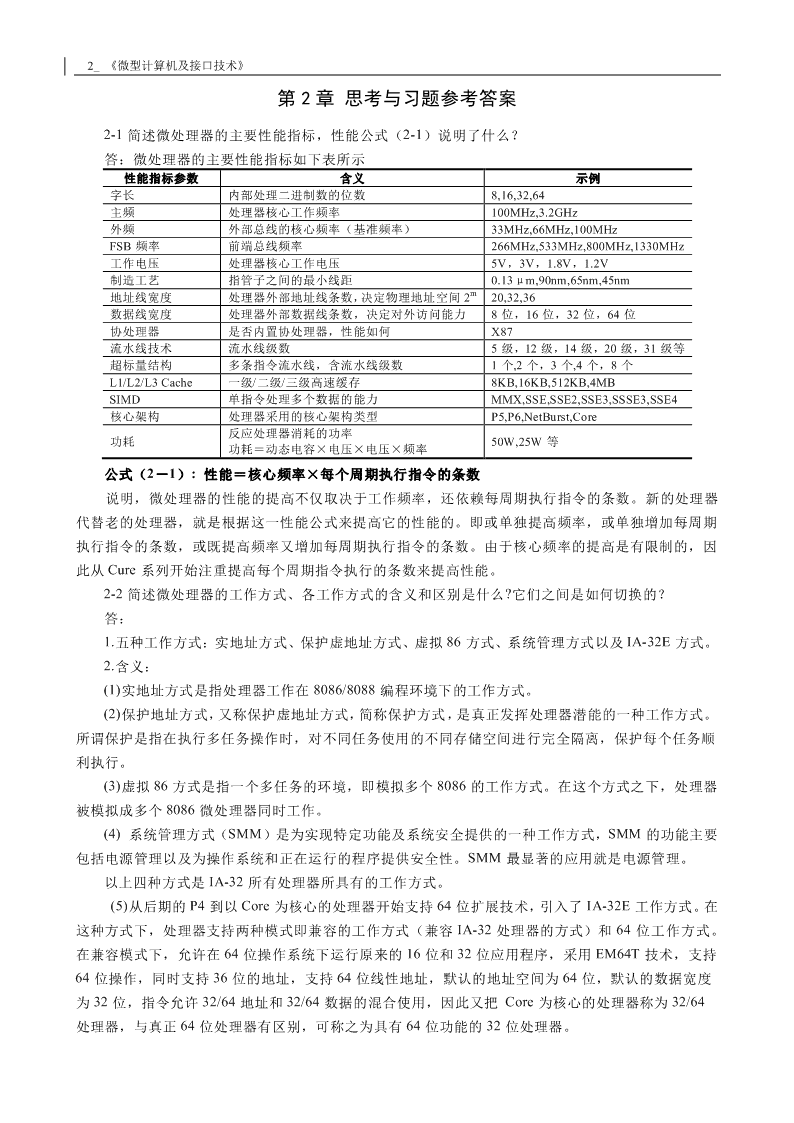

2《微型计算机及接口技术》第2章思考与习题参考答案2-1简述微处理器的主要性能指标,性能公式(2-1)说明了什么?答:微处理器的主要性能指标如下表所示性能指标参数含义示例字长内部处理二进制数的位数8,16,32,64主频处理器核心工作频率100MHz,3.2GHz外频外部总线的核心频率(基准频率)33MHz,66MHz,100MHzFSB频率前端总线频率266MHz,533MHz,800MHz,1330MHz工作电压处理器核心工作电压5V,3V,1.8V,1.2V制造工艺指管子之间的最小线距0.13μm,90nm,65nm,45nmm地址线宽度处理器外部地址线条数,决定物理地址空间220,32,36数据线宽度处理器外部数据线条数,决定对外访问能力8位,16位,32位,64位协处理器是否内置协处理器,性能如何X87流水线技术流水线级数5级,12级,14级,20级,31级等超标量结构多条指令流水线,含流水线级数1个,2个,3个,4个,8个L1/L2/L3Cache一级/二级/三级高速缓存8KB,16KB,512KB,4MBSIMD单指令处理多个数据的能力MMX,SSE,SSE2,SSE3,SSSE3,SSE4核心架构处理器采用的核心架构类型P5,P6,NetBurst,Core反应处理器消耗的功率功耗50W,25W等功耗=动态电容×电压×电压×频率公式(2-1):性能=核心频率×每个周期执行指令的条数说明,微处理器的性能的提高不仅取决于工作频率,还依赖每周期执行指令的条数。新的处理器代替老的处理器,就是根据这一性能公式来提高它的性能的。即或单独提高频率,或单独增加每周期执行指令的条数,或既提高频率又增加每周期执行指令的条数。由于核心频率的提高是有限制的,因此从Cure系列开始注重提高每个周期指令执行的条数来提高性能。2-2简述微处理器的工作方式、各工作方式的含义和区别是什么?它们之间是如何切换的?答:1.五种工作方式:实地址方式、保护虚地址方式、虚拟86方式、系统管理方式以及IA-32E方式。2.含义:(1)实地址方式是指处理器工作在8086/8088编程环境下的工作方式。(2)保护地址方式,又称保护虚地址方式,简称保护方式,是真正发挥处理器潜能的一种工作方式。所谓保护是指在执行多任务操作时,对不同任务使用的不同存储空间进行完全隔离,保护每个任务顺利执行。(3)虚拟86方式是指一个多任务的环境,即模拟多个8086的工作方式。在这个方式之下,处理器被模拟成多个8086微处理器同时工作。(4)系统管理方式(SMM)是为实现特定功能及系统安全提供的一种工作方式,SMM的功能主要包括电源管理以及为操作系统和正在运行的程序提供安全性。SMM最显著的应用就是电源管理。以上四种方式是IA-32所有处理器所具有的工作方式。(5)从后期的P4到以Core为核心的处理器开始支持64位扩展技术,引入了IA-32E工作方式。在这种方式下,处理器支持两种模式即兼容的工作方式(兼容IA-32处理器的方式)和64位工作方式。在兼容模式下,允许在64位操作系统下运行原来的16位和32位应用程序,采用EM64T技术,支持64位操作,同时支持36位的地址,支持64位线性地址,默认的地址空间为64位,默认的数据宽度为32位,指令允许32/64地址和32/64数据的混合使用,因此又把Core为核心的处理器称为32/64处理器,与真正64位处理器有区别,可称之为具有64位功能的32位处理器。

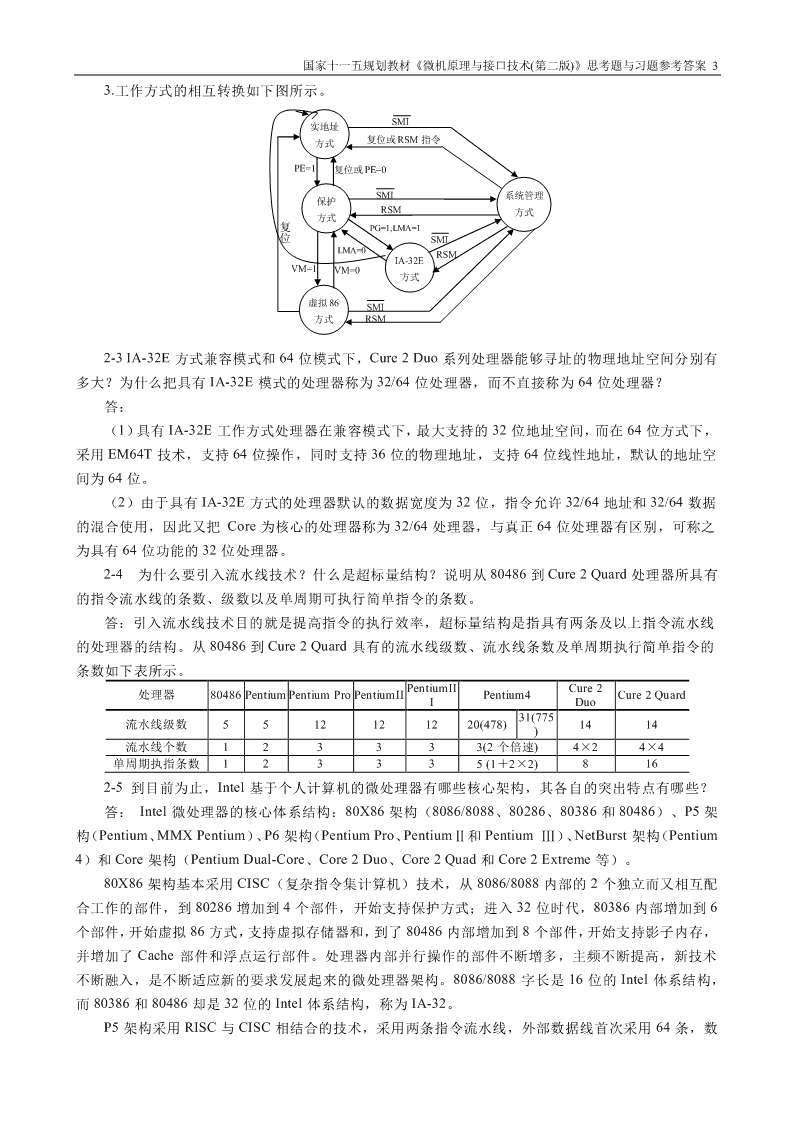

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案33.工作方式的相互转换如下图所示。SMI实地址复位或RSM指令方式PE=1复位或PE=0SMI系统管理保护RSM方式方式复PG=1,LMA=1位SMILMA=0RSMIA-32EVM=1VM=0方式虚拟86SMI方式RSM2-3IA-32E方式兼容模式和64位模式下,Cure2Duo系列处理器能够寻址的物理地址空间分别有多大?为什么把具有IA-32E模式的处理器称为32/64位处理器,而不直接称为64位处理器?答:(1)具有IA-32E工作方式处理器在兼容模式下,最大支持的32位地址空间,而在64位方式下,采用EM64T技术,支持64位操作,同时支持36位的物理地址,支持64位线性地址,默认的地址空间为64位。(2)由于具有IA-32E方式的处理器默认的数据宽度为32位,指令允许32/64地址和32/64数据的混合使用,因此又把Core为核心的处理器称为32/64处理器,与真正64位处理器有区别,可称之为具有64位功能的32位处理器。2-4为什么要引入流水线技术?什么是超标量结构?说明从80486到Cure2Quard处理器所具有的指令流水线的条数、级数以及单周期可执行简单指令的条数。答:引入流水线技术目的就是提高指令的执行效率,超标量结构是指具有两条及以上指令流水线的处理器的结构。从80486到Cure2Quard具有的流水线级数、流水线条数及单周期执行简单指令的条数如下表所示。PentiumIICure2处理器80486PentiumPentiumProPentiumIIPentium4Cure2QuardIDuo31(775流水线级数5512121220(478)1414)流水线个数123333(2个倍速)4×24×4单周期执指条数123335(1+2×2)8162-5到目前为止,Intel基于个人计算机的微处理器有哪些核心架构,其各自的突出特点有哪些?答:Intel微处理器的核心体系结构:80X86架构(8086/8088、80286、80386和80486)、P5架构(Pentium、MMXPentium)、P6架构(PentiumPro、PentiumⅡ和PentiumⅢ)、NetBurst架构(Pentium4)和Core架构(PentiumDual-Core、Core2Duo、Core2Quad和Core2Extreme等)。80X86架构基本采用CISC(复杂指令集计算机)技术,从8086/8088内部的2个独立而又相互配合工作的部件,到80286增加到4个部件,开始支持保护方式;进入32位时代,80386内部增加到6个部件,开始虚拟86方式,支持虚拟存储器和,到了80486内部增加到8个部件,开始支持影子内存,并增加了Cache部件和浮点运行部件。处理器内部并行操作的部件不断增多,主频不断提高,新技术不断融入,是不断适应新的要求发展起来的微处理器架构。8086/8088字长是16位的Intel体系结构,而80386和80486却是32位的Intel体系结构,称为IA-32。P5架构采用RISC与CISC相结合的技术,采用两条指令流水线,外部数据线首次采用64条,数

4《微型计算机及接口技术》据Cache和指令Cache开始分离,首次采用分支指令预测功能,使效率大大提高。P6架构采用三条指令流水线,Cache扩大,并引入二级Cache,大大地加快了数据读取和命中率,提高了性能,支持多媒体扩展技术MMX。NetBurst架构首次采用快速执行引擎,使简单ALU速度加倍,采用超级流水线技术(20级,31级),先进的动态执行,创新的Cache子系统(TraceCache上),超标量发射以实现并行性,扩充的可重命名的硬件寄存器,支持更新的多媒体扩展指令等。Core微架构拥有双核心、64位指令集、4发射的超标量体系结构(核心特点)和乱序执行机制等技术,支持36位的物理寻址,支持Intel所有的扩展指令集。Core微架构的每个内核拥有L1指令Cache、双端口L1数据Cache,2个内核共同拥有共享式二级缓存。Core架构采用了每条超级指令流水线14级,其流水线效率大幅度提升。全新的整数与浮点单元,Core具备了3个64位的整数执行单元,每一个都可以单独完成的64位整数运算操作,即Core能够在一个周期内同时完成3组64位的整数运算。2-68086/8088微处理器由哪两个关键部分组成,其功能主要包括哪些?说明二者是如何配合工作的。答:(1)组成:8086/8088由两个既相互独立,又相互配合,并行操作的重要部件组成总线接口部件BIU和执行部件EU组成。(2)总线接口部件BIU的功能:负责微处理器内部与外部(存储器和I/O接口)的信息传递。BIU完成的主要任务包括:取指令、传送数据以及计算物理地址;执行部件EU的功能:主要功能简单地说就是执行全部指令。EU完成以下几个主要任务:指令译码、执行指令、向BIU传送地址信息以及管理通用寄存器和标志寄存器。(3)配合工作:只要指令队列不满,则BIU就去取指令,只要指令队列有指令,EU就执行指令,二者同时进行。EU向BIU指供地址信息,BIU计算物理地址,并指向目标地址并取数据或指令或送数据到目标地址,而EU负责运算和处理。BIU和EU既相互独立又相互配置并行流水作业。2-780286由哪几个主要部件组成?各自的功能是什么?与8086有什么不同?答:1.组成:80286微处理器内部共有四个功能部件:地址部件AU、总线部件BU、指令部件IU和执行部件EU。2.功能:(1)总线部件BU负责内外信息交换;(2)指令部件IU负责从预取队列中取代码并进行译码,然后放入3条指令的指令队列中;(3)地址部件AU负责物理地址的生成;(4)执行的EU负责指令的执行。3.与8086的不同点:(1)地址线条数不同,因此寻址空间不一样(8086:20条寻址1MB,8028624条寻址16MB)(2)内部结构不同,比8086多了两个部件,同时多了一个指令队列(已译码的指令队列)(3)速度提高(8086:5MHz,80286:16MHz)(4)多了一种工作方式,支持多任务中,虚拟内存,寻址方式不同2-880386与80286相比内部由几个主要部件组成?各部件的功能是什么?答:1.组成:6个部件:总线部件BU、指令预取部件IPU、指令译码部件IDU、执行部件EU、分段部件SU和分页部件PU。2.功能:(1)总线部件BU:提供与外部(存储器以及I/O)的接口环境(地址线、数据线和控制线的驱动等)。在80386内部,指令预取部件要从存储器中取指令、执行部件在执行指令时要访问存储器或I/O,

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案5分页部件形成物理地址后,都要发出总线周期的请求,BU会根据优先级对这些请求进行仲裁,从而有序地服务于多个请求,并产生相应的总线操作所需要的信号,包括地址信号、读/写控制信号等。BU还提供了与协处理器如80387或80287的接口。(2)指令预取部件IPU通过BU按顺序向存储器取指令并放到16个字节的预取指令队中,为指令译码部件提供有效的指令。(3)指令译码部件IDU从预取指令队列中取出原代码后进行译码,并将译码好的指令存放在3条指令的队列中,送给执行部件。(4)执行部件EU包括ALU以及64位的桶形移位寄存器和8个32位的通用寄存器及保护检测电路等,EU从IDU中取出已译码的指令后,立即通过控制电路产生各种控制信号送到内部各个部件,从而执行了该指令。在执行指令的过程中,向分段部件发出逻辑地址信息,并通过BU与外部交换数据。(5)分段部件SU将EU送来的两路32位有效地址(包括逻辑地址48位:16位选择子和32位段内偏移地址)通过描述符的数据结构形成32位的线性地址。(6)分页部件PU接收到线性地址后,通过两次页转换将其变换为实际的32位物理地址。2-9简述P5架构的Pentium处理器的结构特点。答:(1)与80X86系列微处理器兼容(2)RISC型超标量结构:两条指令流水线(U+V)(3)高性能的浮点运算器(4)双重分离式高速缓存:将指令高速缓存与数据高速缓存分离,各自拥有独立的8KB高速缓存,使其能全速执行,减少等待及传送数据时间。(5)增强了错误检测与报告功能:内部增强了错误检测与报告功能,特别引进了在片功能冗余检测(FRC),并采用了一种能降低出错的六晶体管存储单元。(6)64位数据总线:使用64位的数据总线(80386/80486为32位)。(7)分支指令预测:处理器内部采用了分支预测的技术,大大提高了流水线执行效率。(8)常用指令固化及微代码改进(9)系统管理方式:在实地址方式、保护方式、虚拟86方式的基础上,增加了SMM(系统管理方式)。2-10Pentium处理器的U和V两条指令流水线的功能是什么?主频为100MHz的Pentium处理器,最快执行两条指令的时间为多少ns?答:(1)U流水线主要用于执行复杂指令,而V流水线只能执行简单指令。(2)最快执行两条指令的时间是一个时钟周期,100MHz主频其一个时钟周期为1/100(us)=10ns。2-11简述Pentium处理器的BTB的功能。答:BTB(分支目标缓冲器)可对分支指令进行预测,目的是提高流水线执行效率。在Pentium微处理器中,使用了BTB预测分支指令,这样可在分支指令进入指令流水线之前预先安排指令的顺序,而不致使指令流水线的执行产生停滞或混乱。2-12简述P6架构的处理器的主要特点,基于该架构的PentiumII和PentiumIII特点如何?答:1.架构的主要特点如下:(1)三条超标量指令流水线,每条12级超流水线(细分也可认为14级),使一个时钟周期内可同时执行三条简单指令。(2)5个并行处理单元:两个整数运算部件,一个装入,一个存储,1个浮点运算部件(FPU)。

6《微型计算机及接口技术》(3)8KB两路相关指令高速缓存,8KB四路相关数据高速缓存。(4)专用全速总线上的二级高速缓存与微处理器紧密相联。(5)事务处理I/O总线和非封锁高速缓存分级结构。(6)错序执行,动态分支预测和推理执行。2.PentiumII处理器的显著特点有:(1)双重独立总线(DIB)体系结构能同时使用具有纠错功能的64位系统总线和具有可选纠错功能的64位Cache总线。(2)多重跳转分支预测通过多条分支预测程序执行,加快了工作向处理器的流动。(3)数据流分析分析并重排指令,使指令以优化的顺序执行,与原始程序的顺序无关。(4)指令推测执行通过预先查看程序计数器PC并执行那些将要执行的指令,提高了速率。(5)采用IntelMMX技术包括了57条增强的MMX指令技术,可处理视频、声频及图像数据。PenitumⅢ与PentiumⅡ相比,主要参数特点如下:(1)主频450MH以上到1.1GHz(2)总线频率100MHz/133MHz(3)新增加70条SSE指令(4)2.0V供电,0.25到0.18微米工艺制造(5)32KB的L1以主频速度工作,512KB的L2以主频一半速度工作2-15Pentium4处理器,一个时钟周期内可执行多少条简单?如果3.0GHz的Pentium4执行9条简单指令,最快需要多长时间执行完?答:P4内部有一个复杂指令流水线和两个快速流水线,快速流水线倍速工作,因此每个时钟可执行5条简单指令。3GHz对应的周期为1/3ns,9*1/3=3ns即9条指令最短可在3ns内执行完毕。2-17一个典型的Cure2Duo处理器一个时钟可以执行多少条简单指令?2.0GHz的Cure2Duo处理器在1ns内最快能执行多少条简单指令?答:由于Cure2Duo是典型的双核处理器,每个内核有4个译码器和相关执行单元,即有4条指令流水线,因此,单一时钟可执行简单指令4×2=8条;时钟频率2GHz即时钟周期为0.5ns,即要0.5ns内可执行简单指令8条,1ns/0.5ns×8=16条,即2GHz的Cure2Duo可在1ns内指行16条简单指令。2-18总结一下8086/8088到Cure2Duo处理器外部地址线、数据线条数、通用寄存器的位数以及所处的工作方式。各自的位长以及所能寻址的物理地址空间有多大?答:从8086到Cure2Duo的相关参数如下表所示表。

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案7处理器PentiumCore2DuoCore2QuadCore2Extreme80868088802868038680486PentiumPentiumProPentiumIIPentiumIIIPentium4主要参数MMX(双核)(四核)(至尊)通用寄存器位数161616323232323232323232/6432/6432/64即位长外部数据线条数168163232646464646464646464外部地址线条数2020243232323632363636363636实,保护、实、保护、实、保护、实、保护、实、保护、实、保护、实、保护、V86、实、保护、实方式实方式实方式实、保护、V86、系工作方式实方式实方式V86、系统管V86、系统管V86系统管V86系统管V86、系统管V86、系统管系统管理、V86、系统管保护方式保护V86保护、V86统管理、IA-32E理理理理理理、超线程IA-32E理、IA-32E2-20通过复位后寄存器的特点,说明各处理器复位后程序第一条指令存放的地址。答:复位后16位处理器8086/8088以及80286系统复位后内部除CS=FFFFH外,其余各寄存器全为0,段的起始地址为段寄存器的内容左移4位,因此复位后第一条指令的地址FFFF0H(CS×16+IP)。IA-32处理器复位后内部地址相关寄存器的状态为:EIP=0000FFF0H,CS=F000H,CS.BASE(代码段基地址)=FFFF0000H,SS=DS=ES=FS=GS=0000H,其它段的段基地址均为0,GDTR=00000000FFFFH,IDTR=00000000FFFFH。即GDTR和IDTR描述的基地址全为0,界限均为FFFFH。LDTR=0,对应的基地址为0,界限为FFFFH,IA-32处理器复位后的第一条指令的地址为=段基地址+偏移地址=FFFF0000+FFF0H=FFFFFFF0H。即8086~80286复位地址FFFF0H,80386~Cure2Duo复位地址为FFFFFFF0H。2-22IA-32处理器的CR0、CR2、CR3和CR4的名称及功能是什么?CR0中与寻址有关的控制位有哪些?CR4中对于具有36条地址线的处理器有哪里相关控制位?答:(1)控制寄存器名称及功能如下表所示标识名称功能CR0机器状态寄存器存放处理器的状态和控制位,决定处理器的工作模式保存着发生页故障,产生异常中断之前所访问的最后一个页的线性地CR2页故障地址寄存器址。CR3页目录表基址寄存器保存着页目录表的物理基地址及两个属性包括了几个结构的扩展并指示对特殊处理器性能的支持,36位物理地CR4扩展控制寄存器CR4(从Pentium开始)址及不同而大小的支持等(2)CR0与寻址有关的主要控制位有CR0.0(PE)保护允许,CR0.31(PG)分页允许CR4中与36位地址相关的控制位有:CR4.5(PAE)页地址扩展,对于基于36位地址的处理器,PAE=1允许使用36位地址,访问64GB的存储空间,PAE=0只有访问使用32位地址线,寻址4GB;CR4.7(PGE)页全局允许,针对基于36条地址线的处理器(P6开始引入)的页全局允许,PGE=1允许全局页特征,PGE=0禁止全局页特征;2-26已经从内存1FF00000开始存放12H,34H,56H,78H,90H,ABH,CDH,EFH,11H,22H,33H,44H,55H,66H,77H,88H,99H,00H,AAH,BBH,CCH,DDH,EEH,FFH,试说明从1FF00000H开始取一个双四字的值,从1FF00008H开始取双字的值,以及从1F00010H开始取四字和一个字的值。解:从1FF00000H开始的双四字的值=8877665544332211EFCDAB9078563412H从1FF00008H开始的双字的值=44332211H

8《微型计算机及接口技术》从1FF00010H开始的四字的值=FFEEDDCCBBAA0099H从1FF00010H开始的一个字的值=0099H2-28对于8086最小模式填写下列表格DT/RM/IORDWR对应的操作指令示例0001读I/O接口INAL,DX0101读存储器MOVAL,[SI]1010写I/O接口OUTDX,AL1110写存储器MOV[DI],AL2-298086/8088的外部时钟接5MHz,试问在RESET引脚需要多少uS时间的高电平,系统才能复位,复位后8086/8088内部的状态如何?在读内存时如果需要插入2个等待周期,这2个等待周期的位置如何?如果该内存单元54300H中的数据为3AH,54301H中的数据为B6H,读内存这一个字需要多少uS的时间?试画出读取由54300H开始一个字的时序图。答:(1)8086/8088需要至少4个时钟周期才可复位,每个时钟周期为1/5us,因此在RESET引脚需4×1/5=0.8us的时间才能复位,复位后除CS=FFFFH外,其它寄存器全为0,指令队列也清除(2)插入的等待周期在T3和T4之间(3)读内存在插入2个等待周期时需要4+2=6个时钟周期的时间即6×0.2=1.2us物理地址=54300H,高4位地址为5(0101B),低16位地址为4300H,数据B63AH,因此对应读时序如图所示。CLKT1T2T3TwTwT4M/IOA19~A1656AD15~A04300HB63AHBHE/S7ALERDDT/RDEN2-30对于80386~Pentium处理器,填写下表。M/IOW/RD/C操作类型指令示例001读I/OINAX,DX011写I/OOUTDX,AX100读存储器代码无101读存储器数据MOVAX,[SI]111写存储器数据MOV[DI],AX2-35对于IA-32或Intel64处理器采用16位运算(用16位寄存器),求以下运算结果及相应各标志位:(1)5439H+4567H(2)2345H+5219H(3)54E3H-27A0H(4)1A9FH+E561H

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案9解:(1)5439H+4567H=99A0H0101010000111001+01000101011001111001100110100000AF=1,PE=1,ZF=0,CF=0,OF=1,SF=1(2)2345H+5219H=755EH0010001101000101+01010010000110010111010101011110AF=0,PE=1,ZF=0,CF=0,OF=0,SF=0(3)法1直接相减54E3H-27A0H=2D43H0101010011100011-00100111101000000010110101000011AF=0,PE=0,ZF=0,CF=0,OF=0,SF=0法2变减为加54E3H-27A0H=54E3+D860H=2D43H0101010011100011+110110000110000010010110101000011AF=0,PE=0,ZF=0,CF=1,OF=0,SF=0(4)1A9FH+E561=0000H0001101010011111+111001010110000110000000000000000AF=1,PE=1,ZF=1,CF=1,OF=0,SF=02-368086/8088,80386,80486,Pentium,PentiumPro,PentiumII,PentiumIII,Pentium4,Cure2内部通用寄存器的位数、段寄存器的位数、外部地址线和数据线的条数分别为多少?求其寻址范围及带符号数表示范围。答:相应参数见下表所示。

10《微型计算机及接口技术》处理器Core2DuoCore2QuadCore2Extreme8086、80888038680486PentiumPentiumProPentiumIIPentiumIIIPentium4主要参数(双核)(四核)(至尊)通用寄存器位数即位163232323232323232/6432/6432/64长段寄存器位数1616161616161616161616外部数据线条数1632326464646464646464外部地址线条数2032323236363636363636寻址范围0-FFFFFH00000000H-FFFFFFFFH000000000H-FFFFFFFFFH3131-2~2-115153131有符号数表示的范围-2~2-1-2~2-16363支持-2~2-12-40简述段基址、偏移地址、逻辑地址和物理地址的含义及其相互关系。答:段基址是该段物理地址的起始地址或首地址,偏移地址指的是离段基的偏移量,将存放在段寄存器中的内容与偏移地址合称为逻辑地址,通常用段寄存器内容:偏移地址表示逻辑地址。在实地址方式下,逻辑地址包含了段地址(20位段起始物理地址的高16位)和偏移地址,在保护方式下逻辑地址包含了段选择子(决定起始物理地址存放位置)和偏移地址。物理地址可由逻辑地址来决定,物理地址=段基址+偏移地址。只是段基址在不同模式下的求法不同。2-43内存数据如下表所示,指出实地址方式下,执行下列程序段后AX中的值。MOVAX,1100HMOVDS,AXMOVBX,200HMOVAX,[BX+62H]表2.26题2-43和2-50表(内存数据分布情况)地址数据地址数据地址数据::::::00011267H00H00011237H00H00001007H00H00011266H70H00011236H01H00001006H40H00011265H00H00011235H11H00001005HF2H00011264H01H00011234H47H00001004H01H00011263H75H00011233H32H00001003H00H00011262H39H00011232H30H00001002H00H00011261H2AH00011231H30H00001001H1FH00011260H00H00011230H39H00001000HFFH解:从程序段知DS=1100H,有效地址=200H+62H=262H,因此物理地址=11000H+262H=11262H,11262H开始的一个字为7539H,所以AX=7539H2-45IA-32处理器在实地址方式下各寄存器的值如下,求当前的存储单元地址。(偏移量在EAX、ECX、ESP、ESI和EDI中)(1)DS=2000H,EAX=00003000H(2)DS=1A00,ESI=00002000H(3)SS=C000H,ESP=0000A000H(4)DS=1239H,EDI=0000A000H解:(1)物理地址=DS×16+EAX=20000H+00003000H=00023000H(2)物理地址=DS×16+ESI=1A000H+00002000H=0001C000H(3)物理地址=SS×16+ESP=C0000H+0000A000H=000CA000H(4)物理地址=DS×16+ESI=12390H+0000A000H=00001C390H2-46试定义IA-32处理器的两个段描述符来描述一个存储器段,均为一个可写、向上增长的用户访问的在物理存储器中、未访问过的数据段,(1)地址范围为03000000H~03001FFFH,(2)01000000H~027FFFFFH。

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案11解:(1)定义段描述符就是确定段基址、段界和相关属性段基址=03000000H,段界=末地址-首地址=1FFFH,属性G=0,D=1,AVL=0,访问权字节,P=1,DPL=11,S=1,TYPE=001,A=0,对照描述符格式31…………………242322212019……16151413121110987………………0基地址段基址(B31-B24)GD/B0AVL段界(L19-L16)PDPLSTypeA4(B23-B16)基地址(B15-B0)段界(L15-L0)0所以段描述符为:0341F20000001FFFH(2)段基址=01000000H,段大小=027FFFFFH-01000000H+1=017FFFFFH=01800000H>FFFFFH+1因此,G=1,由于段大小=(段界+1)×4K,因此段界=段大小/4K-1=01800000H/4K-1=-180H-1=0017FH,其它属性同上,则段描述符=01C1F2000000017FH2-48已知从00100000H开始存放FFH,01H,00H,04H,10H,F2H,0AH,06H,FFH,03H,00H,00H,10H,F2H,40H,02H,从02100000H开始存放35H,36H,31H,30H,30H,32H,39H,38H,3AH,DS=000BH,EBX=0000002H,GDTR=001000001FFFH,CR0=60000011H,CR3=00034000H,对于IA-32处理器,执行指令MOVEAX,[EBX]时:(1)求源操作数对应的描述符表可存放描述符个数(2)求源操作数对应段描述符的值以及该描述符描述段的地址范围(3)求源操作数所对应的物理地址(4)求指令执行后EAX中的内容。(5)从已知条件中还能得到什么信息?解:DS=000BH=0000000000001011B,对照选择子的格式可知TI=0,选中GDT表,RPL=11为普通用户使用,索引×8=08H13(1)GDT表可存放的描述符的个数由索引决定,由于索引共有13位,因此可寻找2=8K个描述符;(2)先找出描述符存放的首地址=GDT表首址(GDTR高32位)+索引×8=00100000H+08H=00100008H,以段描述符为0240F210000003FFH,描述符描述的段的大小取决于段界和G,对照段描述符的格式可知G=0,段界=003FFH,段基址=02100000H,因此段地址范围为02100000H~0210003FFH;(3)CR0=600000011H,因此PE=1,PG=0,是分段而不分页的保护方式,因此CR3多余,段内偏移地址=EBX的值=00000002H,因此物理地址=段基址+段内偏移地址=02100000H+00000002H=02100002H;(4)021000002H开始的4个字节就是EAX的值=39323031H;(5)由段描述符可知,G=0,D=1为32位数据,此外决定其它属性的主要是访问权字节,访问权字节中为F2H=11110010B,即P=1表示数据在物理存储器中,DPL=11表示一般用户程序访问的数据,S=1表示段描述符,A=0表示该段还没有被访问过,TYPE=001表示该段是向上增长的可写的数据段。2-49已知内存中的数据如表5.16所示,对于IA-32处理器,已知内部相应寄存器的值为:ESI=00001230H,DS=SS=ES=FS=GS=1003H。GDT表和LDT表的首地址均为0,CR4=0。内存数据如下所示。(1)当CR0=60000010H时指令MOVEAX,[ESI]对应源操作数的物理地址及指令执行后EAX中的值。

12《微型计算机及接口技术》(2)当CR0=60000011H时求指令MOVEAX,[ESI]对应源操作数的物理地址及指令执行后EAX中的值。该段的最多能容纳多少字节数据?根据访问权字节说明该段是什么样的段,是否存在存储器中?地址数据地址数据地址数据::::::00011267H00H00011007H00H00001007H00H00011266H70H00011006H01H00001006H40H00011265H00H00011005H11H00001005HF3H00011264H01H00011004H47H00001004H01H00011263H75H00011003H32H00001003H00H00011262H39H00011002H30H00001002H00H00011261H2AH00011001H30H00001001H1FH00011260H00H00011000H39H00001000HFFH解:CR4=0表示没有页的扩展,默认4KB页大小(1)由CR0=60000010H可知,PE=0,处于实地址方式,因此物理地址=段地址×16+偏移地址=10030H+00001230H=00011260H,由表可知执行完MOVEAX,[ESI]之后,EAX的值=75392A00H;(2)由CR0=60000011H知PE=1且PG=0为仅分段的保护方式,由DS=1003H=0001000000000011B,可知,TI=0选择的是GDT表,RPL=11表示一般用户访问,索引×8=1000H段描述符存放的首地址=GDT表首址+索引×8=00001000H,所以通过上表可知,段描述符=0040F30100001FFFH,段基址=00010000H,段界=01FFFH,G=0,段内偏移量=ESI=00001230H,因此物理地址=段基址+偏移地址=00010000H+00001230H=00011230H,由表可得执行MOVEAX,[ESI]后,EAX的值就是从00011230H开始的4个字节,即EAX=32303039H;由于G=0时段大小=段界+1=01FFFH+1=2000H=8192字节,即可容纳8192字节的数据访问权字节=F3H=11110011B,A=1该已经被访问过,同P=1在物理存储器中,是向上增长的可写的数据段。

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案13第5章思考与习题参考答案5-3说明SRAM、DRAM、MROM、PROM、EPROM及FRAM的特点及简单工作原理。答:SRAM靠双稳态触发器的两个稳定状态存储信息的;DRAM靠极间电容的充放电来存储信息的;MROM靠光刻技术确定是否保留MOS管决定信息的,跨接MOS管,信息为0,没有跨接MOS管,信息为1;PROM是靠熔丝的通断决定信息的,没有熔断,则信息为1,熔断信息为1;EPROM是靠雪崩注入式场效应管(FAMOS管)的浮置栅是否积累足够的电荷来存储信息的,有足够的电荷积累,则记录信息0,没有足够的电荷积累信息记录;FRAM是靠铁电电容来存储信息的。5-4已知一个SRAM芯片的容量为4M×8,该芯片有一个片选信号引脚和一个读/写控制引脚,问该芯片至少有多少个引脚?m解:SRAM的引脚的确定从地址线、数据线、控制线及电源线四方面考虑,地址线m决定字数,2=4M,因此m=22,容量4M×8,所以n=8,片选一条,读写控制一个,电源线2条,芯片共有引脚=22+8+1+1+2=34条。5-5已知一个DRAM芯片外部引脚信号中有4条数据线,11条地址线,则其容量最大有多大?2×11解:DRAM的容量=2×4=16M位。(注意地址线与单元数的关系与SRAM不同)5-650ns的512M×8的DRAM芯片,其外部数据线和地址线为多少条?1秒钟至少可存取多少次?如果总线速度为50MHz的微机系统,在访问存储器时要不要插入等待周期?29解:(1)寻址的地址线=log2(单元数)=log2(512M)=log2(2)=29条,由于DRAM的外部地址线是内部的一半,因9此DRAM的外部地址线为15条,数据线8条,1s/50ns=10/50=20000000次,即每秒可存取2千万次,总线速度为50MHz,即总线时钟周期为1/50MHz=0.02us=20ns,因此比50ns快,因此需要插入等待周期,要插入2个等待周期20ns+20ns*2=60ns,才能正常访问50ns的存储器。5-9试计算外频(内存模块的核心频率)为100MHz时DDR、DDR2、DDR3的带宽。解:由于DDR、DDR2和DDR3数据宽度为64位,100MHz下的速度如下:(1)DDR:100MHz×2×64/8=1600MB/s(2)DDR2:100MHz×4×64/8=3200MB/s(3)DDR3:100MHz×4×2×64/8=6400MB/s5-10已知RAM的容量为(1)16K×8(2)64K×8(3)128K×8(4)256K×8如果RAM的起始地址为3450H,则各RAM对应的末地址为多少?410解:(1)16K×8,单元数16K=2×2=3FFFH+1,所以末地址=首地址+大小-1=3450H+3FFFH=744FH16(2)64K=2=FFFFH+1,末地址=3450H+FFFFH=1344FH17(3)128K=2=1FFFFH+1,末地址=3450H+1FFFFH=2344FH18(4)256K=2=3FFFFH+1,末地址=3450H+3FFFFH=4344FH5-11如果一个应用系统中ROM为8KB,最后一个单元地址为57FFH,RAM紧接着ROM后面编址,RAM为16KB,求该系统中存储器的第一个地址和最后一个单元地址。13解:ROM最后一个单元为57FFH,8K=2=1FFFH+1,因此首地址=末地址-(大小-1)=57FFH-1FFFH=143800H,由于RAM紧跟ROM后面编址,因此RAM的首地址=57FFH+1=5800H,RAM大小16K=2=3FFFH+1,所以RAM的最后地址就是系统存储器的末地址(最后一个单元的地址)=5800H+3FFFH=97FFH

14《微型计算机及接口技术》5-12有一个存储体由SRAM构成,其地址线15条,数据线为8条,则NC128Vcc(1)该存储体能够存储多少个汉字?A12227A14A7326A13(2)如果该存储体由2K×4位的芯片组成,需要多少片?A6425A8(3)采用什么方法扩展?需多少根地址线选择这些芯片?A5524A9A4623A1115解:(1)SRAM容量=2×8=32KB,能存储汉字32KB/2=16K个=16384A3722OE/VPPA2821A10个A1920CEA01019D7(2)32K×8/(2K×4)=16×2=32片D01118D6(3)由于单元数和位数都有增加,因此采用字位全扩展方法,需要的地D11217D5D21316D4址线选择芯片取决于字数的增加,2K增加到32K,即分别选择的存储器模块GND1415D3有16个,因此需要4根额外的地址线来通过4-16译码器来选择,这16个8图5.42题5-15图位的存储器模块(每个模块8位,由两片2K×4构成)。5-16写出图5.43(a)所示的片选信号CS以及(b)中Y0~Y7对应的端口地址。(a)(b)图5.43题5-16图解:(a)由CS=0可知:A9=0,A8=0,A7=0,A6=1,A5=1,A4=1,A3=1,A2=1,A1=1,A0=1,地址=0001111111B=07FH;(b)由3-8译码器使能端有效即E3=1,E2=E1=0知:A9=1,A8=0,A7=0,A6=1,A5=0,A4=1,A3=0Y0:A2A1A0=000,因此Y0的地址=1001010000B=250HY1:A2A1A0=001,因此Y1的地址=1001010001B=251HY2:A2A1A0=010,因此Y2的地址=1001010010B=252HY3:A2A1A0=011,因此Y3的地址=1001010011B=253HY4:A2A1A0=100,因此Y4的地址=1001010100B=254HY5:A2A1A0=101,因此Y5的地址=1001010101B=255HY6:A2A1A0=110,因此Y6的地址=1001010110B=256HY7:A2A1A0=111,因此Y7的地址=1001010111B=257H5-17某系统的存储器配备两种芯片即32K×8的EPROM和32K×8的SRAM,采用74LS138译码器输出作片选信号。如图5.44所示。(1)确定每一片存储器芯片的地址范围(2)编程将4#的32KB数据传送到7#存储区域

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案15WRD7~D0RDOED7~D0OED7~D0OED7~D0EPROM27256(1#)27256(2#)27256(3#)74LS138CSA14~A0CSA14-A0CSA14~A0A19G1Y0A18G2AY1G2BM/IOY2Y3Y4A17CY5WED7~D0WED7~D0WED7~D0WED7~D0A16BA15AY662256(4#)62256(5#)62256(6#)62256(7#)CSA14~A0CSA14~A0CSA14~A0CSA14~A0A14~A0SRAM图5.44题5-17图解:(1)3-8译码器的使能端有效可知A19=1A18=01#:Y0:A17A16A15=000,A14~A0=0……0~1……1,地址范围:80000H~87FFFH2#:Y1:A17A16A15=001,A14~A0=0……0~1……1,地址范围:88000H~8FFFFH3#:Y2:A17A16A15=010,A14~A0=0……0~1……1,地址范围:90000H~97FFFH4#:Y3:A17A16A15=011,A14~A0=0……0~1……1,地址范围:98000H~9FFFFH5#:Y4:A17A16A15=100,A14~A0=0……0~1……1,地址范围:A0000H~A7FFFH6#:Y5:A17A16A15=101,A14~A0=0……0~1……1,地址范围:A8000H~AFFFFH7#:Y6:A17A16A15=110,A14~A0=0……0~1……1,地址范围:B0000H~B8FFFH(2)用串操作指令完成MOVAX,9000H;不仿设数据段地址9000HMOVDS,AXMOVSI,8000H;数据段段内偏移量起始地址8000HMOVAX,0B000H;设附加数据段地址B000HMOVES,AXMOVDI,0;附加数据段段内偏移量起始地址0CLD;在DF=0让地址增加MOVCX,32*1024;32KB大小数据传输REPMOVSB用普通数据传送指令完成MOVAX,9000H;不仿设数据段地址9000HMOVDS,AXMOVSI,8000H;数据段段内偏移量起始地址8000HMOVAX,0B000H;设附加数据段地址B000HMOVES,AXMOVDI,0;附加数据段段内偏移量起始地址0MOVCX,32*1024;32KB大小数据传输REPLP0:MOVAX,[SI]MOVES:[DI],AXINCSIINCDILOOPREPLP0

16《微型计算机及接口技术》5-21简述8088、8086、80386、Pentium、PentiumII、PentiumIII、Pentium4以及Cure2系统存储器的组成形式。解:8088为8位存储器组织,共一个8位存储体,总容量最大1MB;8086和80286为16位存储器组织,共2个8位存储体,1个偶地址存储体和1个奇地址存储体,其中8086的每个存储体最大512KB,共1MB,而80286每个8MB,共16MB;80386为32位存储器组成,共4个8位存储体,每个最大1MB,共4GB;Pentium~Cure2均为64位存储器组织,共8个8位存储体,Pentium每个存储体最大512MB,共4GB,PentiumII~Cure2每个最大8GB,共64GB。5-22简述内存的层次结构。解:内存有三个层次即Cache、主存储器和虚拟存储器,其中Cache容量小、最快、价格高,虚拟存储器最慢,容量大,价格低。5-23CMOS的功能是什么?如何对其操作?写出将年月日时分秒的值读出后存入1000H:2000H开始的内存区域的程序片段。解:CMOS主要包括实时钟及CMOSRAM,因此其主要功能有产生实时钟及保存设置和配置信息。对CMOS的操作分两个步骤:(1)向70H写CMOS地址;(2)对71H读或写数据MOVAX,1000HMOVDS,AXMOVDI,2000HINCDIMOVAL,09H;年单元OUT70H,ALINAL,71HMOV[DI],ALMOVAL,08H;月单元OUT70H,ALINAL,71HMOV[DI],ALINCDIMOVAL,07H;日单元OUT70H,ALINAL,71HMOV[DI],ALINCDIMOVAL,4;时单元OUT70H,ALINAL,71HMOV[DI],ALINCDIMOVAL,2;分单元OUT70H,ALINAL,71HMOV[DI],ALINCDIMOVAL,0;秒单元OUT70H,ALINAL,71HMOV[DI],AL

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案17第6章思考与习题参考答案6-2简述微处理器与I/O设备之间的接口信息。答:微处理器与外设之间交换的信息概括起来有数据信息、状态信息和控制信息。微机中的数据信息通常有数字量、模拟量和开关量三种基本形式。(1)数字量信息:是以连续几位二进制形式表示的数或字符,数字量信息可直接与微处理器连接(2)模拟量信息:是时间上连续变化的量,如电流、电压等都是模拟量信息。由于微处理器只能直接处理数字量信息,因此这些模拟量信息在从外界输入微机前或微机处理之后送到外界时都必须相应转换,如A/D或D/A变换等.(3)开关量信息:是只有两个状态的量,如电路的开与关、阀门的合与断等等。一个开关量只需一位二进制数来表示。状态信息是外部设备向微处理器提供外设当前工作状态的信息,微处理器接收到这些状态就可以了解外设的情况,适时准确地进行有效的数据传送。常见的外设状态信息如输入设备准备好信号(READY)、输出设备是否忙(BUSY)等等。控制信息是微处理器通过I/O接口向外部设备发送控制命令的信息。控制命令主要用于I/O设备的工作方式设置等。数据信息、状态信息还是控制信息,它们都是通过系统的数据总线传送的,因此,广义上讲数据信息、状态信息和控制信息都是数据信息。6-3简述I/O编址方式及各自的特点。答:I/O端口地址的编址有两种基本方法:存储器映射编址(统一编址)和I/O映射编址(独立编址)。存储器映射I/O(Memory-MappedI/O)编址就是I/O端口的地址与存储器的地址统一混合编址,即把一个I/O口地址看作是一个存储单元。在这种编址方式中,I/O口地址与内存单元统一安排在整个内存空间中。对I/O的读写相当于对存储器的读写,即只用访问存储器的指令,而无需用IN或OUT指令即可对I/O进行访问。采用这种编址方法的优点是:●微处理器对外设的操作可使用全部的存储器操作指令,指令多,使用方便。●内存与外设地址分布相同。●无需专用的I/O指令。其缺点是:●外设占用了内存单元,使内存空间减少。●寻址速度比专用I/O指令慢。I/O映射编址(Input/OuptputMapped)是指I/O端口与存储器分开独立编址,即I/O端口和存储器都有自己的一套地址空间,而且互不相干。这样,I/O端口不占用内存空间,但在这种编址方式下,必须采用专用的I/O指令(IN或OUT指令)才能访问I/O设备。采用I/O映射的优点是:●I/O设备不占用内存单元,节约了内存空间。●指令执行速度快。从8086到Pentium,仅支持I/O映射的编址方法,而P6架构及之后的处理器既支持I/O映射编址

18《微型计算机及接口技术》又支持存储器映射编址,即除了用IN/OUT等专用I/O指令外,还可以用访问存储器的指令访问被映射的I/O端口。6-4微机系统中的16位、32位以及64位I/O组织的特点是什么?各自由哪些信号线访问I/O端口?答:16位采用2个8位I/O体,32位采用4个8位I/O体,64位采用8个8位I/O体构成完整的I/O系统。不管是哪一种形式,I/O端口地址范围0000H~FFFFH,处理器仅提供16条地址线来寻址I/O。主要信号线有:16位I/O组织的8086~80286:A15~A0以及IORC、IOWC和BHE;32位的I/O组织80386~Pentium:A15~A2以及BE0~BE3、IORC和IOWC;64位的I/O组织PentiumPro~Cure2:A15~A3以及BE0~BE7、IORC和IOWC。6-5简述I/O指令IN和OUT的含义(结合时序图)。解:IORC及IOWC由处理器的读/写控制信号与存储器/IO选择信号等通过外围电路组合产生如下:IN和OUT指令操作对应的时序关系如图所示。ABusP8或DX指示的地址ABusP8或DX指示的地址ADSADSIORCIOWCDBusDBus(a)IN指令操作时序(b)OUT指令操作时序IN指令是将指定外部设备的数据读入到累加器中,如图(a)所示,IN指令,如INAL,DX执行时,ADSDX指示的地址有效选中相应I/O端口,同时为低电平,将地址锁存,处理器在外围电路的作用下,产生的IORC控制信号有效,在该信号的上升沿,将外设的数据通过数据总线DBus读入内部,送累加器AL中。OUT指令是将累加器的数据写入指定的外部设备中,如图(b)所示,OUT指令,如OUTDX,AX执ADS行时,DX指示的地址有效选中相应I/O端口,同时为低电平,将地址锁存,处理器在外围电路的作用下,产生的IOWC控制信号有效,在该信号的上升沿,将累加器AX中的数据,通过数据总线DBus,送给外设。6-6简述I/O的主要控制方式及其特点。答:主要的输入输出(主机与外设间的数据传送)控制方式有直接程序控制方式、中断控制方式、直接存储器存取控制方式等。直接程序方式分为无条件传送方式和查询传送方式。在程序确信外设已经准备就绪,或外设没有

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案19必要提供准备就绪信号的情况下,就不需要去查询外设的状态而直接进行数据传送的方式称为无条件传送方式。这种方式常用于简单外部设备的输入输出中。在条件传送方式下,首先查询外设状态,满足条件时才进行数据的传送,因此也叫查询传送方式。在外设状态满足要求时,外设通过I/O接口向微处理器发出要求数据传送的请求信号,接到请求信号后,微处理器才去响应,执行输入或输出操作。这就是中断控制的输入输出方式或中断传送方式(简称中断方式)。DMA传送方式是在内存与外设之间开辟的专用数据通道,这个数据通道在DMA控制器硬件的控制下,直接进行数据交换而不通过微处理器,不用I/O指令。这样,数据传送的速度上限取决于存储器的存取速度。DMA方式传送时,由DMA控制器向微处理器请求总线服务,微处理器响应后让出总线,这时系统总线由DMA支配并接管。数据的输入和输出完全由DMA控制器指挥。因此除微处理器外,DMA控制器也是主控设备之一。为了让处理器彻底摆脱管理和控制I/O设备的负担,引入了I/O处理机控制方式。这种方式下,由专用I/O协处理器负责I/O操作和处理。6-7通常输入接口和输出接口硬件上需要什么逻辑电路?答:由于不同类型的I/O接口都是通过总线接到处理器上的,而处理器与I/O接口的数据交换是分时复用的,也就是说同时仅允许访问一个外部设备,因此在输入时只有被选中的I/O接口的数据通过进入数据总线,其它未被选中的I/O接口的数据不能呈现在总线上,因此通常输入接口需要接具有可控的三态功能的缓冲器,而由于处理器速度很快,又在不断访问存储器或I/O,为了让外设稳定接到处理器发送的数据,输出接口需要锁存器。6-10已经波特率为2400bps,字符格式为7位数据,1位校验位,1位停止位,UART发送端的波形如图所示(下方为参考方波,说明该数据是多少(用十六进制表示),采用什么校验?+4.8V0Vf=2.4KHz参考方波)解:由UART字符格式知,传送数据是低位在前高位在后,据已经条件知,1位起始位,7位数据,1位校验位,1位停止位,共10位为一帧,从图中找出起始位(低电平)开始的连接10位,图从2.4KHz的一个脉冲对应2400bps波特率的一个位,即从第3个脉冲开始10位恰是传送的一帧字符,去掉开始的起始位,从第4个脉冲开始取7位数据位,依次是D0=1,D1=1,D2=0,D3=1,D4=0,D5=1和D6=1,校验位=0,停止位=1,因此数据为D6D5D4D3D2D1D0=1101011B=3BH,由于校验为0,因此传送的字符中(含校验位)1的个数为5,奇数,因此为奇校验。6-12如果通过RS-232C进行双机通信,波特率为11520bps,字符格式为1位停止位,没有校验,8位数据,通过示波器得到的波形如图6-54所示,上图是RS-232C的连接器DB9-2脚(RXD)的波形,下面是为了比较方便输入的频率为11.52Kz的参考方波。指出波形对应的数据(用十六进制表示)。

20《微型计算机及接口技术》RS-232CRXD(DB9-2)引脚波形+9.6V0V-9.6VVf=11.52KHz(参考方波)图6-54题6-11图解:分析方法同6-10,只是逻辑关系是相反的,+9.6V对应逻辑0,-9.6V对应逻辑1。第3个参考脉冲对应起始位+9.6V(逻辑0),数据位从第4个脉冲开始的8位,依次为D0=1,D1=0,D2=0,D3=1,D4=0,D5=1,D6=0,D7=0,因此传送的数据为00101011B=2BH6-15简述8255的工作方式。并说明端口A和B作为方式1输入或输出时,C端口与之配合的引脚的含义。解:8255有三种工作方式,方式0,1,和2,方式0为基本的输入输入方式,其输入输出没有固定用于联络的信号,方式1为选通的输入输出方式,A和B口作为I/O,C端口指定的位作为联络应用信号,包括选通信号、输入输出缓冲器满信号和中断信号,方式2为双向通信的方式,主要限于A组的A端口,C用于配合,作为联系信号。A口作为方式1输入时,PC4作为选通输入信号,PC5作为输入缓冲器满信号,PC3作为中断信号;B口作为方式1输入时,PC2作为选通输入信号,PC1作为输入缓冲器满信号,PC0作为中断信号;A口作为方式1输出时,PC6作为输出缓冲器满信号,PC7作为应答信号,PC3作为中断信号;B口作为方式1输出时,PC1作为输出缓冲器满信号,PC2作为应答信号,PC0作为中断信号;6-16假设8255的端口地址为60H-63H,试分别编写满足条件的初始化程序:(1)将A组和B组设置为方式0,端口A和B设成输入端口,C上半口为输入,下半口为输出。(2)将A口设为方式2,B口设为方式1输出。(3)将A口设为方式1输出,B口为方式1输出,PC4和PC5为输出。解:(1)MOVAL,10011000BOUT63H,AL(2)MOVAL,11000100BOUT63H,AL(3)MOVAL,10100100BOUT63H,AL6-17如图6.55所示为以8086为核心采用8255扩展I/O接口,A口接一输入设备,B接输出设备,PC2作为检测输入设备的的准备就绪信号READY,PC6作为输出设备忙BUSY检测端。(1)写出8255的初始化程序片段

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案21(2)写出读取输入设备数据并存入内存ES:DI指示单元的子程序(3)写出从DS:SI指示的内存单元取出数据写到输出设备的子程序(4)已知8255的PC7接一上拉电阻,其对地连接一细长微型导线(A与B之间),PC0通过驱动接一蜂鸣器构成一简易防盗报警系统,如果微型导线被碰断,则蜂鸣器发出报警声(蜂鸣器得电123而响)直到导线被保安人为接上,报警的同时向输出设备发送字符串“Grasptheburglar!”通知D值班人员采取措施。写出有关程序。D7-D0344D0PA0333输入设备D1PA1322D2PA2311M/IOD3PA33040READYN2D4PA412939A15D5PA5C22838A14D6U4PA632737A13D7PA748825518输出设备A12U1PB05WR3619A11WRPB1620VCCA10PB21174F3021VCCA9PB31222PB423BELLA8PB5R21RD524BA7N12RESET35RDPB62510KA6RESETPB73R1A5414BUSYA4PC08415A3U2PC11K56616A265U3B74F32CSPC217BG1TitlePC3A71113901374F30PC41212A1PC5811SizeNumberA09A1PC610ABA0PC7A4ADate:10-Aug-2004File:F:教学123图6.55题6-17图解:(1)MOVAL,10011000BMOVDX,0FEFFH;控制口OUTDX,AL(2)MOVDX,0FEFEH;C口WAITL:INAL,DX;ReadyMOVDX,0FEFCH;A口INAL,DXTESTAL,00100000B;PC5JZWAITL;未准备好等待MOVDX,0FEFCH;A口INAL,DX;读输入设备数据MOVES:[DI],AL;写入指定内存单元(3)MOVDX,0FEFEH;C口WAITP:INAL,DXTESTAL,01000000B;PC6(BUSY)JNZWAITPMOVAL,DS[SI]MOVDX,0FEFDH;B口OUTDX,AL;数据输出(4)START:MOVDX,0FEFEHINAL,DXTESTAL,80H;判断PC7

22《微型计算机及接口技术》JNZBEEPMOVDX,0FEFFHMOVAL,0;PC0=0置复位命令字OUTDX,AL;取消报警JMPSTARTBEEP:MOVDX,0FEFFHMOVAL,1;PC0=1OUTDX,AL;报警MOVSI,OFFSETSTRINGSMOVCX,18;18个字符WAITB:MOVDX,0FEFFHINAL,DXTESTAL,01000000B;BUSY=1?JNZWAITBMOVAL,[SI]MOVDX,OFEFDH;B口OUTDX,ALINCSILOOPWAITBSTRINGSDB‘Grasptheburglar!’6-19已知8254的端口地址为9F0CH~9F0FH,外接时钟频率为2MHz,利用8254的OUT0通道产生周期为1ms的方波,OUT1产生最快的连续脉冲序列,周期为多少?OUT2产生最大的负脉冲(建议方式1),负脉冲的宽度为多少。试编制满足上述要求的程序。解:(1)满足要求的程序如下.MODELSMALL.CODE.STARTUPMOVAL,00110110B;CTC0命令字:方波信号发生器方式MOVDX,9F0FH;8254控制口地址OUTDX,ALMOVDX,9F0CH;CTC0通道地址MOVAX,2000;计数常数=2MHz*1000us=2000OUTDX,AL;实际收入低8位初值MOVAL,AH;取高8位OUTDX,AL;写高8位初值MOVAL01010100B;CTC1命令字:速率发生器方式MOVDX,9F0FH;8254控制口地址OUTDX,ALMOVDX,9F0DH;CTC1通道地址MOVAL,2;计数常数=2(最快)

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案23OUTDX,AL;写初值MOVAL10110010B;CTC2命令字:负脉冲信号发生器方式MOVDX,9F0FH;8254控制口地址OUTDX,ALMOVDX,9F0EH;CTC2通道地址MOVAL,0;计数常数=0000(最大值)OUTDX,AL;写初值OUTDX,AL.EXITEND(2)OUT1产生最快的连续脉冲序列,1个周期为2个计数时钟,因此周期=1/2MHz*2=1us;OUT2产生最大的负脉冲,负脉冲的宽度为65536个计数脉冲周期=65536×1/2MHz=32768us=32.768ms6-20已知8254的CLK0接5MHz时钟,其端口地址为280H,281H,282H和283H系统采用16位的8086(1)画出8254与系统的连接图,译码电路自行设计。(2)要在OUT0周期性地产生负脉冲宽度为2ms的信号作为定时中断请求信号,写出初始化程序(3)若利用8254产生1S为周期的定时中断信号,说明实现方法,画出相应的连接图,并编写相应程序。(1)由地址:280H~283H知:(地址不重叠,即全译码,I/O端口16条地址线全部要参与译码)A15A14A13A12A11A10A9A8A7A6A5A4A3A2=00000010100000xxB电路如下:+5VA1574LS27A14GATE0A13GATE1A12GATE2A11A1074LS305MHzA9CSCLK0A774LS27OUT0A8A6CLK1A5WRWRA4OUT1A3RDRDOUT2A2A1A1M/IOA0A0AEN(2)OUT0产生2ms定时中断信号(方波)MOVAL,00110110B;ctc0控制字MOVDX,0283HOUTDX,AL

24《微型计算机及接口技术》MOVAX,20000;初值=5MHz*(2ms*2)=5000*4=20000;注意:2ms仅为负脉冲宽度,因此一个周期=4msMOVDX,280H;CTC0通道OUTDX,AL;写低字节初值MOVAL,AHOUTDX,AL;写高字节初值(3)将OUT0连接到CLK1,CTC1初值=1S/4ms=1000/4=250MOVAL,01010110B;ctc1控制字MOVDX,0283HOUTDX,ALMOVAX,250;初值=1S/4ms=250MOVDX,281H;CTC1通道OUTDX,AL;写初值

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案25第7章思考与习题参考答案7-2在中断响应过程中,硬件完成的主要任务有哪些?答:从接到中断请求到中断处理之前(转中断服务程序入口地址)这一段时间称为中断响应阶段或中断响应过程。对于可屏蔽中断,微处理器响应中断,硬件会自动完成以下几项工作:(1)中断响应的第一阶段即接到中断申请,处理完当前指令即进入响应周期。(2)第二阶段即中断响应周期,在其间微处理器向外部中断控制器发送两个响应脉冲信号INTA作为INTR的响应,每一个脉冲占用一个总线周期。第一个响应脉冲通知中断控制器,微处理器已经响应外部的中断请求,这时中断控制器准备提供该外部中断的中断类型号。在第二个响应脉冲到来时,微处理器取走中断控制器提供的中断类型号。(3)将标志寄存器中的内容压入堆栈保护,然后清IF和TF标志,以禁止INTR中断引脚以及陷进和单步中断。(4)将断点地址压入堆栈(CS:IP或CS:EIP或CS:RIP)。对于外部中断以及陷井异常:断点地址是指中断时微处理器待执行的下一条指令对应的逻辑地址;对于故障异常:断点地址是指中断时微处理器待执行的当前指令对应的逻辑地址。先压入断点地址的CS,后压入偏移地址IP或EIP或RIP。(5)微处理器从外部中断控制器取得中断类型号码n,通过中断类型号与中断服务程序入口地址的关系找出该类型对应的段基地址和偏移地址,从而转入中断服务程序入口地址,完成中断响应任务。7-4中断描述符包括了哪些地址信息?答:中断描述符描述了某中断对应中断服务程序的入口地址信息及其属性,包括中断服务程序入口地址所在段的段内偏移地址和段选择子等。每个中断描述符占8个字节,中断描述符格式如下:高地址偏移地址(A31~A16)PDPL0111000000000段的选择子低地址偏移地址(A15-A0)图7.4中断描述符其中偏移地址A0~A31共32位;段选择子16位,存放在段寄存器中;P为存在位,P=1表明中断描述符在物理存储器中;DPL为中断描述符特权级两位,共4级,00,01,10,11,其中00为最高级,11为最低级。7-5简述实地址方式和保护地址方式下中断服务程序入口地址的形成方法。答:1.在实方式下,中断类型号n与该中断对应的中断向量存放的起始地址之间的关系是:中断向量存放的起始地址=4×n,即中断类型号为n的中断向量存放在从4n到4n+3这4个单元,其中4n+3(高字节),4n+2(低字节)存放中断服务程序入口地址的段地址,而4n+1(高字节),4n(低字节)存放中断服务程序入口地址的偏移地址。因此实方式下的中断服务程序入口地址=段地址×16+偏移地址。2.保护方式下的中断服务程序入口地址是通过中断描述符的结构来寻址的。具体方法如下:(1)根据中断类型号从中断描述符表中找出中断描述符

26《微型计算机及接口技术》中断描述符在IDT中的起始地址=中断类型号n×8+IDT基地址,从该地址开始取出8个字节即中断描述符。由中断描述符的格式可知,找到了中断描述符,就找到了偏移地址和选择子。(2)通过中断描述符中的选择子从GDT或LDT中找出段描述符根据中断描述符的格式,得到中断描述符中16位的段选择子,最低两位为请求特权层,TI指示该段在哪个描述符表中(TI=0选中GDT,TI=1选中LDT),高13位为寻找段描述符的索引,通过该索引从GDT或LDT表中找到段描述符,段描述符的起始位置=索引值×8+GDT或LDT基地址,从该地址开始取出8个字节即段描述符。由段描述符格式知,找到了段描述符就找到了段基地址。(3)根据段描述符提供的段基地址与中断描述符提供的偏移地址合成入口地址根据段描述符的格式,对于IA-32处理器从段描述符中取出32位的段基地址,再与中断描述符中的32位偏移地址相加即可得到32位的中断服务程序入口地址。如果是80286则段基址与偏移地址均为24位,因此得到的中断服务程序入口地址也是24位的。7-6已知内存单元中有关单元存放的信息如表7.7所示,CR0=60000001H,IDT的首地址为65000000H,GDT首地址为00100000H,求保护方式下类型号为11H的中断服务程序入口地址。表7.7题7-5内存数据分布内存地址数据(H)内存地址数据(H)内存地址数据(H)00108064H8506700930H8965000085H5100108065H0006700931H6565000086H8700108066H2006700932H1265000087H0000108067H0006700933H2565000088H120010810EH5E06700934H1065000089H200010810FH3C06700935H496500008AH1300108110HFF06700936HC66500008BH8100108111H1F06700937H0F6500008CH0000108112H00::6500008DHEE00108113H7006708258H906500008EH4200108114H0006708259HC76500008FH0000108115HF20670825AH1365000090HFF00108116H440670825BH0065000091H0100108117H010670825CH0065000092H58::0670825DHEE65000093H8200200C20HB60670825EH4565000094H0000200C21H800670825FH3265000095H4900200C22H7006708210HF265000096H4400200C23H0606708211H5D65000097H00解:CR0=60000001H知PG=0,PE=1保护方式中断描述符首地址=IDT表首地址+中断类型号*8=65000000H+11H*8=65000088H所以中断描述符=0042EE0081132012H其中描述的偏移地址=00422012H,段选择子=8113H因此段描述符首地址=GDT首地址+索引*8=00100000H+8110H=00108110H段描述符=0144F20070001FFFH,其描述符的段基地址=01007000H,因此中断服务程序入口地址=段基地址+偏移地址=01007000H+00422012H=01429012H7-88259的IRR什么情况下某位置1,什么情况下复位?如果IRR=FFH,说明什么?答:IRR在有中断申请且还没有被响应时置1,没有中断申请或有申请但已经被响应时被复位,如果IRR=FFH,说明8个中断都有中断申请但都还没有被响应。

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案277-98259的ISR什么情况下某位置1,什么情况下复位?如果ISR=FFH,说明什么?答:ISR在有中断服务且中断没有结束时相位置位,中断结束时复位,如果ISR=FFH说明8个中断源都有在被中断响应且中断处理没有结束,最先进入中断响应的是最低优先的中断源,先低到高级的次序进入中断响应的过程,最后进入的是最高级中断的中断源。

28《微型计算机及接口技术》第10章思考与习题参考答案10-1名词解释(1)DAS(2)DAC(3)ADC答:(1)DAS=DataAcquisitionSystem即数据采集系统(2)DAC=DigtaltoAnalogConverter即数模转换器(3)ADC=AnalogtoDigtalConverter即模数转换器10-2简述DAC与ADC的主要性能指标。答:1.DAC主要性能指标(1)DAC转换精度:DAC转换精度是指实际转换得到的输出值与理论值之间的误差程度,可分为绝对精度和相对精度两种衡量标准。绝对精度是指每个输出值接近理论值的程度。相对精度一般用绝对精度相对于满度量程输出的百分比表示。(2)DAC分辨率:分辨率指DAC所能分辨最小量化信号的能力,是对微小输入量变化的敏感程度的描述。n位二进制D/A转换器的分辨率一般用2-n来表示。由于分辨率与n密切相关,因此,习惯上,直接用n表示DAC的分辨率。(3)DAC转换速率和建立时间:转换速率指模拟信号输出电压的最大变化速度,单位为V/μs。建立时间是指DAC输出电压到达规定范围(终值的1/2最低有效位)时所需要的时间。转换速度越高越好,建立时间越短越好。(4)DAC线性误差:理想情况下,DAC输出与输入的关系应该是线性的,但实际上输出特性并不是理想线性的。把实际转换特性偏离理想转换特性的最大值称为线性误差。线性误差越小越好。2.ADC主要性能指标(1)ADC转换精度:转换精度反映了ADC的实际输出接近理想输出的精确程度。ADC的精度通常采用数字量的最低有效位LSB来表示。(2)ADC转换时间与转换速率:转换时间是指完成一次A/D转换所需要时间,而转换速率是转换时间的倒数,因此,转换速率表明了ADC的速度,转换速率越高,速度越快。(3)ADC分辨率:分辨率是指ADC能够分辨最小量化信号(输入最小模拟电压值)的能力,与数据位数有关,位数越多,分辨率越高。对于n位二进制的ADC来说,分辨率为:分辨率=满量程输入模拟电压值/2n10-3假设一8位T型电阻网络式DAC,其参考电压为-5V,Rf=R,则将输出的数了量为68H时,输出电压为多少?当获得的输出电压为4V时,应该向DAC送入的数字量是多少?Rfn1RfVref解:U。=Vref2iDi=D,Vref=-5V,Rf=R,所以D=68H,U0=5×68H/256=2.03125V;nn2R02RU0=4V,则D=4/5*256=204.8≈205=C0H10-4利用图10.7的电路,如果DAC0832的地址为3A9H,写出产生最低点为1V,最高点为4V的三角波(如图10.20所示)程序片段。4V1V0V图10.201-4V三角波

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案29解:1V对应的数字量D1V=1/5*256=51.2≈51,4V对应的数字量D4V=4/5*256=204.8≈205=C0H参考程序片段如下:DLVEQU51DHVEQU205MOVDX,3A9HMOVAL,DLVINC0:OUTDX,ALCMPAL,DHVJLEINCDDEC0:DECALOUTDX,ALCMPAL,DLVJADEC0INCD:INCALJMPINC0或MOVDX,3A9HMOVAL,DLVREPLP1:OUTDX,ALCMPAL,DHVJBINCDVREPLP2DECALOUTDX,ALCMPAL,DLVJAREPLP2INCDV:INCALJMPREPLP110-5一数据采集与处理系统如图10.21所示。已知8255的PA口作为A/D转换器ADC0809的接口;ADC0809的500KHCLK时钟由8254OUT1产生,已知8254的CLK1端接2MHz的时钟信号,GATE1接8255的PC7;DAC0832作为后向输出通道,各地址关系及与系统总线连接如图所示。系统工作过程为:采集ADC0809的压力1,将其转换后的数字量一方面存放到内存缓冲区(由DATABUF指示,假设DATABUF变量已定义),另一方面变换后的数字量通过逻辑取反后由DAC0832变换成模拟量输出,如果采集到的数据对应的模拟量超过4V,则通过8254的OUT2产生最大的负脉冲,如果低于1V,则让8254的OUT2产生1KHz的方波。试按以下要求用编写有关程序片段:(1)写出8255在本应用系统中的初始化程序片段(2)写出供ADC0809的CLK端500KHZ方波的程序片段(3)根据系统工作过程写出满足要求的程序片段(4)通过该电路,还可扩展应用,请自行设计应用,说明要求,并给出参考答案

30《微型计算机及接口技术》图10.21一数据采集与处理系统原理示意图解:地址分配:8254:E00H~E03H8255:E04H~E07HDAC0832:E14H~E17H任何一个地址均可(1)8255初始化要做的工作就是确定工作方式:A方式0输入、B方式0输出、C上半口输出,下半口输入MOVDX,0E07H;8255控制端口MOVAL,10010001B;91HOUTDX,AL(2)8254产生500KHz方波计数值初=2MHz/500KHz=2000/500=4MOVDX,0E05HINAL,DXORAL,80H;8255PB7=GATE1=1OUTDX,ALMOVDX,0E03H;8254控制端口地址MOVAL,01010110B;8254通道1设置为8位读写,二进制计数OUTDX,ALMOVAL,4;初值MOVDX,0E01H;8254通道1口地址OUTDX,AL(3)压力1对应的ADC0809的通道是IN2,对应ADDC,B,A=010即8255的PC2,1,0=010对ADC0809的操作依据三个步骤进行,即启动并锁存地址、查询EOC状态以及转换读取结果,然后根据结果确定DAC0832的输出波形。假设初始化工作已经做完如(1)和(2)参考程序如下:ADCSPROCNEARSTART:MOVDX,0E05H;8255的B端口地址

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案31MOVAL,82H;ADC0809通道2(IN2)(注意保持PB7=1)OUTDX,AL;ALE、START、OE=0,选中IN2MOVAL,0B2H;ALE=1、START=1、OE=0,选中IN2(保持PB7=1)OUTDX,ALNOPNOPMOVAL,82HOUTDX,AL;至此产生START和ALE的锁存信号MOVDX,0E05H;指向8255的C端口ADCWAIT:INAL,DXANDAL,01JZADCWAIT;判断EOC是否为1MOVDX,0E04H;8255的A口地址INAL,DX;读取转换结果MOVDATABUF,ALCMPAL,1/5*256;1V对应数字量JBCALLSUB1;低于1V转OUT0产生1KHz的方波子程序CMPAL,4/5*256;4V对应数字量JACALLSUB2;大于4V转OUT0产生最大负脉冲子程序NOTALMOVDX,0E14H;DAC0832口地址(E14H~E17H)OUTDX,ALJMPSTARTCALLSUB1:CALLSUB1JMPSTARTCALLSUB2:CALLSUB2JMPSTARTDATABUFDB?RETADCSENDPSUB1PROCNEAR;OUT2产生最大负脉冲子程序(PC7=GATE2)MOVDX,0E07HMOVAL,00001110B;PC7=0(GATE2)OUTDX,ALPUSHDXPUSHALMOVDX,0E03H;8254控制端口地址MOVAL,10110010B;通道2设置为16位读写,二进制计数,方式1OUTDX,ALMOVAL,0;初值

32《微型计算机及接口技术》MOVDX,0E02H;8254通道2口地址OUTDX,AL;写低8位初值OUTDX,AL;写高8位初值POPALPOPDXINCAL:PC7=1(GATE2)OUTDX,ALNOPNOPDECALOUTDX,AL;PC7=0(GATE2)RETSUB1ENDPSUB2PROCNEAR;计数值初=2MHz/1KHz=2000/1=2000MOVDX,0E07HMOVAL,00001111B;PC7=1(GATE2)OUTDX,ALMOVDX,0E03H;8254控制端口地址MOVAL,10110110B;通道2设置为16位读写,二进制计数,方式3OUTDX,ALMOVAX,2000;初值MOVDX,0E02H;8254通道2口地址OUTDX,AL;写低8位初值MOVAL,AHOUTDX,AL;写高8位初值RETSUB2ENDP(4)从图中可以看出,8254还有通道0没有使用,可以通过控制GAT0,编程使OUT0产生不同的波形,可将GATA0直接接+5V,让OUT0产生10ms为周期的连续波,参考子程序如下:SUB3PROCNEAR;计数值初=2MHz×10ms=2000*10=40000MOVDX,0E03H;8254控制端口地址MOVAL,00110100B;通道0设置为16位读写,二进制计数,方式2OUTDX,ALMOVAX,40000;初值MOVDX,0E02H;8254通道2口地址OUTDX,AL;写低8位初值MOVAL,AHOUTDX,AL;写高8位初值RETSUB3ENDP

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案33第11章思考与习题参考答案11-3求下列总线的带宽(1)PCI(2)AGP4X(3)PCIExpress16X解:(1)PCI为32位宽度,总线频率为33MHz,因此带宽=33×32/8=132MB/S(2)AGP×4,64位数据,基频=66MHz,带宽=66×4×64/8=2112MB/S=2.112GB/S(3)PCIExpress16X,基频=2.5GHz,10位编码,带宽=2.5×16=40Gbps=40×1/10=4GB/S11-4简述系统总线的信号类型,系统总线的三个时代代表总线是什么?解:(1)总线的信号主要包括电源、数据线、地址线和控制线(2)代表三个时代的总线:ISA总线、PCI总线以及PCIExpress总线。

34《微型计算机及接口技术》第12章思考与习题参考答案10-2简述微型计算机系统的硬件构成。解:典型的微型计算机硬件系统由主机与外设构成,如图12.1所示。主机包括系统板、电源、硬盘、主机箱等以及可选扩充部件等,外设中的常用输入设备包括键盘、鼠标、扫描仪、摄头等,输出设备常见的有显示器、打印机等,输入输出设备的包括主机外的存储器U盘和移动硬盘或外置硬盘以及传真机、调制解调器等。投影仪打印机扫描仪传真机U盘主机移动硬盘或外围硬盘显示器鼠标键盘摄像头12-4简述芯片组中MCH或GMCH及ICH芯片的作用。解:MCH或GMCH是芯片组的核心芯片,主要负责快速通道与处理器的传输,称为存储控制中枢或带图形功能的存储控制中枢;而ICH则主要负责I/O通道的控制,与MCH或GMCH相比,ICH控制的部分速度较低。12-5PC/XT,PC/AT,386,486,Pentium~Pentium4,Cure2Duo~Cure2Extreme主板各有什么主要特点?解:PC/XT主板以8088为核心,集成度低,全部采用通用芯片构成,采用8位的XT总线,地址线20条,数据线8条;PC/AT主板以80286为核心,集成度比XT高,但大部采用通用芯片,后来发展到采用中小规模的门阵列作为外部接口,有协处理器插座,首次开始采用带后备电池的CMOSRAM和实时钟,采用16位的AT总线标准,地址线24条,数据线16条,开始引入内存条;386主板以80386为核心,外围接口全部采用门阵列芯片,有协处理器插座,板子支持开始Cache,采用ISA和EISA总线标准;486主板以80486为核心,增加了Cache采用ISA和VESA总线标准,开始支持影子内存,由于486开始协处理器集成到内部,所以首次取消协处理器插座;Pentium主板以Pentium为核心,开始全面采用芯片组技术,采用ISA和PCI并存的总线形式,开始支持USB接口;PentiumII主板以PentiumII为核心,采用ISA、PCI和AGP并存的多总线形式,处理器封闭形式为SLOT1,AGP用于图形接口;PentiumIII主板以PentiumIII为核心,采用PCI和AGP并存的总线形式,处理器封闭形式改回SOCKET,开始支持AC‘97以及以太网接口;Pentium4主板以Pentium4为核心,采用PCI和AGP或PCI和PCIEXpress并存的总线形式,支持的硬盘速度更快更大,支持394接口;CureDuo主板以CureDuo为核心,芯片组全面提升,速度更快,带宽更大,以PCI和PCIExpress*1及*16为主要总线形式,开始引入串行硬盘接口SATA,支持外围式的eSATA,开始支持矩阵存储技术,

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案35支持DDR2;CureQuard主板以CureQuard为核心,芯片组全面提升,MCH或GMCH速度更快,带宽更大,以PCI和PCIExpress*1及*16为主要总线形式;CureExtreme主板以CureExtreme为核心,芯片组全面提升,MCH或GMCH速度更快,带宽更大,以PCI和PCIExpress*1及*16为主要总线形式,支持DDR3内存;'

您可能关注的文档

- 《当代教育心理学》习题答案.pdf

- 《征管评估》题库(初、中、高).doc

- 《微型计算机原理与接口技术》(第三版)习题答案.doc

- 《微型计算机原理与接口技术》(第三版)习题答案.pdf

- 《微型计算机原理与接口技术》(第四版)课后习题答案.pdf

- 《微型计算机原理与接口技术》周荷琴_吴秀清(第三版)课后习题答案.pdf

- 《微型计算机原理与接口技术》第二版答案张荣标.pdf

- 《微型计算机原理及应用技术》部分习题答案(新).doc

- 》课后答案_(第3版)清华大学出版社__杨素行.pdf

- 《微机原理与接口技术》(第二版)龚尚福-习题解析和实验指导.doc

- 《微机原理与接口技术》(第四版)周何琴课后习题答案.pdf

- 《微机原理与接口技术》习题答案.doc

- 《微机原理与接口技术》洪永强课后习题集 第2版.doc

- 微机原理与接口技术》洪永强课后习题集__第2版.pdf

- 《微机原理与接口技术》课后习题答案.doc

- 《微机原理与接口技术》课程考试复习题集含答案.doc

- 《微机原理及接口技术》(第2版)—习题解答.doc

- 《微波技术与微波电路》课后答案-华南理工大学.pdf

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明