- 4.71 MB

- 2022-04-22 11:31:20 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

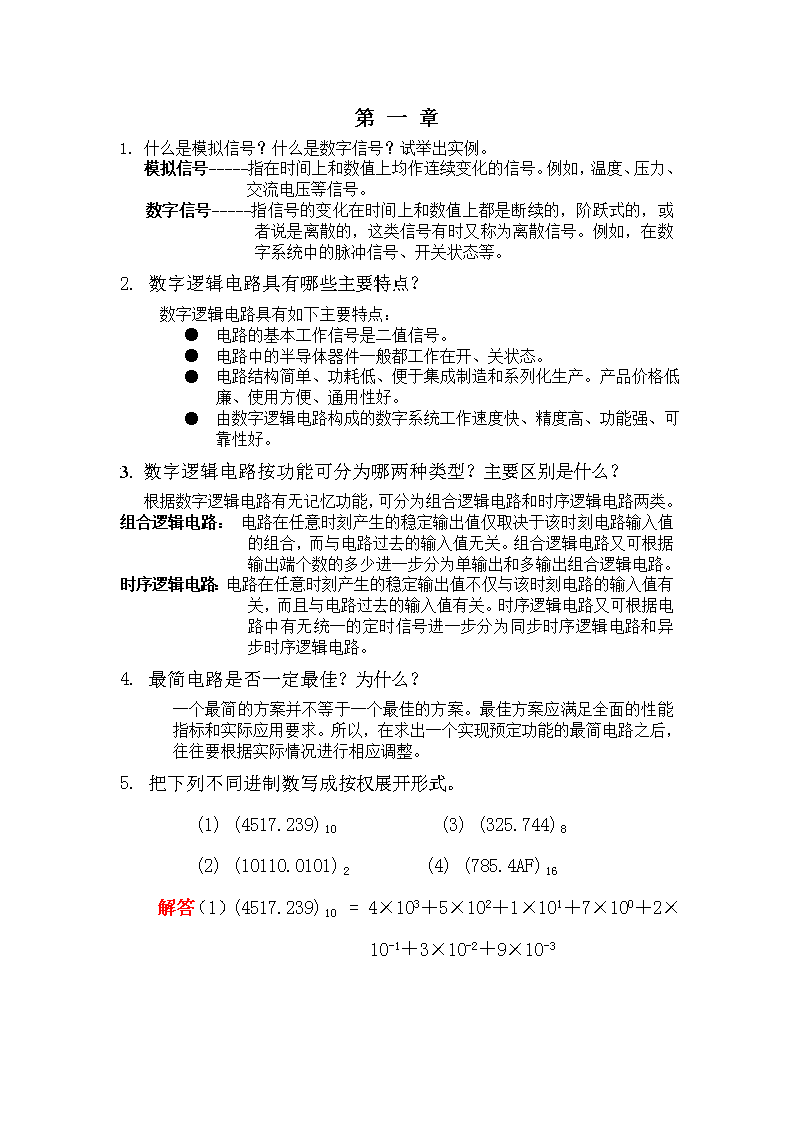

'第一章1.什么是模拟信号?什么是数字信号?试举出实例。模拟信号-----指在时间上和数值上均作连续变化的信号。例如,温度、压力、交流电压等信号。数字信号-----指信号的变化在时间上和数值上都是断续的,阶跃式的,或者说是离散的,这类信号有时又称为离散信号。例如,在数字系统中的脉冲信号、开关状态等。2.数字逻辑电路具有哪些主要特点?数字逻辑电路具有如下主要特点:● 电路的基本工作信号是二值信号。● 电路中的半导体器件一般都工作在开、关状态。●电路结构简单、功耗低、便于集成制造和系列化生产。产品价格低廉、使用方便、通用性好。● 由数字逻辑电路构成的数字系统工作速度快、精度高、功能强、可靠性好。3.数字逻辑电路按功能可分为哪两种类型?主要区别是什么?根据数字逻辑电路有无记忆功能,可分为组合逻辑电路和时序逻辑电路两类。组合逻辑电路:电路在任意时刻产生的稳定输出值仅取决于该时刻电路输入值的组合,而与电路过去的输入值无关。组合逻辑电路又可根据输出端个数的多少进一步分为单输出和多输出组合逻辑电路。时序逻辑电路:电路在任意时刻产生的稳定输出值不仅与该时刻电路的输入值有关,而且与电路过去的输入值有关。时序逻辑电路又可根据电路中有无统一的定时信号进一步分为同步时序逻辑电路和异步时序逻辑电路。4.最简电路是否一定最佳?为什么?一个最简的方案并不等于一个最佳的方案。最佳方案应满足全面的性能指标和实际应用要求。所以,在求出一个实现预定功能的最简电路之后,往往要根据实际情况进行相应调整。5.把下列不同进制数写成按权展开形式。(1)(4517.239)10 (3)(325.744)8(2)(10110.0101)2 (4)(785.4AF)16解答(1)(4517.239)10=4×103+5×102+1×101+7×100+2×10-1+3×10-2+9×10-3

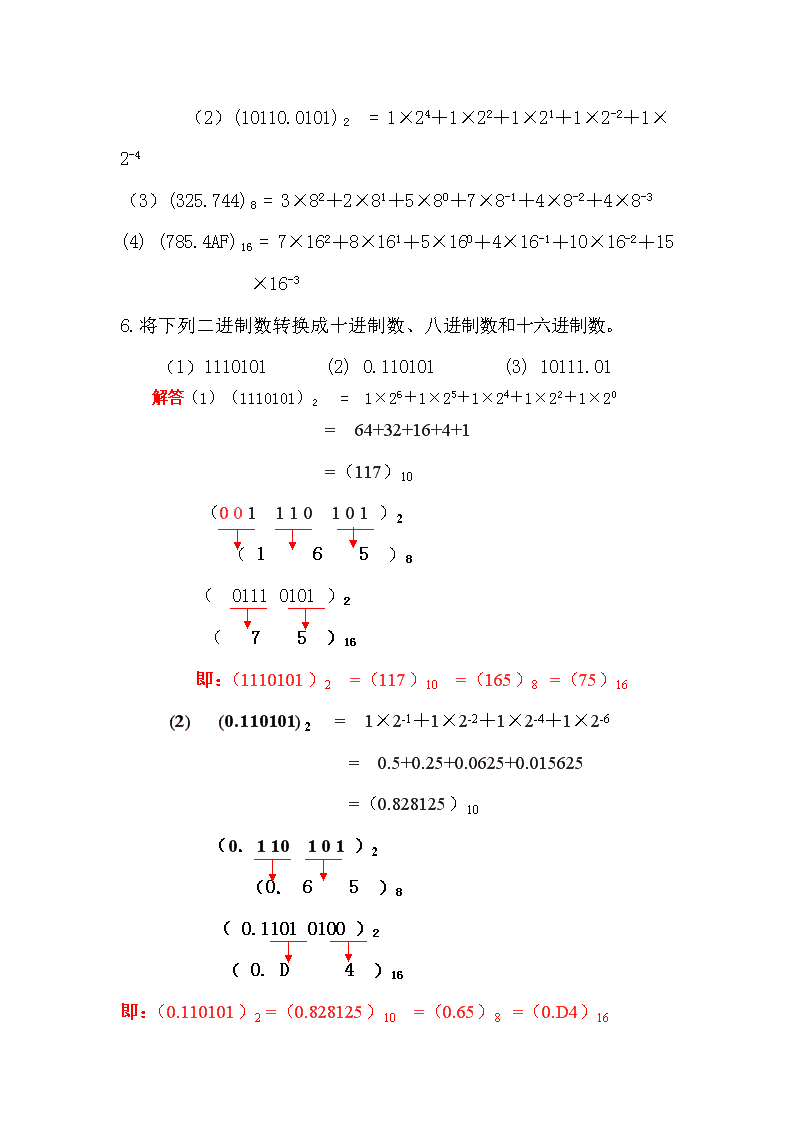

(2)(10110.0101)2 =1×24+1×22+1×21+1×2-2+1×2-4(3)(325.744)8=3×82+2×81+5×80+7×8-1+4×8-2+4×8-3(4)(785.4AF)16=7×162+8×161+5×160+4×16-1+10×16-2+15×16-36.将下列二进制数转换成十进制数、八进制数和十六进制数。(1)1110101(2)0.110101(3)10111.01解答(1)(1110101)2=1×26+1×25+1×24+1×22+1×20=64+32+16+4+1=(117)10(001110101)2(165)8(01110101)2(75)16即:(1110101)2=(117)10=(165)8=(75)16(2)(0.110101)2=1×2-1+1×2-2+1×2-4+1×2-6=0.5+0.25+0.0625+0.015625=(0.828125)10(0.110101)2(0.65)8(0.11010100)2(0.D4)16即:(0.110101)2=(0.828125)10=(0.65)8=(0.D4)16

(3)(10111.01)2=1×24+1×22+1×21+1×20+1×2-2=16+4+2+1+0.25=(23.25)10(010111.010)2(27.2)8(00010111.0100)2(17.4)16即:(10111.01)2=(23.25)10=(27.2)8=(17.4)167.将下列十进制数转换成二进制数、八进制数和十六进制数(精确到小数点后4位)。(1)29(2)0.27(3)33.33解答(1)(29)10=24+23+22+20=(11101)2=(011101)2=(35)8=(00011101)2=(1D)16(2)(0.27)10≈ 2-2+2-6 = (0.010001)2=(0.010001)2=(0.21)8=(0.01000100)2=(0.44)16(3)(33.33)10=(?)2=(?)8=(?)16即:(33.33)10=(100001.0101)2=(41.24)8=(21.5)168.如何判断一个二进制正整数B=b6b5b4b3b2b1b0能否被(4)10整除?解答B=b6b5b4b3b2b1b0=b6×26+b5×25+b4×24+b3×23+b2×22+b1×21+b0×20=(b6×24+b5×23+b4×22+b3×21+b2)×22+b1×21+b0

×20可见,只需b1=b0=0即可。9.写出下列各数的原码、反码和补码。(1)0.1011(2)–10110解答(1)由于0.1011为正数,所以有原码=补码=反码=0.1011(2)由于真值=-10110为负数,所以有原码=110110(符号位为1,数值位与真值相同)反码=101001(符号位为1,数值位为真值的数值位按位变反)补码=101010(符号位为1,数值位为真值的数值位按位变反,末位加1)10.已知[N]补=1.0110,求[N]原,[N]反和N。解答[N]反码=1.0101(补码的数值位末位减1)[N]原码=1.1010(反码的数值位按位变反)N=-0.1010(原码的符号位1用“-”表示)11.将下列余3码转换成十进制数和2421码。(1)011010000011(2)01000101.1001解答(1)(011010000011)余3码=350)10=(001110110000)2421(2)(01000101.1001)余3码=(12.6)10=(00010010.1100)242112.试用8421码和格雷码分别表示下列各数。(1)(111110)2(2)(1100110)2解答(1)(111110)2=(62)10=(01100010)8421=(100001)Gray(2)(1100110)2=(102)10

=(000100000010)8421=(1010101)Gray第二章1假定一个电路中,指示灯F和开关A、B、C的关系为F=(A+B)C试画出相应电路图。解答电路图如图1所示。图12用逻辑代数的公理、定理和规则证明下列表达式:(1)(2)(3)(4)

解答(1)证明如下(2)证明如下(3)证明如下(4)证明如下3用真值表验证下列表达式:(1)

(2)解答(1)真值表证明如表1所示。表1ABA+B00001000010111111010111111000100(1)真值表证明如表2所示。表2ABABA+B001010000100111110001111110101004求下列函数的反函数和对偶函数:(1)(2)

(3)(4)解答(1)(2)(3)(4)5回答下列问题:(1)如果已知X+Y和X+Z的逻辑值相同,那么Y和Z的逻辑值一定相同。正确吗?为什么?(2)如果已知XY和XZ的逻辑值相同,那么那么Y和Z的逻辑值一定相同。正确吗?为什么?(3)如果已知X+Y和X+Z的逻辑值相同,且XY和XZ的逻辑值相同,那么Y=Z。正确吗?为什么?(4)如果已知X+Y和X·Y的逻辑值相同,那么X和Y的逻辑值一定相同。正确吗?为什么?解答(1)错误。因为当X=1时,Y≠Z同样可以使等式X+Y=X+Z成立。(2)错误。因为当X=0时,Y≠Z同样可以使等式XY=XZ成立。

(3)正确。因为若Y≠Z,则当X=0时,等式X+Y=X+Z不可能成立;当X=1时,等式XY=XZ不可能成立;仅当Y=Z时,才能使X+Y=X+Z和XY=XZ同时成立。(4)正确。因为若Y≠Y,则X+Y=1,而X·Y=0,等式X+Y=X·Y不成立。6用代数法求出下列逻辑函数的最简“与-或”表达式。(1)(2)(3)(4)解答(1)(2)(3)(4)

7.将下列逻辑函数表示成“最小项之和”形式及“最大项之积”的简写形式。(1)(2)解答(1)(2)

8用卡诺图化简法求出下列逻辑函数的最简“与-或”表达式和最简“或-与”表达式。(1)(2)(3)解答(1)函数的卡诺图如图2所示。ACD000111101011010011111111111110图2(最简与-或式)(最简或-与式)

(2)函数的卡诺图如图3所示。ABCD000111101011010011111111111110图3F(A,B,C,D)=B+D(既是最简与-或式,也是最简或-与式)(3)函数的卡诺图如图4所示。ABCD0001111010110100111111110图4(最簡与-或式)(最簡或-与式)9用卡诺图判断函数F(A,B,C,D)和G(A,B,C,D)有何关系?(1)(2)

解答(1)作出函数F和G的卡诺图分别如图5、图6所示。0001111011111111CDABABCD000111101011010011111111100001111010图5图6由卡诺图可知,F和G互为反函数,即:(2)作出函数F和G的卡诺图分别如图7、图8所示。ABCD00011110101101001111111110ABCD00011110101101001111111110图7图8由卡诺图可知,F和G相等,即:10某函数的卡诺图如图9所示.

图9(1)若,当a取何值时能得到最简的“与-或”表达式?(2)a和b各取何值时能得到最简的“与-或”表达式?解答(1)当时,令a=1,b=0能得到最简“与-或”表达式:(3项)(2)当a=1,b=1时,能得到最简的“与-或”表达式:(3项)11用列表法化简逻辑函数解答或者第三章9.图1(a)所示为三态门组成的总线换向开关电路,其中,A、B为信号输入端,分别送两个频率不同的信号;EN为换向控制端,控制电平波形如图(b)所示。试画出Y1、Y2的波形。

图1电路图及有关信号波形解答图中,EN=0:Y1=,Y2=;EN=1:Y1=,Y2=。据此,可做出Y1、Y2的波形图如图2所示。图210.试画出实现如下功能的CMOS电路图。(1)(2)(3)解答(1)实现的CMOS电路图如图3所示。

图3(2)实现的CMOS电路图如图4所示。图4(3)实现的CMOS电路图如图5所示。图511.出下列五种逻辑门中哪几种的输出可以并联使用。(1)TTL集电极开路门;(2)普通具有推拉式输出的TTL与非门;(3)TTL三态输出门;(4)普通CMOS门;

(5)CMOS三态输出门。解答上述五种逻辑门中,TTL集电极开路门、TTL三态输出门和CMOS三态输出门的输出可以并联使用。12.用与非门组成的基本R-S触发器和用或非门组成的基本R-S触发器在逻辑功能上有什么区别?解答与非门组成的基本R-S触发器功能为:R=0,S=0,状态不定(不允许出现);R=0,S=1,置为0状态;R=1,S=0,置为1状态;R=1,S=1,状态不变。或非门组成的基本R-S触发器功能为:R=0,S=0,状态不变;R=0,S=1,置为1状态;R=1,S=0,置为0状态;R=1,S=1,状态不定(不允许出现)。13.在图6(a)所示的D触发器电路中,若输入端D的波形如图6(b)所示,试画出输出端Q的波形(设触发器初态为0)。图6电路图及有关波形解答根据D触发器功能和给定输入波形,可画出输出端Q的波形如图7所示。

图714.已知输入信号A和B的波形如图8(a)所示,试画出图8(b)、(c)中两个触发器Q端的输出波形,设触发器初态为0。图8信号波形及电路解答根据给定输入波形和电路图,可画出两个触发器Q端的输出波形QD、QT如图9所示。

图9输出波形图15.设图10(a)所示电路的初始状态Q1=Q2=0,输入信号及CP端的波形如图10(b)所示,试画出Q1、Q2的波形图。图10电路及有关波形解答根据给定输入波形和电路图,可画出两个触发器输出端Q1、Q2的波形如图11所示。图11

16试用T触发器和门电路分别构成D触发器和J-K触发器。解答(1)采用次态方程联立法,分别写出T触发器和D触发器的次态方程如下:T触发器的次态方程:D触发器的次态方程:比较上述两个方程可得,据此可画出用T触发器和一个异或门构成D触发器的电路图如图12(a)所示。(1)采用次态方程联立法,分别写出T触发器和JK触发器的次态方程如下:T触发器的次态方程:JK触发器的次态方程:比较上述两个方程可得,据此可画出用T触发器和三个逻辑门构成JK触发器的电路图如图12(b)所示。图12

第四章1.分析图1所示的组合逻辑电路,说明电路功能,并画出其简化逻辑电路图。图1组合逻辑电路解答根据给定逻辑电路图写出输出函数表达式用代数法简化输出函数表达式由简化后的输出函数表达式可知,当ABC取值相同时,即为000或111时,输出函数F的值为1,否则F的值为0。故该电路为“一致性电路”。实现该电路功能的简化电路如图2所示。图22.分析图3所示的逻辑电路,要求:(1)指出在哪些输入取值下,输出F的值为1。

(2)改用异或门实现该电路的逻辑功能。图3组合逻辑电路解答分析给定逻辑电路,可求出输出函数最简表达式为当ABC取值000、011、101、110时,输出函数F的值为1;用异或门实现该电路功能的逻辑电路图如图4所示。图43.析图5所示组合逻辑电路,列出真值表,并说明该电路的逻辑功能。=1=1=1AWBCDXYZ...图5组合逻辑电路解答①写出电路输出函数表达式如下:

列出真值表如表1所示:表1ABCDWXYZABCDWXYZ00000001001000110100010101100111000000010011001001100111010101001000100110101011110011011110111111001101111111101010101110011000由真值表可知,该电路的功能是将四位二进制码转换成Gray码。4.设计一个组合电路,该电路输入端接收两个2位二进制数A=A2A1,B=B2B1。当A>B时,输出Z=1,否则Z=0。解答根据比较两数大小的法则,可写出输出函数表达式为根据所得输出函数表达式,可画出逻辑电路图如图6所示。图65.设计一个代码转换电路,将1位十进制数的余3码转换成2421码。解答设1位十进制数的余3码为ABCD,相应2421码为WXYZ,根据余3码和2421码的编码法则,可作出真值表如表2所示。表2

ABCDWXYZABCDWXYZ00000001001000110100010101100111dddddddddddd000000010010001101001000100110101011110011011110111110111100110111101111dddddddddddd由真值表可写出输出函数表达式为化简后可得:逻辑电路图如图7所示。图76.假定X=AB代表一个2位二进制数,试设计满足如下要求的逻辑电路:(1)Y=X2(2)Y=X3(Y也用二进制数表示。)解答

假定AB表示一个两位二进制数,设计一个两位二进制数平方器。由题意可知,电路输入、输出均为二进制数,输出二进制数的值是输入二进制数AB的平方。由于两位二进制数能表示的最大十进制数为3,3的平方等于9,表示十进制数9需要4位二进制数,所以该电路应有4个输出。假定用WXYZ表示输出的4位二进制数,根据电路输入、输出取值关系可列出真值表如表3所示。表3ABWXYZ000110110000000101001001由真值表可写出电路的输出函数表达式为根据所得输出函数表达式,可画出用与非门实现给定功能的逻辑电路图如图8所示。图8假定AB表示一个两位二进制数,设计一个两位二进制数立方器。由题意可知,电路输入、输出均为二进制数,输出二进制数的值是输入二进制数AB的立方。由于两位二进制数能表示的最大十进制数为3,3的立方等于27,表示十进制数27需要5位二进制数,所以该电路应有5个输出。假定用TWXYZ表示输出的5位二进制数,根据电路输入、输出取值关系可列出真值表如表4所示。表4ABTWXYZ0001101100000000010100011011由真值表可写出电路的输出函数表达式为

根据所得输出函数表达式,可画出用与非门实现给定功能的逻辑电路图如图9所示。图97.用与非门设计一个组合电路,该电路输入为1位十进制数的2421码,当输入的数字为素数时,输出F为1,否则F为0。解答设一位十进制数的2421码用ABCD表示,由题意可知,当ABCD表示的十进制数字为2、3、5、7时,输出F为1,否则为0。据此,可写出输出函数表达式为F(A,B,C,D)=∑m(2,3,11,13)+∑d(5~10)经化简变换后,可得到最简与非表达式为逻辑电路图如图10所示。图108.设计一个“四舍五入”电路。该电路输入为1位十进制数的8421码,当其值大于或等于5时,输出F的值为1,否则F的值为0。解答

根据题意,可列出真值表如表5所示。表5ABCDF00000001001000110100010101100111100010011010┇11110000011111d┇d由真值表可写出输出函数表达式为F(A,B,C,D)=∑m(5~9)+∑d(10~15)经化简变换后,可得到最简与非表达式为逻辑电路图如图11所示。

图119.设计一个检测电路,检测4位二进制码中1的个数是否为偶数。若为偶数个1,则输出为1,否则输出为0。解答假定采用异或门实现给定功能,设输入的四位代码用B4B3BB1表示,输出函数用F表示,根据题意和异或运算的规则,可直接写出输出函数表达式为逻辑电路图如图12所示。

图1210.设计一个加/减法器,该电路在M控制下进行加、减运算。当M=0时,实现全加器功能;当M=1时,实现全减器功能。解答设:A-----被加数/被减数B-----加数/减数C-----来自低位的进位输入/来自低位的借位输入F-----本位“和”/本位“差”G-----向高位的“进位”/向高位的“进位”根据题意,可列出真值表如表6所示。MABCFGMABCFG000000010010001101000101011001110010100110010111100010011010101111001101111011110011110110000011由真值表可写出输出函数表达式:M=0:F(A,B,C)=∑m(1,2,4,7)G(A,B,C)=∑m(3,5,6,7)M=1:F(A,B,C)=∑m(1,2,4,7)G(A,B,C)=∑m(1,2,3,7)经化简变换后,可得函数表达式如下:

根据逻辑表达式,可作出逻辑电路图如图13所示。图1311.在输入不提供反变量的情况下,用与非门组成电路实现下列函数:(1)(2)解答变换如下:逻辑电路图如图14所示。图14

变换如下:逻辑电路图如图15所示。图1512.下列函数描述的电路是否可能发生竞争?竞争结果是否会产生险象?在什么情况下产生险象?若产生险象,试用增加冗余项的方法消除。(1)(2)(3)解答因为逻辑表达式中没有以互补形式出现的逻辑变量,故不会发生竞争。因为逻辑表达式中有逻辑变量A以互补形式出现,故会发生竞争。但由于不论BCD取何值,表达式都不会变成或者的形式,所以不会产生险象。因为逻辑表达式中有逻辑变量A以互补形式出现,故会发生竞争。由于BC=11时,表达式会变成的形式,所以BC=11时会产生险象。增加冗余项后的表达式:

习题五1.简述时序逻辑电路与组合逻辑电路的主要区别。解答组合逻辑电路:若逻辑电路在任何时刻产生的稳定输出值仅仅取决于该时刻各输入值的组合,而与过去的输入值无关,则称为组合逻辑电路。组合电路具有如下特征:①由逻辑门电路组成,不包含任何记忆元件;②信号是单向传输的,不存在任何反馈回路。时序逻辑电路:若逻辑电路在任何时刻产生的稳定输出信号不仅与电路该时刻的输入信号有关,还与电路过去的输入信号有关,则称为时序逻辑电路。时序逻辑电路具有如下特征:电路由组合电路和存储电路组成,具有对过去输入进行记忆的功能;电路中包含反馈回路,通过反馈使电路功能与“时序”相关;电路的输出由电路当时的输入和状态(过去的输入)共同决定。2.作出与表1所示状态表对应的状态图。表1状态表现态y2y1次态y2(n+1)y1(n+1)/输出Zx2x1=00x2x1=01x2x1=11x2x1=10ABCDB/0B/0C/0A/0B/0C/1B/0A/1A/1A/0D/0C/0B/0D/1A/0C/0解答根据表1所示状态表可作出对应的状态图如图1所示。

图13.已知状态图如图2所示,输入序列为x=11010010,设初始状态为A,求状态和输出响应序列。图2解答状态响应序列:AABCBBCB输出响应序列:000010014.分析图3所示逻辑电路。假定电路初始状态为“00”,说明该电路逻辑功能。

图3解答根据电路图可写出输出函数和激励函数表达式为根据输出函数、激励函数表达式和JK触发器功能表可作出状态表如表2所示,状态图如图4所示。现态y2y1次态y2(n+1)y1(n+1)/输出Zx=0x=10001101100/000/000/000/001/111/011/011/1表2图4由状态图可知,该电路为“111…”序列检测器。5.分析图5所示同步时序逻辑电路,说明该电路功能。图5逻辑电路图

解答根据电路图可写出输出函数和激励函数表达式为根据输出函数、激励函数表达式和D触发器功能表可作出状态表如表3所示,状态图如图6所示。现态y2y1次态y2(n+1)y1(n+1)/输出Zx=0x=10001101101/011/001/000/111/100/011/001/0表3图6由状态图可知,该电路是一个三进制可逆计数器(又称模3可逆计数器),当x=0时实现加1计数,当x=1时实现减1计数。6.分析图7所示逻辑电路,说明该电路功能。图7逻辑电路图解答

根据电路图可写出输出函数和激励函数表达式为根据输出函数、激励函数表达式和JK触发器功能表可作出状态表如表4所示,状态图如图8所示。现态y2y1次态y2(n+1)y1(n+1)/输出Zx=0x=10001101101/010/011/000/111/100/001/010/1表4图8由状态图可知,该电路是一个模四可逆计数器。当x=0时实现加1计数,输出Z为进位信号;当x=1时实现减1计数,输出Z为借位信号。7.作出“0101”序列检测器的Mealy型状态图和Moore型状态图。典型输入、输出序列如下。输入x:110101010011输出Z:000001010000解答根据典型输入、输出序列,可作出“0101”序列检测器的Mealy型状态图和Moore型状态图分别如图9、图10所示.图9Mealy型状态图图10Moore型状态图8.设计一个代码检测器,该电路从输入端x串行输入余3码(先低位后高位)

,当出现非法数字时,电路输出Z为1,否则输出为0。试作出Mealy型状态图。解答根据题意,可作出Mealy型状态图如图11所示。图119.化简表5所示原始状态表。现态次态/输出Zx=0x=1ABCDEFGB/0A/0F/0A/0A/0C/0A/0C/0F/0G/0C/0A/1E/0B/1表5原始状态表解答根据状态等效判断法则,可利用隐含表求出状态等效对(A,B)(A,D)(B,D)(C,F)(E,G);最大等效类为{A,B,D}、{CF}、{E,G};令A,B,D}→a、{CF}→b、{E,G}→c,可得最简状态表如表6所示。

现态次态/输出Zx=0x=1abca/0b/0a/0b/0c/0a/1表6最简状态表10.化简表7所示不完全确定原始状态表。现态次态/输出Zx=0x=1ABCDED/dA/1d/dA/0B/1C/0E/dE/1C/0C/d表7原始状态表解答根据状态相容判断法则,可利用隐含表求出状态相容对(A,B)、(A,D)、(C,E)、(B,C)、(B,E);利用覆盖闭合表可求出最小闭覆盖为{A,B}、{A,D}、{B,C,E};令{A,B}→a、{A,D}→b、{B,C,E}→c,可得最简状态表如表8所示。现态次态/输出Zx=0x=1abcb/1b/0a/1c/0c/0c/1表811.按照相邻法编码原则对表9进行状态编码。

现态次态/输出Zx=0x=1ABCDA/0C/0D/1B/1B/0B/0C/0A/0表9状态表解答给定状态表中有4个状态,状态编码时需要两位二进制代码。根据相邻编码法,应满足AB相邻、BC相邻、CD相邻。设状态变量为y2y1,令y2y1取值00表示A,01表示B,10表示D.11表示C,可得二进制状态表如表10所示。现态y2y1次态y2(n+1)y1(n+1)/输出Zx=0x=10001111000/011/010/101/101/001/011/000/0表1012.分别用D、T、JK触发器作为同步时序电路的存储元件,实现表11所示二进制状态表的功能。试写出激励函数和输出函数表达式,比较采用哪种触发器可使电路最简。

现态y2y1次态y2(n+1)y1(n+1)/输出Zx=0x=10001111001/011/010/100/110/010/001/011/1表11状态表解答根据二进制状态表和D触发器激励表,可求出激励函数和输出函数最简表达式为根据二进制状态表和T触发器激励表,可求出激励函数和输出函数最简表达式为根据二进制状态表和JK触发器激励表,可求出激励函数和输出函数最简表达式为比较所得结果可知,采用JK触发器电路最简单。13.已知某同步时序电路的激励函数和输出函数表达式为

试求出改用JK触发器作为存储元件的最简电路。解答根据激励函数和输出函数表达式,可作出状态表如表12所示。现态y2y1次态y2(n+1)y1(n+1)输出Zx=0x=10001111000001111000100110011表12状态表根据二进制状态表和JK触发器激励表,可求出激励函数和输出函数最简表达式为根据激励函数和输出函数最简表达式,可作出逻辑电路图如图12所示。图1214设计一个能对两个二进制数X2=x21,x22,…,x2n和X1=x11,x12,…,x1n

进行比较的同步时序电路,其中,X2、X1串行地输入到电路的x2、x1输入端。比较从x21、x11开始,依次进行到x2n、x1n。电路有两个输出Z2和Z1,若比较结果X2>X1,则Z2为1,Z1为0;若X2X1,根据题意,可作出最简状态图如图13所示,相应状态表如表13所示。图13现态次态输出Z2Z1x2x1=00x2x1=01x2x1=10x2x1=11ABCABCBBCCBCABC110110表13给定状态表中有3个状态,状态编码时需要两位二进制代码。设状态变量为y2y1,令y2y1取值00表示A,01表示B,10表示C.

11为多余状态,令多余状态下输入x2x1为01进入B,为10进入C,为00或11进入A,可得二进制状态表如表14所示。现态y2y1次态y2(n+1)y1(n+1)输出Z2Z1x2x1=00x2x1=01x2x1=10x2x1=11000110110001100001011001100110100001100011011000表14根据二进制状态表和JK触发器激励表,可求出激励函数和输出函数最简表达式为根据激励函数和输出函数最简表达式,可画出逻辑电路图如图14所示。图14

15.用T触发器作为存储元件,设计一个采用8421码的十进制加1计数器。解答根据题意,设状态变量用y3y2y1y0表示,可直接作出二进制状态图如图15所示,相应状态表如表15所示。图15表15y3y2y1y0y3(n+1)y2(n+1)y1(n+1)y0(n+1)00000001001000110100010101100111100010011010┋11110001001000110100010101100111100010010000dddd┋dddd根据二进制状态表和T触发器激励表,可求出激励函数最简表达式为根据激励函数最简表达式,可画出逻辑电路图如图16所示。

图16'

您可能关注的文档

- 《数字电子技术基础》习题答案(王毓银)版的.doc

- 《数字电子技术基础》国防科技版习题答案.docx

- 《数字电子技术基础》第3版(余孟尝)高等教育出版社_课后答案.doc

- 《数字电子技术基础》第3版(余孟尝)高等教育出版社_课后答案.pdf

- 《数字电子技术基础简明教程(第三版)》余孟尝主编_答案.doc

- 《数字电子技术基础简明教程(第三版)》余孟尝答案.pdf

- 《数字电子技术基础简明教程(第三版)答案》.pdf

- 《数字电路-分析与设计》1--10章习题及解答(部分)_北京理工大学出版社.doc

- 《数字通信原理》习题及解答20120371.pdf

- 《数学物理方程》第三版习题答案.pdf

- 《数据与计算机通信》第七版课后习题答案.doc

- 《数据库原理与应用》(孟凡荣 闫秋艳)课后习题答案.doc

- 《数据库原理与应用》课后习题答案.doc

- 《数据库原理与应用》课后习题答案1至5章 孟凡荣主编.doc

- 《数据库原理及应用》邮电二版 习题参考答案(总体).doc

- 《数据库系统及应用》习题解答.doc

- 《数据库系统概论》-答案第四版.pdf

- 《数据库系统概论》各章复习题及答案(2013给学生).doc

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明