- 1.19 MB

- 2022-04-22 11:31:16 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

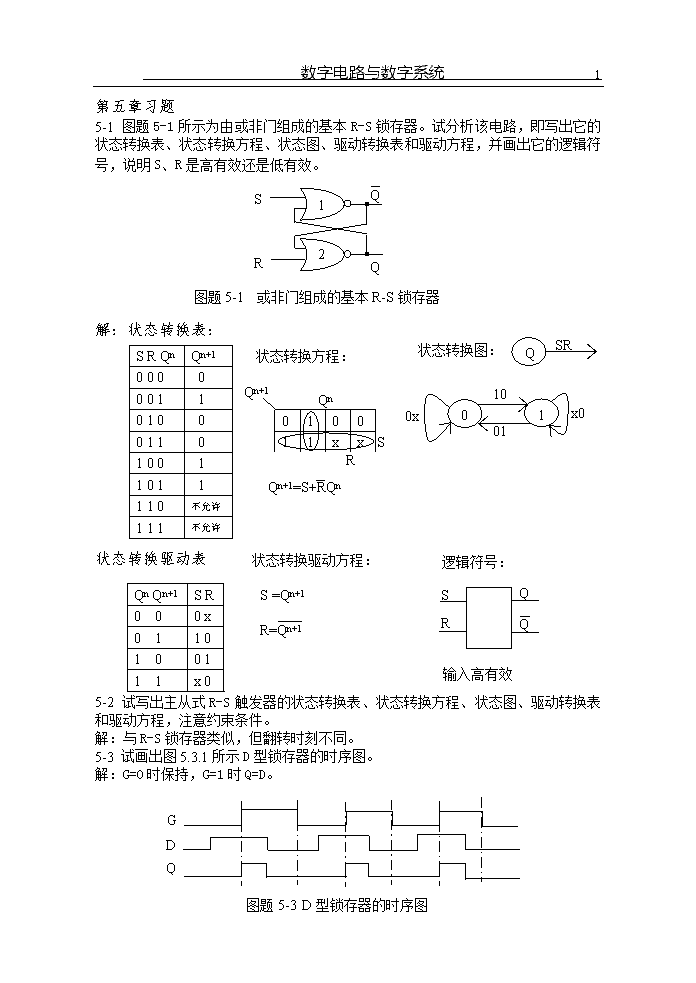

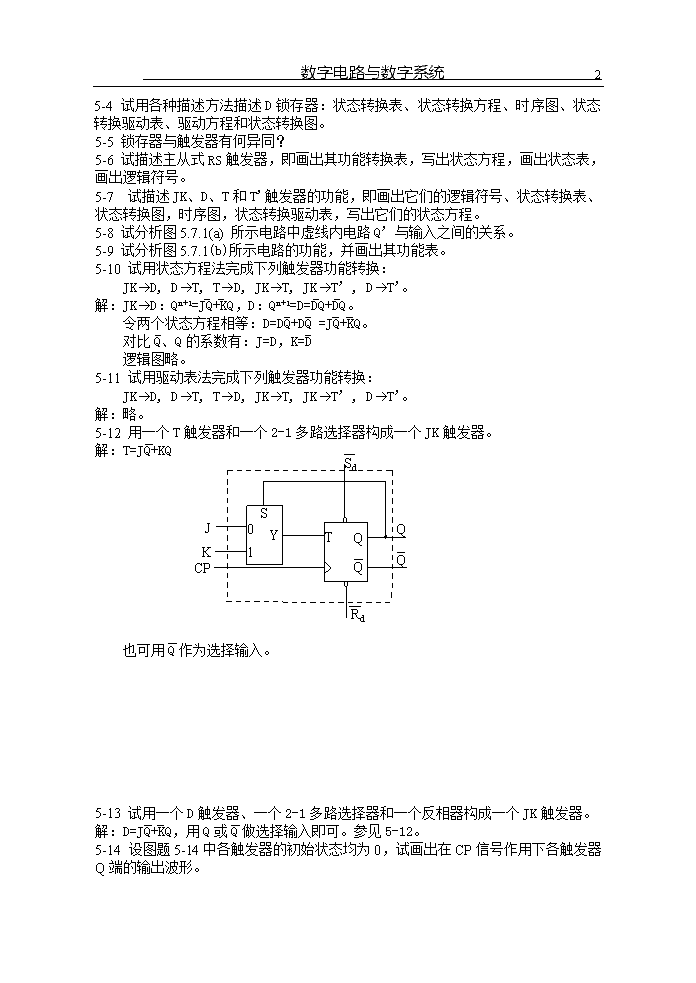

'数字电路与数字系统33第五章习题5-1图题5-1所示为由或非门组成的基本R-S锁存器。试分析该电路,即写出它的状态转换表、状态转换方程、状态图、驱动转换表和驱动方程,并画出它的逻辑符号,说明S、R是高有效还是低有效。图题5-1或非门组成的基本R-S锁存器QSRQ12状态转换图:0110QSR010xx0解:状态转换表:状态转换方程:010011xxSRQnQn+1Qn+1=S+RQnSRQnQn+1000000110100011010011011110不允许111不允许S=Qn+1R=Qn+1状态转换驱动方程:RSQQ逻辑符号:输入高有效状态转换驱动表QnQn+1SR000x0110100111x05-2试写出主从式R-S触发器的状态转换表、状态转换方程、状态图、驱动转换表和驱动方程,注意约束条件。解:与R-S锁存器类似,但翻转时刻不同。5-3试画出图5.3.1所示D型锁存器的时序图。解:G=0时保持,G=1时Q=D。GDQ图题5-3D型锁存器的时序图

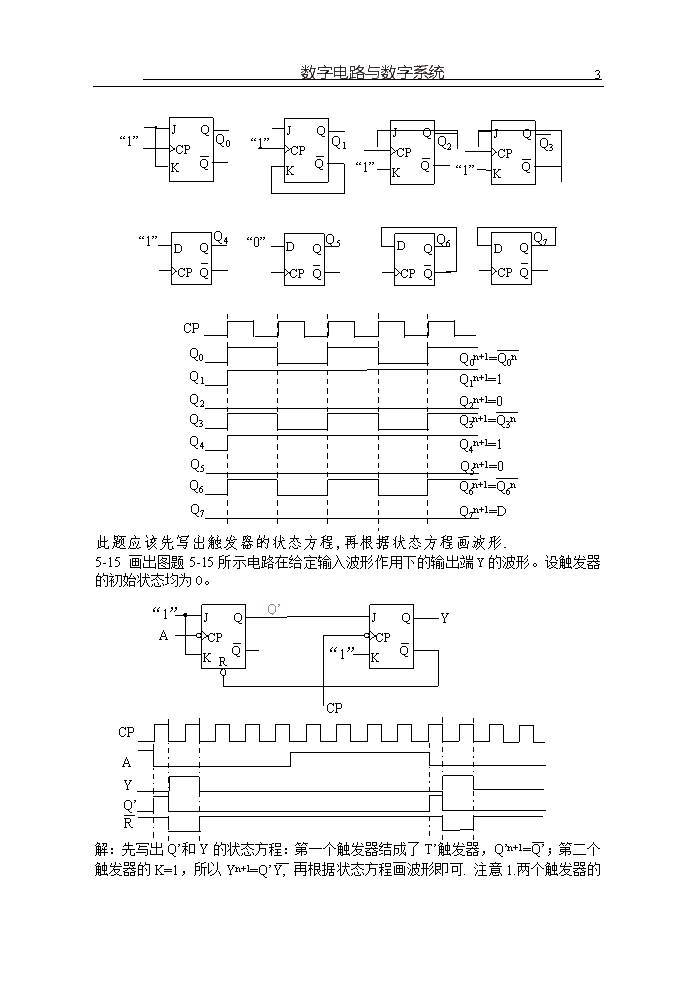

数字电路与数字系统335-4试用各种描述方法描述D锁存器:状态转换表、状态转换方程、时序图、状态转换驱动表、驱动方程和状态转换图。5-5锁存器与触发器有何异同?5-6试描述主从式RS触发器,即画出其功能转换表,写出状态方程,画出状态表,画出逻辑符号。5-7试描述JK、D、T和T"触发器的功能,即画出它们的逻辑符号、状态转换表、状态转换图,时序图,状态转换驱动表,写出它们的状态方程。5-8试分析图5.7.1(a)所示电路中虚线内电路Q’与输入之间的关系。5-9试分析图5.7.1(b)所示电路的功能,并画出其功能表。5-10试用状态方程法完成下列触发器功能转换:JKàD,DàT,TàD,JKàT,JKàT’,DàT’。解:JKàD:Qn+1=JQ+KQ,D:Qn+1=D=DQ+DQ。令两个状态方程相等:D=DQ+DQ=JQ+KQ。对比Q、Q的系数有:J=D,K=D逻辑图略。5-11试用驱动表法完成下列触发器功能转换:JKàD,DàT,TàD,JKàT,JKàT’,DàT’。解:略。5-12用一个T触发器和一个2-1多路选择器构成一个JK触发器。QQTRdSdJKCPQQ01YS解:T=JQ+KQ也可用Q作为选择输入。5-13试用一个D触发器、一个2-1多路选择器和一个反相器构成一个JK触发器。解:D=JQ+KQ,用Q或Q做选择输入即可。参见5-12。5-14设图题5-14中各触发器的初始状态均为0,试画出在CP信号作用下各触发器Q端的输出波形。

数字电路与数字系统33“1”“1”Q3Q2Q1Q0JDKDCPDQDQDJDKDCPDQDQDJDKDCPDQDQDJDKDCPDQDQD“1”“1”“0”“1”Q7Q6Q5Q4QDCPDQDQDDQDQDCPDQQCPQCPCPQ0Q1Q0n+1=Q0nQ1n+1=1Q3Q2Q2n+1=0Q3n+1=Q3nQ4Q4n+1=1Q5Q5n+1=0Q6Q6n+1=Q6nQ7Q7n+1=D此题应该先写出触发器的状态方程,再根据状态方程画波形.5-15画出图题5-15所示电路在给定输入波形作用下的输出端Y的波形。设触发器的初始状态均为0。JDKDCPDRDQDQDJDKDCPDQDQD“1”“1”ACPYCPAYQ’Q’R解:先写出Q’和Y的状态方程:第一个触发器结成了T’触发器,Q’n+1=Q’;第二个触发器的K=1,所以Yn+1=Q’Y,再根据状态方程画波形即可.

数字电路与数字系统33注意1.两个触发器的时钟;2.第一个触发器的清0信号;3.画时序图时,将Q’作为辅助变量画出。第三章思考题与习题解答+12V1kWb=50+6V50kW+5V3kW30kWb=20·+15V2kWb=3051kW15kW-6V(a)(b)(c)图题3-13-1判断图题3-1所示电路中三极管的工作状态?解:(a)放大工作状态(b)饱和工作状态(c)截止工作状态3-2怎样判断与“非门”能带动同类型门的个数?解:将TTL“与非”门的输出端能驱动同类“与非”门的最大数目称为扇出系数,用表示。由于门电路的驱动能力在输出高电平和低电平时是不同的,可近似计算如下:故一般的74系列TTL“与非”门的扇出系数。3-3“与非”门三个输入端的波形如图题3-3所示,画出其输出端的波形。ABACYBCY图题3-3

数字电路与数字系统333-4试分别指出TTL“与非”门的下列接法会造成什么后果,并说明原因:⑴输出端接地;⑵输出端接+5V电源;⑶两个普通“与非”门的输出端短接。解:⑴无论输出高、低电平,输出始终为低电平。则无法实现“与非”逻辑功能。⑵无论输出高、低电平,输出始终为高电平。则无法实现“与非”逻辑功能。⑶一般的TTL“与非”门是不允许将输出端直接连接在一起的。因为,TTL“与非”门的输出电阻很小,不论在“与非”门导通还是截止状态,其输出电阻都在几欧姆到几十欧姆之间,若将它们的输出端直接相连,则当一个“与非”门输出高电平而另一个“与非”门输出低电平时,从电源到地之间则会形成一条低阻通路,将有一个很大的电流从截止“与非”门的管流到导通“与非”门的管,这个电流不仅会使导通“与非”门的输出低电平抬高,甚至会因功耗过大而把两个“与非”门都损坏。3-5有两个相同型号的TTL“与非”门,对它们进行测试的结果如下:⑴甲的开门电平为1.4V,乙的开门电平为1.5V;⑵甲的关门电平为1.0V,乙的关门电平为0.9V。试问在输入相同高电平时,哪个抗干扰能力强?在输入相同的低电平时,哪个抗干扰能力强?解:高电平噪声容限:甲的开门电平小,所以甲在输入高电平时的抗干扰能力强;低电平噪声容限:甲的关门电平大,所以甲在输入低电平时的抗干扰能力强。3-6试说明下列各种门电路中哪些可以将输出端并联使用(输入端的状态不一定相同)。⑴具有推拉式输出级的TTL电路;⑵TTL电路的OC门;⑶TTL电路的TS门;⑷普通的CMOS门;⑸漏极开路输出的CMOS门;⑹CMOS电路的TS门。

数字电路与数字系统33解:⑵TTL电路的OC门;⑸漏极开路输出的CMOS门;可以将输出端并联使用,并实现“线与”逻辑功能。3-7计算图题3-7电路中上拉电阻RL的阻值范围。其中G1、G2、G3是74LS系列OC门,输出管截止时的漏电流,输出低电平时允许的最大负载电流。G4、G5、G6为74LS系列“与非”门,该门的输入电流为、。要求OC门的输出高、低电◊◊···G1G2G3G4G5G6RLUCC=5V图题3-7◊平应满足、。解:3-8计算图题3-8电路中的反相器GM能驱动多少个相同类型的反相器?要求GM输出的高、低电平符合,。所有的反相器均为74LS系列TTL电路,输入电流,,时输出电流的最大值,时输出电流的最大值为。(GM的输出电阻可忽略不计)图题3-8GM··G1G2GnUI解:

数字电路与数字系统333-9OC门是具有什么逻辑功能的门电路?它有什么特点和用途?解:OC门是集电极开路的“与非”门,是把“与非”门电路的推拉式输出级改为三极管集电极开路输出。所以具有“与非”门的逻辑功能。OC门只有在外接上拉电阻和电源时才能正常工作,而电源的电压既可与门电路本身的电压相同,也可以不同。OC门的最大特点是允许将输出端直接连在一起,以实现“线与”功能。UIHY3·图题3-10UDD10kWY2UDD10kWY1·3-10图题3-10中均为CD4000系列CMOS门电路,试指出各门电路的输出是高电平还是低电平?解:为高电平;为低电平;为低电平。[注:只有TTL门电路当输入端通过一个大电阻(10KW)接地时,才会出现反电平现象。]3-11用三态门实现“线与”(即总线结构)时,为什么要求在任何时间只能有一个门工作?解:三态门的输出结构与普通门电路一样,例如TTL三态“与非”门,仍然是推拉式输出结构,若在一时刻,两个门同时工作,其输出电平又不一样,从电源到地之间则会形成一条低阻通路,将有一个很大的电流从截止的TTL三态“与非”门的管流到导通TTL三态“与非”门的管,这个电流不仅会使导通TTL三态“与非”门的输出低电平抬高,甚至会因功耗过大而把两个TTL三态“与非”门都损坏。3-12图题3-12中给出TTL系列门电路的三种逻辑图,试改正图中错误,使之满足输出函数表达式。

数字电路与数字系统33UCCAY1BCD··B0Y3·AY20图题3-12AY2“1”AY1BCD解:B0Y33-13在图题3-13中是TTL门电路驱动CMOS门电路的实例。已知TTL“与非”门在时的最大输出电流为,输出端的管截止时有的漏电流。CMOS“或非”门的输入电流很小,可忽略。现要求加到CMOS“或非”门输入端的电压满足,该电路的电源电压为。试求上拉电阻的取值范围。UCCAB··RL图题3-13Y1Y2··TTLCMOS

数字电路与数字系统33解:3-14TTL“与非”门输出端若接CMOS“与非”门负载时,需注意什么问题?反之,CMOS“与非”门输出端若接TTL“与非”门负载时,又需注意什么问题?解:由TTL“与非”门输出驱动CMOS“与非”门负载时,需注意TTL“与非”门与CMOS“与非”门之间的电平配合问题。因为一般情况下,CMOS“与非”门的电源较高,这时:1、接上拉电阻;2、选用专用的CMOS电平移动器。由CMOS“与非”门输出驱动TTL“与非”门负载时,需注意CMOS门的驱动能力不能适应TTL门的要求,即常有的问题。这种情况下,1、并联同一封装内的CMOS门,以增大;2、选用CMOS驱动器;3、在CMOS门的输出接一个开关晶体管。第六章习题6-1略。6-2此时相当于触发器在前级Q的上沿翻转,所以是减法计数器。6-3异步可逆计数器。UP/DOWN=0时,加法计数;UP/DOWN=1时,减法计数6-4该电路为异步置位法任意模计数器,置位状态为4(M-1),所以该计数器的模M=5计数器;时序图略。有效状态循环:0、1、2、3、7、0;4,6为过渡状态,其次态为7;5的次态为6。由于由状态011(M-2)到100(M-1)时,Q1、Q0由1变0,所以这两个Q端上会出现毛刺。6-5用4位T’触发器;因用复位法,故用状态1010清0(R=Q3Q1)。有效状态循环为0~9;10、11、14、15均为过渡状态,其次态均为0;12的次态是13,13的次态是14;毛刺出现在Q1上。6-6用4位T’触发器;因用置位法,故用状态1001置位(S=Q3Q1Q0)。有效状态循环为0~8,15;9、13为过渡状态,其次态均为15;10à11à12à13à15,14à15;无毛刺。6-7用4位T’触发器;因用置位法,故用状态1101置位(S=Q3Q2Q1Q0)。有效状态循环为0~12,15;13为过渡状态,其次态为15;14à15;毛刺出现在Q0上。6-8~6-11略。

数字电路与数字系统336-12电路由T触发器组成;CPi=CP,T0=1,T1=Q0,T2=Q1Q0,所以它是同步二进制减法计数器。时序图略。6-13该题未要求是同步还是异步计数器,可以两种都做,也可以只做一种。异步:先将JK转换为T’,即令J=K=1;同步:先将JK转换为T,即令J=K=T;M=8,需要3个触发器;异步可逆、同步可逆,参见图6.39;6-14异步计数器电路简单,速度慢;同步计数器则相反。6-15可能产生毛刺,也可能不产生。如果产生毛刺,则它(们)出现在由M-2到M-1时由1变0的QA、QD端上和/或由M-2到M-1时由0变1的QB、QC端上。6-16先分别将‘290接为8421和5421计数器,再分别用M=7(QDQCQBQA=0111)8421和(QAQDQCQB=1010)5421复位即可,应特别注意高低位的顺序。波形图和状态图略。QAQBQCQD74LS290ABR01R02S91S92QAQBQCQD74LS290ABS91S92R01R02CP8421模7计数器CP5421模7计数器6-17先分别将‘290接为8421和5421计数器,再分别用M-1=6(QDQCQBQA=0110)8421和(QAQDQCQB=1001)5421置位即可,应特别注意高低位的顺序。波形图和状态图略。QAQBQCQD74LS290ABS91S92R01R02QAQBQCQD74LS290ABR01R02S91S92CP8421模7计数器CP5421模7计数器

数字电路与数字系统336-18不可以。如果这样,置9信号永远有效,电路一直在状态9上。6-19图T6-19有错,先将图改为下图。QAQBQCQD74LS290ABR01R02S91S92QAQBQCQD74LS290ABR01R02S91S92CP复位法M1=6置位法M2=6左边片复位法,M1=6;右边片置位法,M2=6;M=M1M2=36。6-201.先8421级联;用复位法:(72)10=(01110010)8421时复位即可。用74LS290实现8421码模72计数器QAQBQCQD74LS290(L)ABR01R02S91S92CPQAQBQCQD74LS290(H)ABR01R02S91S922.先5421级联;用复位法:(72)10=(10100010)2时复位即可。QAQBQCQD74LS290(十位)ABR01R02S91S92用74LS290实现5421码模72计数器QAQBQCQD74LS290(个位)ABR01R02S91S92CP

数字电路与数字系统331.(72)10=(8*9)10=(1000*1001)8421,先分别用复位法作8421接法M1=8和M2=9两个计数器,然后将它们级联即可。用74LS290实现M=8*9=72计数器QAQBQCQD74LS290(M=9)ABR01R02S91S92CPQAQBQCQD74LS290(M=8)ABR01R02S91S926-2174LS161:LD=1,无效;P=T=1,有效;因是异步清0,M=14时清0,即令CLR=QDQCQB;有毛刺;74LS163:LD=1,无效;P=T=1,有效;因是同步清0,M-1=13时清0,即令CLR=QDQBQA;无毛刺;画QD、QC、QB、QA和RCO对应CP的同步波形时应画至少一个计数周期,并特别注意毛刺。波形图略。6-22可以。预置0即可实现同步置0。6-23由于74LS161/163均为同步预置,故用二者实现时电路完全一样:令CLR=1,无效;P=T=1,有效;LD=RCO;预置数为9的补码,即16-9=7即可。波形图略。6-24应从RCO引出,此时不管分频比为多少,分频关系都是正确的。6-25画出状态顺序表或状态图即可。RCOQAQBQCQDPLDTCLRABCDRCOQAQBQCQDPLDTCLRABCD(b)(a)RCOQAQBQCQDPLDTCLRABCDCLK74LS163/16111CP011CLK74LS163/16111CPRCOQAQBQCQDPLDTCLRABCDCLK74LS163/16111CP001CLK74LS163/16111CP对于图(a),只要注意QB=0时预置,并且DCBA=QD110即可。QDQCQBQA0000011001111000000101010100100110101011001100101111111011011100

数字电路与数字系统33由状态图知,这是模6计数器。对于图(b),只要注意QC=0时预置,并且DCBA=QD100即可。QDQCQBQA1011101001001000000101010000100101100111001100101111110011011110由状态图知,这是模10计数器。该电路设计巧妙,QD均为占空比为50%的方波。RCOQAQBQCQDPLDTCLRABCDCLK74LS163(2)1RCOQAQBQCQDPLDTCLRABCDCLK74LS163(1)11CP6-26该图漏了一条线,见下图。为什么?不能将图中的74LS163换成74LS161,因为74LS163是同步清0,而74LS161是异步清0,若更换芯片会改变计数器的模。6-27①先将两片74LS161级联成8位计数器;令P、T有效;令CLR无效;LD=RCO;(D7~D0)=(256-210)10=(46)10=(00101110)2即可。②先将两片74LS161级联成8位计数器;令P、T有效;令LD无效;由于‘161是异步清0,故用(210)10=(11010010)2清0,即令CLR=Q7Q6Q4Q1即可。③210=14*15,参见图6.28。④210=14*15,参见6-26图(注意漏了一条线,见答案。6-28略。6-29解:Sin=Q3⊕Q2,状态顺序为Q3Q2Q1Q0,0000à0000;0001à0010à0100à1001à0011à0110à1101à1010à0101à1011à0111à1111à1110à1100à1000à0001。同学们需画出状态表和状态图。

数字电路与数字系统33这是m序列发生器,输出序列为00010011010111100016-30能。令CLR=1无效;LD=0,有效;左移:A=QB,B=QC,C=QD,D=Sin;右移:B=QA,C=QB,D=QC,A=Sin。6-31,6-32有兴趣的同学可做,不要求。第九章习题9-1答:所有Di均为1时电流最大,为IVREFMAX=VREF(1/23+1/22+1/21+1/20)/R=(1+2+4+8)VREF/23R=15VREF/8R=1.875VREF/R=1.875mA;PVREFMAX=VREFIVREFMAX=5*1.875=9.375mW。9-2解:ΔV=VREF/16=0.3125V;Vomax=15ΔV=4.6875V;当D3D2D1D0=1001时,Vo=9ΔV=2.8125V。9-3答案:VO=VREF/28∑Di2i,i=0~7。9-4解:T型:IVREF=VREF/3R∑Di;PVREF=VREF2/3R∑Di;PVREFMAX=n*VREF2/3R;PVREFMIN=0;PVREF与位数、输入数据有关。倒T型:IVREF=VREF/R,PVREF=VREF2/R,与输入数据D无关。9-5解:由2n>=Vomax/ΔV=5V/1mV=5000,得n=13;由Vomax=(2n-1)VREF/2n,得VREF=213Vomax/(213-1)≈Vomax=5V;如果取n=13,VREF=5V,则:ΔV=VREF/213=5/8192=0.0006<1mV,Vomax=(213-1)VREF/213=8191*5/8192=4.99938V,满足设计要求。9-6解:该图中电阻网络作为反馈电阻,故增益表达式为:AV=-2n/Σ(2i×Di)①当D9-D0=1000000000时,AV=-210/29=-2;②当增益为5时,令AV=-2n/Σ(2i×Di)=-213/X,得X=-213/-5=1638.4,取X=(1638)10=(0011001100110)2实际增益为AV=-213/1638=5.0019-7解:1.74LS194构成m序列发生器,其输出状态Q3Q2Q1Q0的顺序为0001,0010,0100,1001,0011,0110,1101,1010,0101,1011,0111,1111,1110,1100,1000;2.AD7520构成4位DAC,其输出为VO=-VREF/24∑Di*2i=-5/16∑Di*2i=-0.3125∑Di*2i;3.由于Q0接在D9上,所以DAC输入数据D9D8D7D6的顺序为Q0Q1Q2Q3的顺序:1000,0100,0010,1001,1100,0110,1011,0101,1010,1101,1110,1111,0111,0011,0001;

数字电路与数字系统33246810121416246tVO…4.所以波形图为:9-2解:此题与9-5类似:n=13,VREF=5V;实际分辨率为0.61mV。9-3在图9.16中,如果分压器中最下面一个电阻的阻值也为R,其它部分相同。试列出类似表9.1的输入-输出关系表,并指出量化误差的大小。解:此时各分压值分别为1/8VREF,2/8VREF,…7/8VREF;列表如下:输入电压Vi量化电平比较器输出编码器输出C7C6C5C4C3C2C1D2D1D0[0,VREF/8)1/16VREF0000000000[VREF/8,2VREF/8)3/16VREF0000001001[2VREF/8,3VREF/8)5/16VREF0000011010[3VREF/8,4VREF/8)7/16VREF0000111011[4VREF/8,5VREF/8)9/16VREF0001111100[5VREF/8,6VREF/8)11/16VREF0011111101[6VREF/8,7VREF/8)13/16VREF0111111110[7VREF/8,VREF)15/16VREF1111111111如果按表中所列取量化电平,则量化误差为1/16VREF。9-4解:因为VREF=5V,所以各分压值分别为1/3V,3/3V,5/3V,7/3,9/3V,11/3V,13/3V;Vi=2.36V落在区间(7/3,9/3),输出编码值为100,对应的量化值为8/3V,此时的量化误差为|2.36-8/3|=0.3067V。9-5解:如果只做一次ADC转换,10位逐次逼近式ADC完成一次转换需要12个时钟周期;如果连续进行ADC转换,每次转换又需要11个时钟周期?9-6解:fADC>(2~5)fi,取fADC=3fi=30KHz;连续ADC时,fCP=(n+1)fADC=11fADC;所以fCPMIN=11fADC=11*30KHz=330KHz。9-7解:10位双积分式ADC转换一次最多用时2n+1tCP;设取样频率取fS=3fi=3KHz,则该ADC的最低时钟频率为fCP=2n+1fS=210+1*3KHz=6144KHz。第八章7-14a、根据题目,为11序列检测。设:初始状态,电路未收到一个有效1;

数字电路与数字系统33:收到一个1后的状态;注:X表示任意。:连续收到两个1后的状态。0/01/00/01/1X/0D2D1C、“101”检测器,不重叠。S00/01/00/0S1S20/01/0S30/01/01/1:初始状态;:输入序列为“1”;:输入序列为“10”;:输入序列为“101”;8-3图8.38所示的环形振荡器中,RC的作用是:增加门的传输延持时间;有助于获得较低的振荡频率;通过改变R和C的数值,可以调节输出信号的频率。调节范围受门电路输出高电平和阈值的限制。若设:门为TTL,的作用是,防止反相器的输入端钳位二极管的电流过大所串接的保护电阻。8-4

数字电路与数字系统33uI0.01mFUCC···555534862718-5①回差电压:②当时:17268435555···UCC0.01mFR1uOR2C··8-6占空比=上式说明,图1所示电路输出脉冲的占空比始终大于50%,所以改为图2,这时由于图1接入二极管D1和D2,充电电流仅流过R1,放电电流仅流过R217268435555···UCC0.01mFR1uOR2C···

数字电路与数字系统33占空比:图2若取,电路振荡周期为:输出脉冲的幅度:左右。8-8⑴电路的原理:j稳定状态当触发正脉冲未到时,为“0”,为“1”,即,G2门的两个输入端分别为“0”和“1”,故其输出为“1”态,即。这就是稳定状态。k暂稳状态当触发正脉冲到时,变为“1”,故变成“0”。因为电容上的电压不能突变,仍为“1”。这时G2门的两个输入端电压会同时高于门电路的阈值电压,其输出,电路开始进入暂稳态。0tUitt000UO1UCUO2tUTtwt0UOtp与此同时,电容也将开始放电,其放电回路为:从地。随着电容的放电,使得随时间按指数规律逐渐下降,当降至TTL管的阈值电压时,又变成“1”,即,暂稳态结束。l恢复过程当输入正脉冲消失,即由“1”变为“0”时,立即由“0”变成“1”

数字电路与数字系统33,这时电容又开始充电直到充满稳定,电路又恢复到原稳定状态,即。门G3的作用是改善输出波形。⑵波形如图输出脉冲的宽度:式中该电路可正常工作。8-10⑴电路的原理:j稳定状态当触发信号为高电平时,G2门的输入通过接地,G2门输出为“1”态,即高电平。G1门的两个输入均为高电平,为低电平,,这就是稳定状态。k暂稳状态当触发负脉冲到时,变成“1”。因为电容上的电压不能突变,,使G2门的输出为低电平,该低电平反馈到G1门的输入端,此时即使的负触发脉冲消失,仍维持高电平,电路开始进入暂稳态。0tUItt000UAUO1UI1tUTtwt0UO与此同时,电源由G1门的导通管给电容充电,随着电容的充电,随时间按指数规律逐渐下降,当降至TTL管的阈值电压时,又变成“1”,暂稳态结束。l恢复过程当输入负脉冲消失,这时电容将通过放电直到稳定,电路又恢复到原稳定状态,即。

数字电路与数字系统33和构成微分电路,防止输入触发脉冲太宽。⑵波形如图17268435555···UCC0.01mFRuOC·ui·8-12要求:1-10s当取时:用可变电阻器可实现。4-5设计一个编码器,输入是表示1位十进制数的状态信号,输出为余3循环码,用“与非”门实现。真值表输入输出(余3循环码)十进制数DCBA01234567890010011001110101010011001101111111101010解:编码器的真值表如右所示。由表可知:DCBA0123456789根据D、C、B、和A的逻辑表达式,画出编码器的逻辑图如下:

数字电路与数字系统334-7试用3-8线译码器74LS138组成一个1-8线数据分配器。70123456138E3A2A1A0E2E1Y7Y6Y5Y4Y3Y2Y1Y0S2S1S0D+5V解:令:D为数据输入端;S2S1S0为数据选择控制输入端(S0为最低有效位)。逻辑图如右所示:4-10试将8-1MUX扩展成16-1MUX。解:S2S1S0S2S1S08-1MUX01234567YE(1)S3S2S1S08-1MUX01234567YE(2)F0123456789101112131415逻辑图如下所示(S3是选择控制端的最高有效位):

数字电路与数字系统334-12试用2-4线译码器(输出低有效)和2输入“与非”门实现1位数码比较器。解:m0m1S0m2S1m32-4译码器Y2(A=B)Y1(AB)“1”BA1位数值比较器的输出函数逻辑表达式如下:,,。4-13试用4位加法器74LS283和门电路构成8位二进制数的求补电路。解:“1”74LS283B3B2B1B0C3C2C1C074LS283B7B6B5B4C7C6C5C48位二进制数的求补电路如下:

数字电路与数字系统334-14用4位加法器74LS283实现下述电路:1.8421BCD码至余3BCD码的转换器;74LS283“1”DCBA解:8421BCD码加上“0011”即成为余3BCD码。实现电路如右所示:第七章部分习题7-7解:解:(c)(1)输出是输入和Q的函数Z=F(X,Q),所以是米里型时序电路;(2)输出方程:Z=X⊕Q;驱动方程:T=Z=X⊕Q;次态方程(状态方程):Qn+1=T⊕Q=X⊕Q⊕Q=XXQQn+1Z00000101101111100100/01/110/11/0Qn+1/ZQX(3)

数字电路与数字系统33011/01/10/10/0(4)(5)波形图:CPXQZ当输入X=000101011,初态为0时Q=0000101011Z=000111110如果使输入与时钟同步,则输出无毛刺。7-8解:(a)1.米里型2.输出方程:Z=XQ1Q0;驱动方程:J1=X,K1=X+Q0=XQ0J0=XQ1,K0=X次态方程(状态方程):Q1n+1=J1Q1+K1Q1=XQ1+XQ0Q1=X(Q1+Q0)Q0n+1=J0Q0+K0Q0=XQ1Q0+XQ0=X(Q1+Q0)00/010/000/011/000/011/100/001/00(Q1Q0)n+1/ZXQ1Q0100011110001/01/00/00/01001111/01/10/0Q1Q0X/Z3.4.7-12某同步时序电路的逻辑方程如下:驱动方程:,;输出方程:。要求:

数字电路与数字系统33解:1.同步时序电路的逻辑图示于图,这是米里型的状态机。ClockCKT0Q0Q0ZXCKT1Q1Q12.(a)状态方程:Q1n+1=T1⊕Q1=X⊕Q0⊕Q1Q0n+1=T0⊕Q0=XQ1⊕Q0=XQ1Q0+XQ0+Q1Q0(b)状态转换表:(c)状态转换图:nn+1ZXQ1Q0Q1Q0000000001110010100011010100111101001110000111110000/01/10/00/01101101/11/01/0Q1Q0X/Z0/0S0/0110S1/0S2/10x7-15解:(a)“11”检测器,不重叠。S0:初始状态,输出0;S1:输入一个“1”,输出0;S2:输入两个“1”,输出1;S0/0010S1/0S2/001S3/1011(b)“101”检测器,可重叠。S0:初始状态;S1:输入序列为“1”;S2:输入序列为“10”;S3:输入序列为“101”;

数字电路与数字系统33(c)(d)略7-34“011”序列检测器,可重叠。S00/00/01/0S1S3/01/00/0S21/10/01/0解:1.采用D触发器,用米里型同步状态机实现;(a)米里型状态图:S0:初始状态;S1:输入序列为“0”;S2:输入序列为“01”;S3:输入序列为“011”;(b)状态表(两种画法均可):SnX=0X=1Sn+1/ZSn+1/ZS0S1/0S0/0S1S1/0S2/0S2S1/0S3/1S3S1/0S0/0XSnSn+1/Z0S0S1/00S1S1/00S2S1/00S3S1/01S0S0/01S1S2/01S2S3/11S3S0/0(c)状态化简:由观察法知,S0、S3等价。简化状态图为:S00/01/0S10/0S21/10/01/0SnX=0X=1Sn+1/ZSn+1/ZS0S1/0S0/0S1S1/0S2/0S2S1/0S0/1(d)状态化简后的状态表:(e)状态分配:

数字电路与数字系统33根据状态分配原则1,次状态对相同时,原状态对相邻:S0、S2应安排相邻;根据状态分配原则2,一个状态在输入相邻时的次态相邻:S0、S1,S1、S2应分别安排相邻;根据状态分配原则3,输入相同时输出也相同的状态相邻:S0、S2,S1、S2应分别安排相邻。据此,安排相邻关系如下:Q0S0S1S2Q1状态分配后的状态表为:(Q1Q0)nX=0X=1(Q1Q0)n+1/Z(Q1Q0)n+1/Z0011/000/001xx1111/010/01011/000/1(e)画K-圈:黑色为Q1,红色为Q0,绿色为Z从K-图自启动特性:输入0时,01à11;输入1时,01à10,可自启动.(f)由K-图写驱动方程和输出方程:D1=Q1n+1=X+Q0=XQ0D0=Q0n+1=XZ=XQ1Q0(g)画逻辑图CK0D0Q0Q0CK1D1Q1Q1CPZX2.采用JK触发器,用摩尔型同步状态机实现。0S1/0S0/010(a)摩尔型状态图:S0:初始状态,输出0;1001S1:输入序列为“0”,输出0;S2:输入序列为“01”,输出0;1S2/0S3/1S3:输入序列为“011”,输出1;

数字电路与数字系统33(b)状态表:SnX=0X=1ZSn+1Sn+1S0S1S00S1S1S20S2S1S30S3S1S01(c)状态化简:由隐含表法知,该状态图不能再化简;S1S0S2S2S0S3S2S3S3xxxS0S1S2(e)状态分配:根据状态分配原则1,次状态对相同时,原状态对相邻:S0、S3应安排相邻;根据状态分配原则2,一个状态在输入相邻时的次态相邻:S0、S1,S1、S2,S1、S3应分别安排相邻;根据状态分配原则3,输入相同时输出也相同的状态相邻:S0、S1,S0、S2,S1、S2应分别安排相邻。据此,安排相邻关系如下:Q0S0S1S2S3Q1状态分配后的状态表为:(Q1Q0)n(Q1Q0)n+1ZX=0X=10001000010111011011001001001(e)画K-圈(因用JK触发器,K-圈不过Q、Q的边线):黑色为Q1,红色为Q0,绿色为Z本题无自启动问题.(f)由K-图写次态方程和输出方程,并由此得驱动方程:

数字电路与数字系统33Q1n+1=XQ0Q1+XQ0Q1J1=XQ0,K1=XQ0Q0n+1=XQ0+XQ0+Q1Q0J0=X,K0=XQ1Z=Q1Q0(g)画逻辑图K0J0Q0Q0CPZXK1J1Q1Q1该例说明:一般情况下,完成同一功能,使用摩尔型状态机比使用米里型状态机的状态数要多。7-48解:(a)驱动方程:D2=Q1Q0,D1=Q0,D0=Q2输出方程:C=Q2状态方程:Q2n+1=D2=Q1Q0,Q1n+1=D1=Q0,Q0n+1=D0=Q2(b)状态转换表:(c)状态转换图:000/0Q2Q1Q0/C001/0011/0111/1110/1100/1010/0101/1Nr.(Q2Q1Q0)n(Q2Q1Q0)n+1Z0000001010010110201000103011111041000001510101016110000171111101(d)能自启动的模5计数器.(e)波形图,画有效循环一周期即可:CPQ1Q0Q2(C)

数字电路与数字系统337-52解:图中:Cr无效;S1S0=01,‘194作右移操作;SR=QD+QC。由此可直接得电路的状态图(根据移存器特点):0100QDQCQBQA100011000010010100000001001101111110101010010110101111011111由状态图知,这是模7计数器。如果看成是分频器,则其输出为近似方波:高电平比低电平短一个时钟周期。若用“与非”门代替图中的“或非”门,则SR=QDQC,其状态图变为:QDQCQBQA0100100101110011000100001111111011001000001001010110110110111010由状态图知,这是模7计数器。如果看成是分频器,则其输出为近似方波:低电平比高电平短一个时钟周期。7-56用上升沿翻转D触发器实现101001序列发生器。解:(1)移存型A.序列长L=6,需3位触发器。

数字电路与数字系统33B.状态顺序表(令Q0为输出序列,Q1,Q2依次比Q0晚一个、两个时钟周期,即得此态序表):x011110100001010x101(Q2Q1Q0)n+1Q2Q1Q0Nr.Q2Q1Q0001111102101301041005001表中无重复状态;C.直接由态序表填Q0的次态K图,注意状态表中下一行是上一行的次态即可。D.画K圈:图中红色为Q2的K圈,绿色为Q1的K圈,黑色为Q0的K圈;E.自启动:由K图直接读出:000à001,111à110,可自启动。F.由K图写Q0的状态方程,也就是触发器的驱动方程:D0=Q0n+1=Q2Q1+Q2Q0,D1=Q1n+1=Q0,D2=Q2n+1=Q1,这就是移存器的驱动.G.逻辑图(画法不唯一):CK0D0Q0Q0CK1D1Q1Q1CPCK2D2Q2Q2(2)状态编码型A.序列长L=6,需3位触发器。B.状态顺序表(令Q0为输出序列,Q1,Q2理论上可任意安排,原则是无重复状态;如果考虑相邻原则,则驱动会简单些):Nr.Q2Q1Q0000110002011301041105101

数字电路与数字系统33表中无重复状态;C.直接由态序表填Q0的次态K图,注意状态表中下一行是上一行的次态即可。D.画K圈:图中红色为Q2的K圈,绿色为Q1的K圈,黑色为Q0的K圈;E.自启动:由K图直接读出:100à011,111à001,可自启动。F.由K图写Q0的状态方程,也就是触发器的驱动方程:D0=Q0n+1=Q2+Q1Q0,D1=Q1n+1=Q2Q1+Q1Q0,D2=Q2n+1=Q1Q0;G.逻辑图略.7-59解:Z1=001001001001001,Z0=101100101100101.Z1周期长为3,Z0周期长为6,它们的最小公倍数为6,故作模6计数器即可。1.按状态编码计数型序列信号发生器设计;Nr.Q2Q1Q0000110002111310141005110(a)状态顺序表(令Q1=Z1,Q0=Z0;Q2的选择:无重复状态即可;相邻状态尽量安排逻辑相邻):111000xx110100101001(Q2Q1Q0)n+1Q2Q1Q0(b)次态K图:(c)画K-圈(因用JK触发器,K-圈不过Q、Q的边线):红色为Q2,绿色为Q1,黑色为Q0(d)自启动:由K图直接读出:010à001,011à001,可自启动。(e)由K-图写次态方程和输出方程,并由此得驱动方程:Q2n+1=Q0Q1Q2+(Q0+Q1)Q2J2=Q1Q0,K2=Q1Q0Q1n+1=Q0Q1J1=Q0,K1=1Q0n+1=(Q2+Q1)Q0+Q1Q0J0=Q2+Q1,K0=Q1(f)逻辑图,略。2.按状态解码计数型序列信号发生器设计。Nr.Q2Q1Q0000010012010301141005101(a)设计模6计数器:状态顺序表

数字电路与数字系统33001010100011101000xx(Q2Q1Q0)n+1Q2Q1Q0(b)次态K图:(c)画K-圈(因用JK触发器,K-圈不过Q、Q的边线):红色为Q2,绿色为Q1,黑色为Q0(d)自启动:由K图直接读出:110à111,111à000,可自启动。(e)由K-图写次态方程和输出方程,并由此得驱动方程:Q2n+1=Q0Q1Q2+Q0Q2J2=Q1Q0,K2=Q0Q1n+1=Q2Q0Q1+Q0Q1J1=Q2Q0,K1=Q0Q0n+1=Q0J0=1,K0=1(f)逻辑图,略。(g)设计译码电路。由于本题对使用器件无要求,可使用任意组合器件。无论使用那种方法,均应先列下表,该表是输出序列与计数器输出状态的关系表。有了此表,可用任意组合电路实现译码。Q2Q1Q0Z1Z0000010010001011011011000010110'

您可能关注的文档

- 《数字电子技术(第二版)习题册》答案.doc

- 《数字电子技术》黄瑞祥 第五章习题答案.doc

- 《数字电子技术基础》习题答案(王毓银)版的.doc

- 《数字电子技术基础》国防科技版习题答案.docx

- 《数字电子技术基础》第3版(余孟尝)高等教育出版社_课后答案.doc

- 《数字电子技术基础》第3版(余孟尝)高等教育出版社_课后答案.pdf

- 《数字电子技术基础简明教程(第三版)》余孟尝主编_答案.doc

- 《数字电子技术基础简明教程(第三版)》余孟尝答案.pdf

- 《数字电子技术基础简明教程(第三版)答案》.pdf

- 《数字通信原理》习题及解答20120371.pdf

- 《数字逻辑》(第二版)习题答案.doc

- 《数学物理方程》第三版习题答案.pdf

- 《数据与计算机通信》第七版课后习题答案.doc

- 《数据库原理与应用》(孟凡荣 闫秋艳)课后习题答案.doc

- 《数据库原理与应用》课后习题答案.doc

- 《数据库原理与应用》课后习题答案1至5章 孟凡荣主编.doc

- 《数据库原理及应用》邮电二版 习题参考答案(总体).doc

- 《数据库系统及应用》习题解答.doc

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明