- 1009.50 KB

- 2022-04-22 11:31:03 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

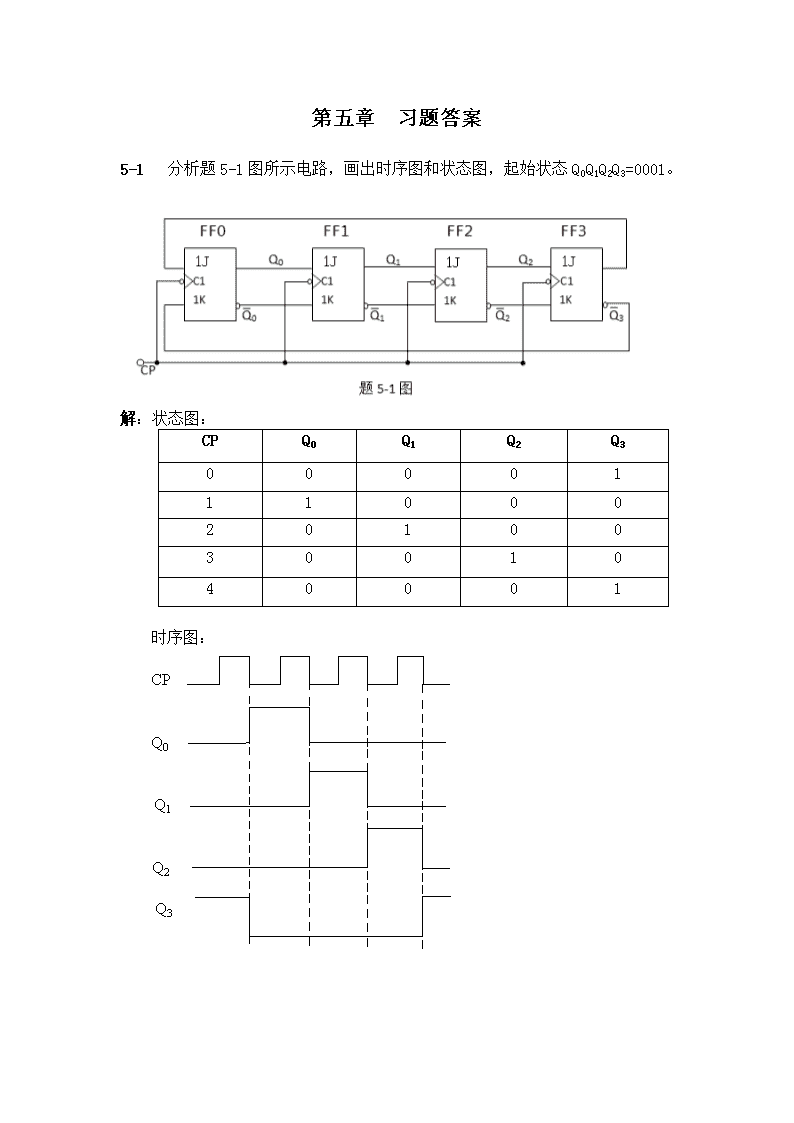

'第五章习题答案5-1分析题5-1图所示电路,画出时序图和状态图,起始状态Q0Q1Q2Q3=0001。解:状态图:CPQ0Q1Q2Q30000111000201003001040001时序图:CPQ0Q1Q2Q3

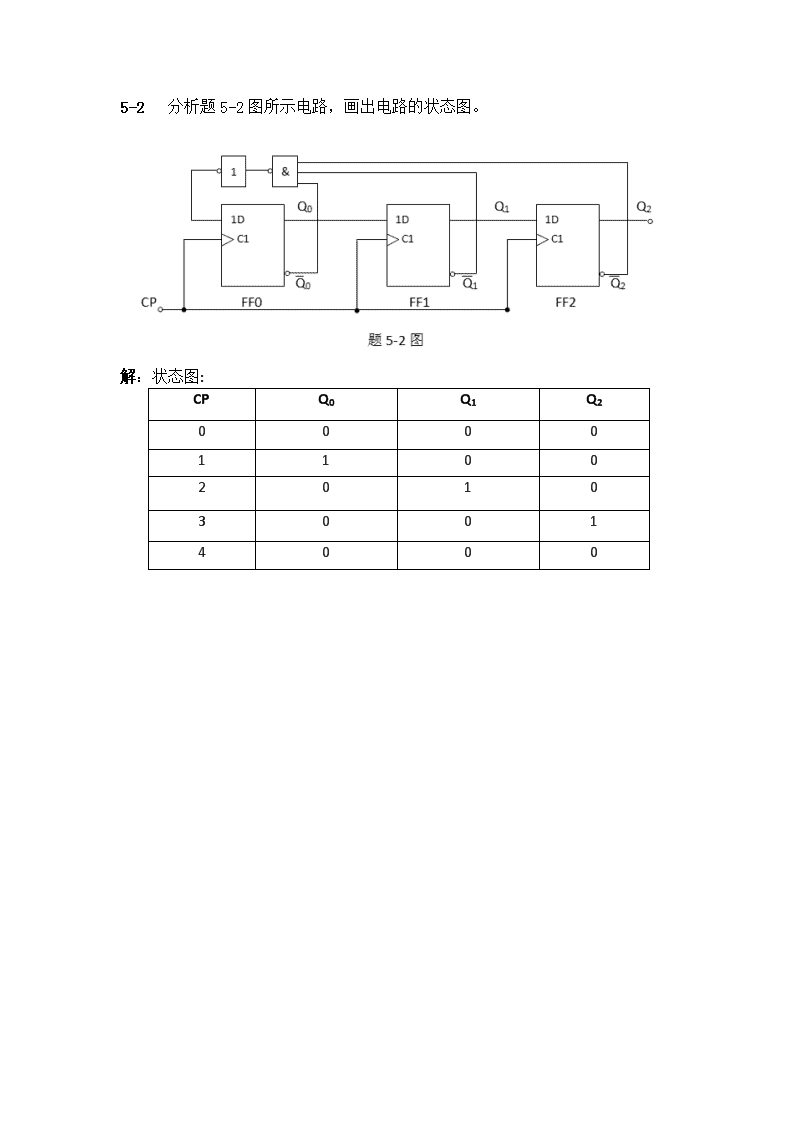

5-2分析题5-2图所示电路,画出电路的状态图。解:状态图:CPQ0Q1Q200001100201030014000

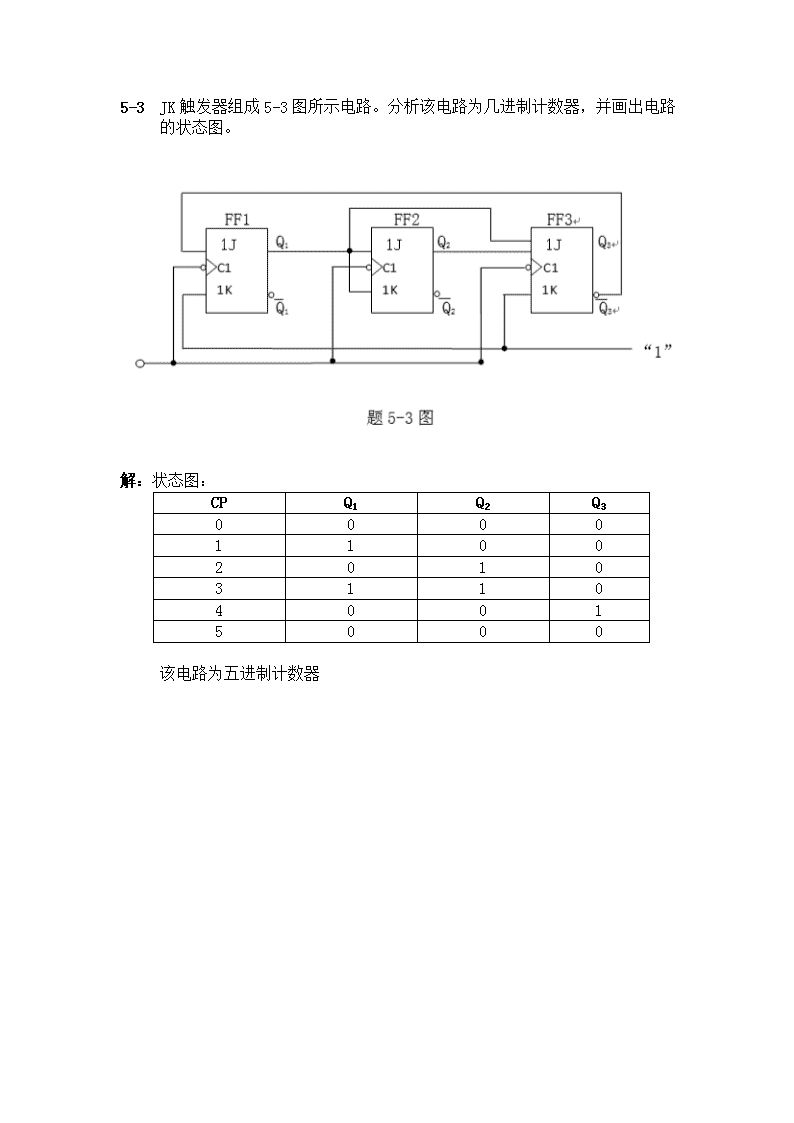

5-3JK触发器组成5-3图所示电路。分析该电路为几进制计数器,并画出电路的状态图。解:状态图:CPQ1Q2Q3000011002010311040015000该电路为五进制计数器

5-4JK触发器促成如图5-4图所示的电路。(1)分析该电路为几进制计数器,画出状态图。(2)若令K3=1,电路为几进制计数器,画出其状态图。解:(1)CPQ1Q2Q301234567000100010110001101011000为7进制计数器(2)CPQ1Q2Q3012345000100010110001100为4进制计数器

5-5试画出题5-5图(a)所示电路中B,C端的波形。输入端A,CP波形如题5-5图(b)所示,触发器的起始状态为零。12345678910111213141516171819CPAQ0Q1BC

5-6分析题5-6图所示电路,画出电路的状态图,说明电路能否自启动。解:状态图:CPQ1Q2Q3Z01234567010000101011100111100011000100101000101000该电路能够自启动

5-7分析题5-7图所示电路,画出电路的状态图,说明电路能否自启动。CPQ4Q3Q2Q10123456701010101010101010100000001100111011110011110111101001000010011100101000011010110110110001110000101101001011100011111111110

由状态图可见,电路图能够自启动

5-8画出题5-8图所示电路的状态图和时序图,简要说明电路的基本功能。解:状态图:功能分析:根据状态图可知:电路为三位格雷码发生器。

5-9画出题5-9图所示的状态图和时序图。解:状态图:时序图:

5-10如题5-10图所示,FF0为下降沿触发的JK触发器,FF1为上升沿触发的D触发器,试对应给定的RD,CP,J,K的波形,画出Q0,Q1的波形。

5-11试用下降沿触发的JK触发器设计一个同步时序电路,要实现的状态图如题5-11图所示。解:电路图:

5-12试用上升沿触发的D触发器和与非门设计一个同步时序电路,要实现的状态图如题5-12图所示。解:电路图如下:

5-13试用下降沿触发的边沿型JK触发器和与非门,设计一个按自然态序进行的七进制同步加法计数器。解:电路图:5-14试用上升沿触发的边沿型D触发器和与非门,设计一个按自然态序进行计数的十进制同步加法计数器。解:电路图:

5-15试用JK触发器设计一个同步十进制计数器,要实现的状态图如题5-15图所示。解:电路图如下:

5-16试设计一个具有如题5-16图所示功能的计数器电路,图中M为控制变量。M=0,计数器为8421码六进制加法;M=1,计数器为循环码六进制计数。解:电路图如下:

5-17试用JK触发器设计一个同步2421(A)码的十进制计数器,电路的状态图如题5-17图所示。解:电路图如下:

5-18试用JK触发器设计一个同步余3循环码十进制减法计数器,电路的状态图如题5-18图所示。解:电路图如下:

5-19用JK触发器设计一个步进电机用的三相六状态脉冲分配器。如果用1表示线圈导通,用0表示线圈截止,则三个线圈ABC的状态图如题5-19图所示。在正转时输入端G为1,反转时为0。解:电路图如下:

5-20用JK触发器设计一个按自然态序进行计数的同步加法计数器,要求当控制信号M=0时为六进制,M=1时为十二进制。解:电路图实现如下:

5-21分析题5-21图所示各电路,画出它们的状态图和时序图,指出各是几进制计数器。

解:状态图:时序图:

5-22试分析题5-22图所示电路,指出各计数器的计数长度M是多少?并画出相应的状态图。

解:74161为异步清零,同步置数的4位同步二进制加法计数器(a)为13进制同步加法计数器,状态转换图如下:(b)为9进制加法计数器,状态转换图如下:(c)为15进制计数器,状态转换图如下:(d)为7进制计数器,状态转换图如下:

5-23试分析题5-23图所示电路的计数长度为多少,采用的是哪种接法。分别画出(Ⅰ)和(Ⅱ)的状态图。若电路作为分频器使用,则芯片(Ⅱ)的CO端输出的脉冲和时钟CP的分频比为多少?题5-23图解:(Ⅰ)为7进制同步加法计数器,其状态图如下:(Ⅱ)为5进制同步加法计数器,其状态图如下:两片74160计数器之间采用异步接法。若电路作为分频器使用,则芯片(Ⅱ)的CO端输出的脉冲和时钟CP的分频比为1:35。

5-24试分析题5-24图所示电路,分别画出两个芯片的状态图。若电路作为分频器使用,则74161的输出Y与时钟CP的分频比为多少?解:图中74160为6进制同步加法计数器,状态图如下:图中74161为6进制同步加法计数器,状态图如下:若电路作为分频器使用,则74161的输出Y与时钟CP的分频比为1:36

5-25试分析题5-25图所示各电路,画它们的状态图和状态表,指出各是几进制计数器。

解:(a)状态表:Q3nQ2nQ1nQ0nQ3n+1Q2n+1Q1n+1Q0n+10000000100100011010000010010001101000000状态图:为五进制计数器(b)状态表:Q3nQ2nQ1nQ0nQ3n+1Q2n+1Q1n+1Q0n+1100000010010001101001000100110101011000100100011010010001001101010110000状态图:为九进制计数器

(c)状态表:Q3nQ2nQ1nQ0nQ3n+1Q2n+1Q1n+1Q0n+110010000000100100011010001010000000100100011010001011001状态图:为七进制计数器

5-26分析题5-26图所示各电路,分别指出它们各是几进制计数器。解:(a)图中74290(Ⅰ)构成10进制,74290(Ⅱ)构成9进制,74290(Ⅱ)的状态图如下:所以电路构成910进制计数器。(b)根据归零逻辑可知,采用异步清零时SN=(10001000)2=(136)10

所以电路构成136进制计数器。5-27试分别画出利用下列方法构成的六进制计数器的连线图。(1)利用74161的异步清零功能;(2)利用74163的同步清零功能;(3)利用74161或74163的同步置数功能;(4)利用74290的异步清零功能。解:(1)(2)(3)

(4)5-28试分别画出用74161的异步清零和同步置数功能构成的下列计数器的连线图。(1)60进制计数器(2)180进制计数器解:(1)异步清零电路图如下:

同步置数电路图如下:(2)异步清零电路图如下:同步置数电路图如下:

5-29试分别画出用74290构成的下列计数器的连线图:(1)9进制计数器(2)50进制计数器(3)30进制计数器(4)88进制计数器解:(1)9进制计数器电路图如下:(2)50进制计数器电路图如下:

(3)30进制计数器电路图如下:(4)88进制计数器电路图如下:

5-30用74163设计一个按自然态序进行计数的同步加法计数器,要求当控制信号M=0时为六进制,M=1时为十二进制。解:电路实现如下:

5-31试分别画出用74164(8位单向移位寄存器)构成的下列环形计数器:(1)5位环形计数器;(2)7位环形计数器。解:(1)5位环形计数器电路图如下:(2)7位环形计数器电路图如下:

5-32试分别画出用74164构成的下列扭环形计数器:(1)4位能自启动的扭环形计数器;(2)8位扭环形计数器。解:(1)4位能自启动的扭环形计数器电路图如下:(2)8位扭环形计数器电路图如下:

5-33试分别画出用74164构成的最大长度移位型计数器:(1)3位最大长度移位型计数器;(2)7位最大长度移位型计数器。解:(1)电路图如下:(2)电路图如下:

5-34试画出用74161(4位二进制同步加法计数器)构成具有时序状态为0,1,2,3,4,5,8,9,10,11,14,15的计数器。解:电路图如下:5-35用计数器74LS161和数据选择器(MUX)74LS151设计一个脉冲序列发生器,使之在一系列CP信号作用下,其输出端能周期性地输出00101101的脉冲序列。解:电路图如下:

5-36用计数器74LS161及8选1(MUX)74LS151各一片以及必要的辅助电路产生序列信号0100’1100’0101’11。解:电路图如下:5-37用计数器74LS161及8选1(MUX)74LS151各一片以及必要的辅助电路产生如下序列信号:当X=0时,序列信号为0110’1101;当X=1时,序列信号为1010’010。解:电路图如下:

5-38用移位寄存器以及必要的辅助电路设计一个同步时序电路,它有两个输入X1和X2,一个输出Z。当X1连续输入3个1(正好3个)后,X2再输入1个1时,输出Z为1,而且在同一时间内X1和X2不能同时为1。画出状态图并用电路实现。解:输入X1,X2与输出Z之间的关系为:CP123455’X1X2Z011101Φ00010000010电路图如下:

5-39用74LS161计数器为核心器件实现如题5-39图所示的状态图,其中X1X2/Z表示输入/输出,且X1与X2不能同时为1。解:(1)输出变量为:Z=S3*X2(2)计数控制信号:CT=*X1(3)置数控制信号:LD=(4)并行置数信号:D2=D1=D0=0电路图如下:

5-40用74LS161计数器以及必要的辅助电路实现如题5-40图所示的状态图。解:(1)CT=b(2)LD=c+S4*b(3)D2=0,D1=c,D0=0电路实现如下:'

您可能关注的文档

- 《数值计算方法》习题答案.pdf

- 《数值计算方法》试题与答案.doc

- 《数字信号处理》第三版课后习题答案.pdf

- 《数字信号处理》第三版高西全版课后习题答案.doc

- 《数字信号处理》第三版高西全版课后习题答案.pdf

- 《数字信号处理》第四版高西全版课后部分习题答案.pdf

- 《数字信号处理》课后答案.doc

- 《数字信号处理》高西全丁美玉第三版课后答案详解.doc

- 《数字电子技术(第二版)习题册》答案.doc

- 《数字电子技术基础》习题答案(王毓银)版的.doc

- 《数字电子技术基础》国防科技版习题答案.docx

- 《数字电子技术基础》第3版(余孟尝)高等教育出版社_课后答案.doc

- 《数字电子技术基础》第3版(余孟尝)高等教育出版社_课后答案.pdf

- 《数字电子技术基础简明教程(第三版)》余孟尝主编_答案.doc

- 《数字电子技术基础简明教程(第三版)》余孟尝答案.pdf

- 《数字电子技术基础简明教程(第三版)答案》.pdf

- 《数字电路-分析与设计》1--10章习题及解答(部分)_北京理工大学出版社.doc

- 《数字通信原理》习题及解答20120371.pdf

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明