- 5.51 MB

- 2022-04-22 11:26:54 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'《数字电子技术》复习题参考答案一、选择题1.在数字电路中,用“1”表示高电平,用“0”表示低电平,称为(C);(A)译码(B)编码(C)正逻辑(D)负逻辑2.AB(A+BC)化成最简式是(D)A、AB、BC、A+BD、AB3、以下说法正确的是:(A)A、将OC门输出端连在一起,再通过一个电阻接外电源,可以实现线与逻辑关系。B、三态门的输出端可以连在一起,但不能构成数据总线。C、将OC门输出端直接连在一起,可以实现线与逻辑关系。D、三态门的输出端连在一起,再通过一个电阻接外电源,构成数据总线。4、全加器有3个输入端ABC,其中C为低位进位,输出端有S和CO,S表示本位和,CO表示向高位进位,如果输入A=1B=1C=1则S和CO各等于(C)AS=0CO=1BS=1CO=0CS=1CO=1DS=0CO=05、数据选择器输入端D0D1D2D3,控制端A1A0若A1A0=10,则哪个输入端的数据可以输出(C)AD0BD1CD2DD36、触发器的特性方程是(A)AQn+1=BQn+1=1CQn+1=0DQn+1=7、有一组代码需要暂时存放,应该选用( B )A、计数器B、寄存器C、译码器D、全加器8、有关单稳态触发器的说法错误的是:(D)A、它有一个稳态和一个暂稳态B、在外来触发脉冲作用下,能从稳态翻转到暂稳态C、暂稳态维持一段时间后,将自动返回稳态。D、它有两个稳定状态9、触发器复位端R和置位端S的关系正确的是(B)A、两者同时有效B、不可能两者同时有效C、复位就是置位D、难以判断10、十进制数63的8421BCD码是(C)(A)10000000(B)00111111(C)01100011(D)0101001118

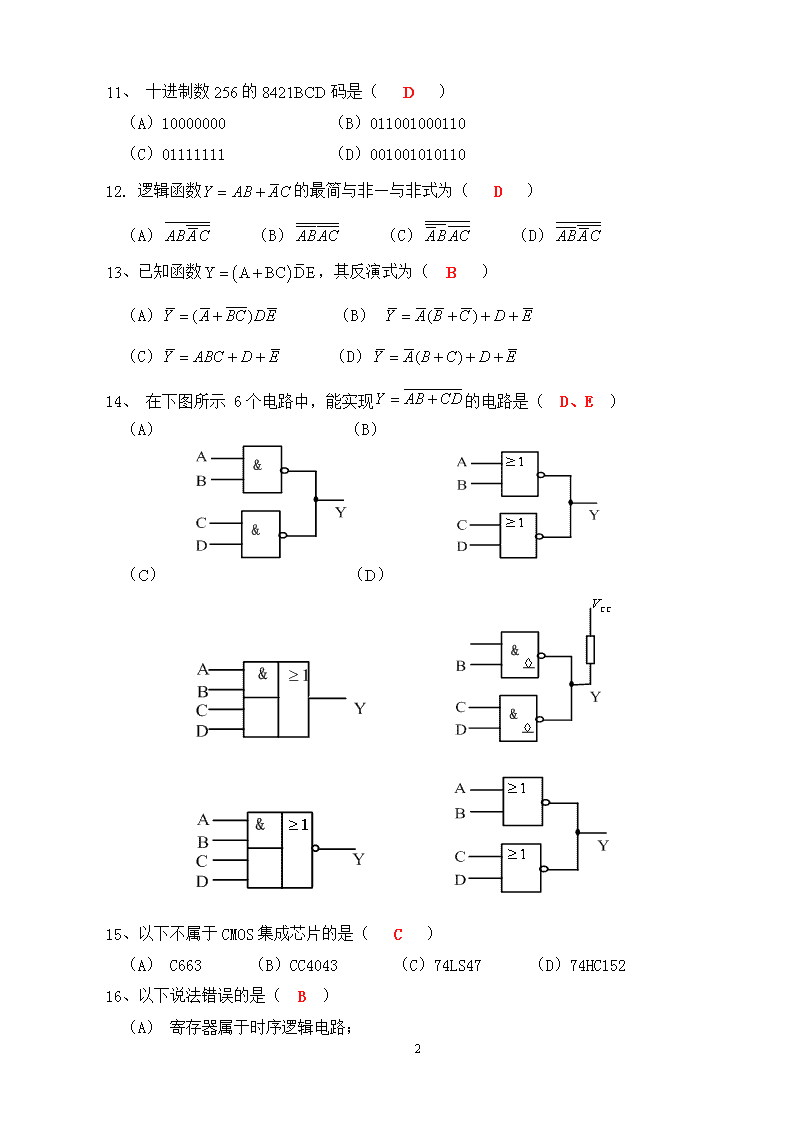

11、十进制数256的8421BCD码是(D)(A)10000000(B)011001000110(C)01111111(D)00100101011012.逻辑函数的最简与非—与非式为(D)(A)(B)(C)(D)13、已知函数,其反演式为(B)(A)(B)(C)(D)14、在下图所示6个电路中,能实现的电路是(D、E)(A)(B)(C)(D)15、以下不属于CMOS集成芯片的是(C)(A)C663(B)CC4043(C)74LS47(D)74HC15216、以下说法错误的是(B)(A)寄存器属于时序逻辑电路;18

(A)读/写存储器简称为ROM;(B)基本寄存器只能采用并入并出的数据传送方式;(C)移位寄存器的存储单元只能用边沿触发器构成.17、欲将频率为的正弦波转换成为同频率的矩形脉冲,应选用(C)(A)多谐振荡器(B)T’型触发器(C)施密特触发器(D)单稳态触发器18、存储容量为位的RAM,需要的地址码的位数为(B)(A)3(B)10(C)13(D)8019、以下可以用来构成计数器的是(D)【注:本题最好改成“不能构成同步触发器的是(A)】(A)基本RS触发器(B)主从RS触发器(C)同步D锁存器(D)边沿JK触发器20、如图1-10所示组合电路中,Y=(B)(A)(B)(C)(D)图1-10二、填空题1.___195_____(10110101)2=(181)10110111102(129)10=(10000001)2(11001)2=()10(254)10=()8421BCD2.在数字电路中,用“0”表示高电平,用“1”表示低电平,则称为__负__逻辑;3.逻辑函数的表示方法包括:真值表、卡诺图、逻辑表达式、逻辑图和__波形图__;4.时序逻辑电路的基本组成单元是____触发器_____;5.已知函数,其反演式;6.触发器的特性方程为:;18

1.如左下图所示的TTL电路,其输出信号Y=;2.如右上图所示电路中,若A=0、B=1,则Q=1__;3.用555定时器构成的单稳态触发器中,,,则=;4.用555定时器构成的多谐振荡器中,,,则输出电压的占空比q=_2/3_;5.逻辑函数的最简与非—与非式为;6.化简A+B+C+D__;13.T触发器的特性方程为:;14.逻辑函数的卡诺图如右下图所示,它的最简与或式是;15.用555定时器构成的施密特触发器,作阈值探测器,要求能将输入信号中幅值大于5V的脉冲信号都检测出来,则电源电压应为__7.5__V;16.用555定时器构成的多谐振荡器中,,,则输出电压的频率=0.44KHZ;17.、同或门的表达式是(Y=A⊙B=)18、正的“或非”门也就是负(与非)门18

19、通常所说的三态门,是指哪3种状态?(0态、1态、高阻态)20、在TTL三态门、OC门、与非门、异或门和或非门电路中,能实现“线与”逻辑功能的门为(OC门),能实现总线连接的门为(三态门)21、一个二进制编码器若需要对12个输入信号进行编码,则需要采用(4)位二进制代码。22、5变量输入译码器,其译码输出信号最多应有(32)个。23、需要判断两个二进制数的大小或相等,可以使用(数值比较器)电路。24、边沿触发器的抗干扰能力比同步触发器要(强)25、把JK触发器转换成T′触发器的方法是(令J=K=1)26、若4位同步二进制加法计数器当前的状态是0111,输入下一个时钟脉冲后,其内容变为(1000)。27、清零后的四位移位寄存器,如果要将四位数码全部串行输入,再串行从寄存器中输出,共需要(8)个CP脉冲。28、由3个触发器组成的二进制加法计数器能有(8)种状态。29、能用于信号幅度鉴别、波形变换和整形的电路是(施密特触发器)。30、在8位A/D转换电路中,如果输入的模拟信号电压是2V,则分辨率是()三、画图题1.如图所示的电路,根据给出的A、B、C的波形对应画出输出信号Y的波形。2.如图所示CMOS门电路,根据给出的A、B的波形对应画出输出信号Y的波形;3.如图3-2所示的触发器电路,根据给出的波形图,画出对应的的波形;18

图3-24、图3-2所示的触发器电路,根据给出的CP及D的波形图,画出对应的的波形。5、图3-3所示的施密特触发器中,、,则该电路的回差=3.33V,输入电压的最大值为,波形已给出,对应画出的波形。图3-36、如图所示,FF0、FF1都是T′触发器,它们的开始状态均为0,对应画出、Q0、Q1、的波形。18

7、时序电路如下图所示,起始状态是Q0Q1Q2=001,画出电路的时序图。(8分)18

四、化简与分析1.化简解:Y=;2.用卡诺图化简解:卡诺图如下:18

3.用卡诺图法化简解:画出卡诺图如下。由卡诺图化简得到=04、用卡诺图化简下列函数成为最简与或式。(∑d为约束项之和)F(A,B,C,D)=∑m(0,1,4,9,12,13)+∑d(2,3,6,10,11,14)解:由卡诺图可得5、写出下图所示电路输出信号的最简与或式Y=;18

6、试分析图示的组合逻辑电路的功能解:A⊙B⊙C列出真值表如下:ABCY00000011010101101001101011001111由真值表知,这是奇偶校验电路。7、如图所示电路,写出S、C的逻辑表达式,并分析该电路实现了什么功能?解:电路完成全加功能,S为全加和,C为高位进位。18

8、写出图示电路的输出信号的逻辑表达式,说明其功能。五、电路设计题1.用译码器74LS138和与非门实现函数(8分)2、用两片74161构成24进制计数器;18

3、用两片74161构成60进制计数器;18

4、设计一个组合逻辑电路,其输入是3位二进制数B=B2B1B0,输出是Y=2B,Y也是二进制数。18

5、用集成数据选择器实现函数;解:选用八选一数据选择器(例如74151)比较得画出逻辑电路如下:6、用边沿JK触发器和门电路设计一个按自然态序进行计数的七进制同步加法计数器。解:画出状态图如下:18

18

六、综合应用题1、用CP下降沿触发的JK触发器设计一个同步时序电路,状态图如下图所示。解:1)由状态图画出电路次态Q2Q1Q0的卡诺图。Q1Q0Q20001111001100000100011011100×××1012)将电路次态分解为三个小卡诺图如下,分别表示Q2n+1、Q1n+1、Q0n+1这三个次态函数。Q2n+1Q1Q0Q20001111001000101×118

Q1n+1Q1Q0Q20001111001010110×0Q0n+1Q1Q0Q20001111000001110×13)合并最小项,化简次态函数,得状态方程4)与JK触发器的标准形式比较得驱动方程5)由驱动方程画出电路逻辑图。2、用下降沿触发的边沿JK触发器设计一个同步时序电路,要求状态图如下图所示。→000→001→011↑↓100←110←11118

18'

您可能关注的文档

- 《教育心理学(皮连生)》课后习题答案.doc

- 《教育技术》课后习题答案参考(北师大).doc

- 《数值分析》黄仿伦改编英文版课后习题答案.pdf

- 第二版(王能超_编著)课后习题答案__高等教育出版社.doc

- 《数字信号处理(第四版)》部分课后习题解答.docx

- 《数字信号处理》第二版课后答案.pdf

- 《数字信号处理》试题库答案.doc

- 《数字信号处理与DSP实现技术》课后习题与参考答案.doc

- 《数字图像处理》习题参考答案.docx

- 《数字电子技术》黄瑞祥 第三章习题答案.doc

- 《数字通信原理(第三版)》教材课后习题答案.doc

- 通信原理》综合练习题_答案_.doc

- 《数字逻辑》 第四版部分习题答案.pdf

- 《数字逻辑》(白中英)(第六版)习题解答.doc

- 《数字逻辑与电路》复习题(带参考答案).pdf

- 《数学思维方式与创新》3习题答案.doc

- 《数据库原理》课后习题及解答.doc

- 《数据库原理》课后习题答案--ch1.pdf

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明