- 761.50 KB

- 2022-04-22 11:35:02 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

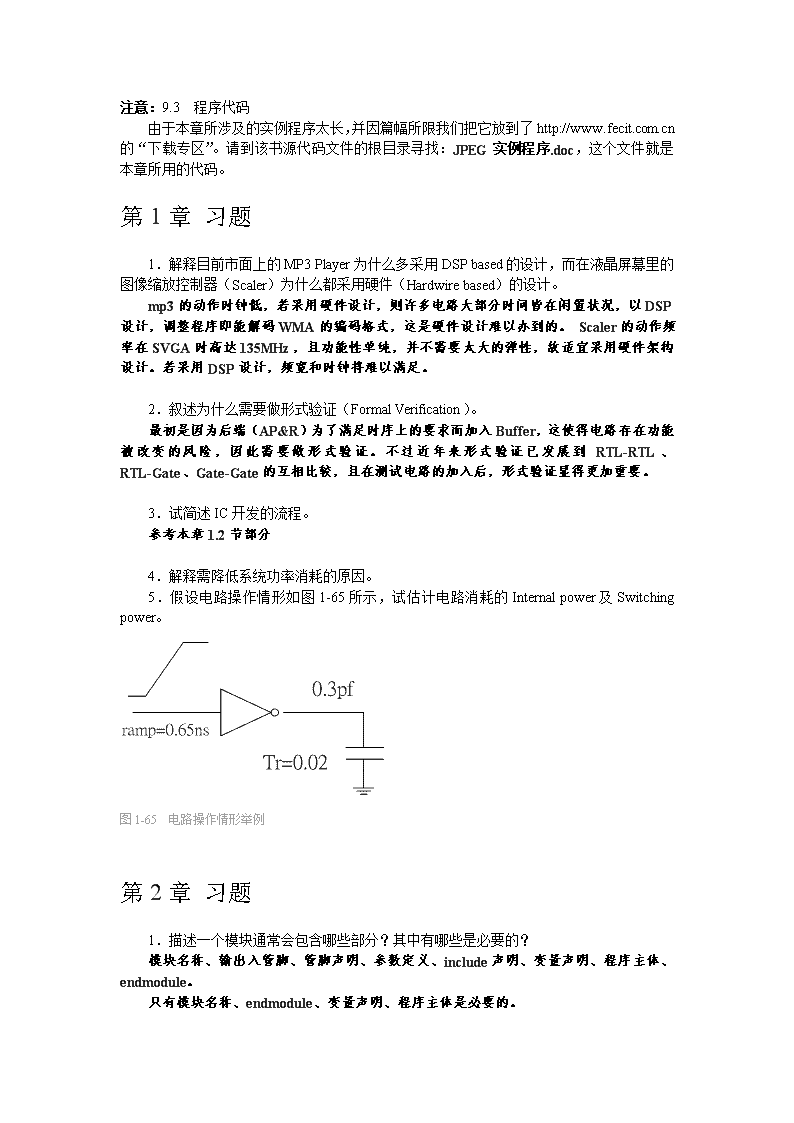

'注意:9.3程序代码由于本章所涉及的实例程序太长,并因篇幅所限我们把它放到了http://www.fecit.com.cn的“下载专区”。请到该书源代码文件的根目录寻找:JPEG实例程序.doc,这个文件就是本章所用的代码。第1章习题1.解释目前市面上的MP3Player为什么多采用DSPbased的设计,而在液晶屏幕里的图像缩放控制器(Scaler)为什么都采用硬件(Hardwirebased)的设计。mp3的动作时钟低,若采用硬件设计,则许多电路大部分时间皆在闲置状况,以DSP设计,调整程序即能解码WMA的编码格式,这是硬件设计难以办到的。Scaler的动作频率在SVGA时高达135MHz,且功能性单纯,并不需要太大的弹性,故适宜采用硬件架构设计。若采用DSP设计,频宽和时钟将难以满足。2.叙述为什么需要做形式验证(FormalVerification)。最初是因为后端(AP&R)为了满足时序上的要求而加入Buffer,这使得电路存在功能被改变的风险,因此需要做形式验证。不过近年来形式验证已发展到RTL-RTL、RTL-Gate、Gate-Gate的互相比较,且在测试电路的加入后,形式验证显得更加重要。3.试简述IC开发的流程。参考本章1.2节部分4.解释需降低系统功率消耗的原因。5.假设电路操作情形如图1-65所示,试估计电路消耗的Internalpower及Switchingpower。图1-65电路操作情形举例第2章习题1.描述一个模块通常会包含哪些部分?其中有哪些是必要的?模块名称、输出入管脚、管脚声明、参数定义、include声明、变量声明、程序主体、endmodule。只有模块名称、endmodule、变量声明、程序主体是必要的。

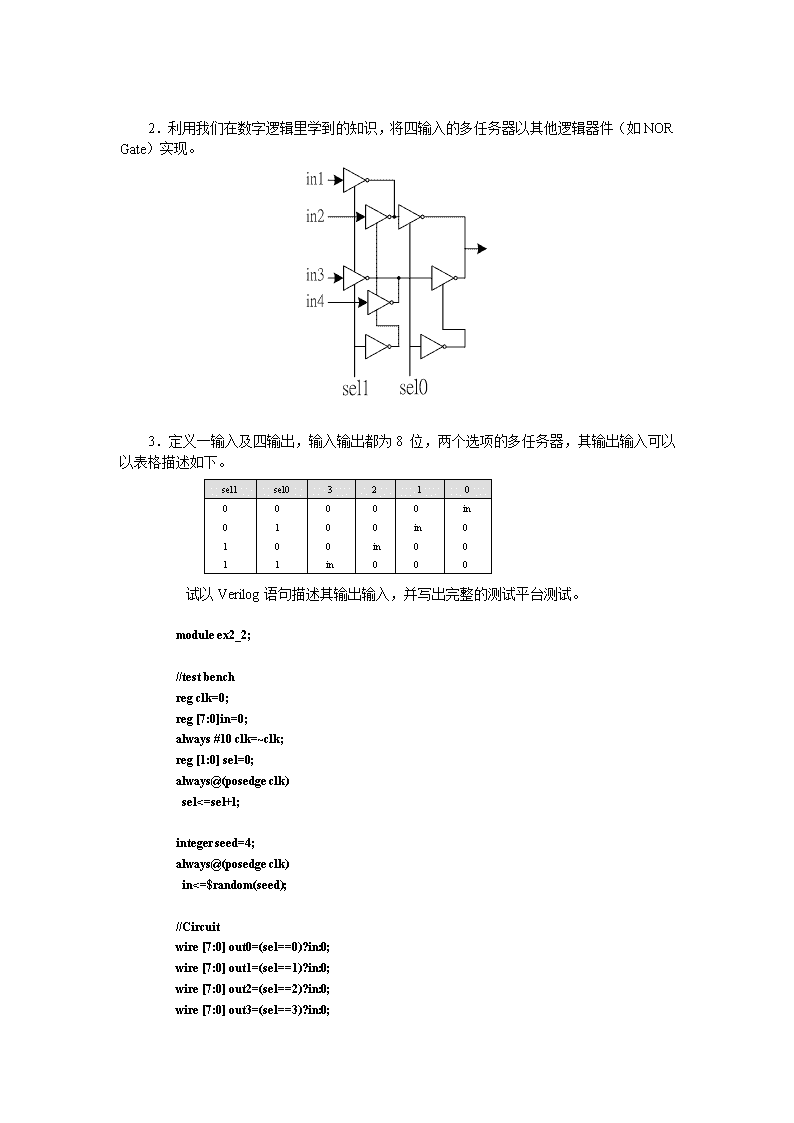

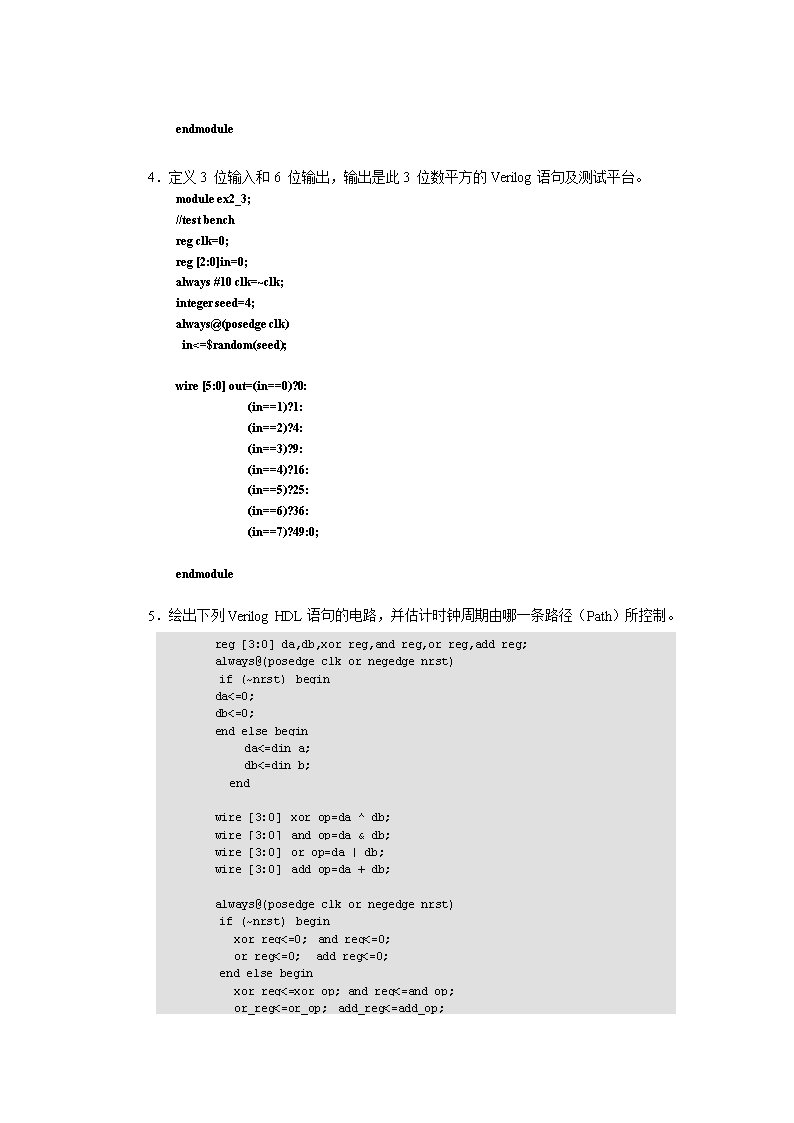

2.利用我们在数字逻辑里学到的知识,将四输入的多任务器以其他逻辑器件(如NORGate)实现。3.定义一输入及四输出,输入输出都为8位,两个选项的多任务器,其输出输入可以以表格描述如下。sel1sel0321000110101000in00in00in00in000试以Verilog语句描述其输出输入,并写出完整的测试平台测试。moduleex2_2;//testbenchregclk=0;reg[7:0]in=0;always#10clk=~clk;reg[1:0]sel=0;always@(posedgeclk)sel<=sel+1;integerseed=4;always@(posedgeclk)in<=$random(seed);//Circuitwire[7:0]out0=(sel==0)?in:0;wire[7:0]out1=(sel==1)?in:0;wire[7:0]out2=(sel==2)?in:0;wire[7:0]out3=(sel==3)?in:0;

endmodule4.定义3位输入和6位输出,输出是此3位数平方的Verilog语句及测试平台。moduleex2_3;//testbenchregclk=0;reg[2:0]in=0;always#10clk=~clk;integerseed=4;always@(posedgeclk)in<=$random(seed);wire[5:0]out=(in==0)?0:(in==1)?1:(in==2)?4:(in==3)?9:(in==4)?16:(in==5)?25:(in==6)?36:(in==7)?49:0;endmodule5.绘出下列VerilogHDL语句的电路,并估计时钟周期由哪一条路径(Path)所控制。reg[3:0]da,db,xor_reg,and_reg,or_reg,add_reg;always@(posedgeclkornegedgenrst)if(~nrst)beginda<=0;db<=0;endelsebeginda<=din_a;db<=din_b;endwire[3:0]xor_op=da^db;wire[3:0]and_op=da&db;wire[3:0]or_op=da|db;wire[3:0]add_op=da+db;always@(posedgeclkornegedgenrst)if(~nrst)beginxor_reg<=0;and_reg<=0;or_reg<=0;add_reg<=0;endelsebeginxor_reg<=xor_op;and_reg<=and_op;or_reg<=or_op;add_reg<=add_op;

endreg[3:0]da,db,xor_reg,and_reg,or_reg,add_reg;always@(posedgeclkornegedgenrst)if(~nrst)beginda<=0;db<=0;endelsebeginda<=din_a;db<=din_b;endwire[3:0]xor_op=da^db;wire[3:0]and_op=da&db;wire[3:0]or_op=da|db;wire[3:0]add_op=da+db;always@(posedgeclkornegedgenrst)if(~nrst)beginxor_reg<=0;and_reg<=0;or_reg<=0;add_reg<=0;endelsebeginxor_reg<=xor_op;and_reg<=and_op;or_reg<=or_op;add_reg<=add_op;end由add_op=da+db这一条语句所控制,因为加法的时间延迟最长。6.编写下列电路的Verilog代码,其电路如图2-42所示。图2-42电路示例wire[3:0]A,B;wiretemp3=~(A[3]^B[3]);wiretemp2=~(A[2]&B[2]);wiretemp1=(A[1]&B[1]);

wiretemp0=(A[0]|B[0]);wiretmp=temp3|temp2|temp1|temp0;always@(posedgeclk)dout<=tmp;7.在ex2_7中,我们曾经编写过一个向左旋转(Rotate)一个位的Verilog程序,请试编写一个每一次时钟信号上升沿时向右旋转(Rotate)两个位的逻辑电路及测试平台。moduleex2_6;//testbenchregclk=0,nrst=1,sel=0;reg[7:0]din=0,dout;always#10clk=~clk;initialbegin#50nrst=0;#70nrst=1;#80sel=1;#15sel=0;endintegerseed=4;always@(posedgeclk)din<=#1$random(seed);//circuitwire[7:0]temp={dout[1:0],dout[7:2]};always@(posedgeclkornegedgenrst)if(~nrst)dout<=0;elseif(sel==1)dout<=din;elsedout<=temp;endmodule8.在本章中我们曾设计过一个3-8译码器,试着设计一个8-3编码器。这个编码器当输入为0时具有最高的编码优先权,当输入为8时编码优先权最低。wire[7:0]in;wire[2:0]out=(in==0)?3’b000:(in==1)?3’b001:(in==2)?3’b010:(in==3)?3’b011:(in==4)?3’b100:(in==5)?3’b101:(in==5)?3’b101:(in==6)?3’b110:(in==7)?3’b111:0;

9.试编写一个4位计数器,系统重置后计数器的值为零,计数顺序为:0->2->3->4->7->9>10->11->12->13->14->15->0。reg[3:0]cntr;wirejump2=(cntr==0)|(cntr==5)|(cntr==7);always@(posedgeclkornegedgenrst)if(~nrst)cntr<=0;elseif(jump2)cntr<=cntr+2;elsecntr<=cntr+1;10.试对ex2_12的NRZI译码编写程序。第3章习题1.试以forever描述一个时间周期为20时间单位的时钟信号。regclk=0;initialforever#10clk=~clk;2.在本章中提到的循环语句有for、repeat、while循环。试以这三种循环编写一个计数器,计数到非常大的数字,以您熟悉的仿真器仿真,然后比较这三种语法所耗的时间。3.比较下列两种VerilogHDL的reset语句,分别对其仿真,比较它们有什么不同,并绘出它们的电路图。case1always@(posedgeclkornegedgenrst)if(~nrst)q<=0;elseq<=d;case2always@(posedgeclk)if(~nrst)q<=0;elseq<=d;二者的不同在于,cas1的reset信号是异步的,即使没有clk仍然能清除q;而case2的reset信号是同步的,如果没有clk就无法清除q。case1case24.用您所熟悉的综合器,针对下列两种情形做综合并比较其结果。case1always@(posedgeclk)begin

B=A;A=C;endcase2always@(posedgeclk)beginB<=A;A<=C;endcase1always@(posedgeclk)beginT1=A1|B1;Y1=T1|C1;endalways@(posedgeclk)beginT2<=A2|B2;Y2<=T2|C2;end5.试绘出下列VerilogHDL语句的电路。functionxor_op;input[7:0]A;xor_op=(A[7]^A[6])|(A[5]^A[4])|(A[3]^A[2])|(A[1]^A[0]);endfunctionwireA,B,D;wire[7:0]C;regY1,Y2;always@(AorBorCorD)beginY1=A&B|xor_op(C);Y2=Y1&D;end

第4章习题1.设计一个五层住户电梯的状态图,这个电梯必须满足一般的功能,每一层都可以对其做上楼或下楼的选择,如果觉得很困难,试着简化问题,编写程序及测试平台。2.试编写下列状态变化图(如图4-39所示)的VerilogHDL程序代码。图4-39状态变化图parameterstate0=2"b00,state1=2"b01,state2=2"b10;

reg[1:0]nxt_state,current_state;regy;always@(posedgeclkornegedgenrst)if(~nrst)current_state<=state0;elsecurrent_state<=nxt_state;always@(current_stateorx)case(current_state)state0:beginif(x==0)beginy=0;nxt_state=state0;endelseif(x==1)beginy=1;nxt_state=state1;endendstate1:beginif(x==0)beginy=1;nxt_state=state1;endelseif(x==1)beginy=0;nxt_state=state2;endendstate2:beginif(x==0)beginy=1;nxt_state=state0;endenddefault:beginy=0;nxt_state=state0;endendcase3.用设计程序状态机的方式,设计一个8位的格雷码(GrayCode)计数器。modulegraycntr(gray,clk,inc,rst_n);parameterSIZE=4;output[SIZE-1:0]gray;inputclk,inc,rst_n;

reg[SIZE-1:0]gnext,gray,bnext,bin;integeri;always@(posedgeclkornegedgerst_n)if(!rst_n)gray<=0;elsegray<=gnext;always@(grayorinc)beginfor(i=0;i>i);bnext=bin+inc;gnext=(bnext>>1)^bnext;endendmodule第5章习题1.试阐述同步设计与异步设计的优缺点。①同步设计Ø优点:易于分析,可靠、稳定,易于加入测试电路。Ø缺点:功率消耗大,占据较大的面积,系统整体效能难以提升。②异步设计Ø优点:占据面积小,节省功率消耗。Ø缺点:不易分析,可靠度稳定度差,且不易加入测试电路。2.解释什么是亚稳态(Metastable)。信号在跨越不同的clkdomain时,有时候稳定,而有时候却不稳定的情形如本章中关于Metastable的节所述。3.试编写一个异步内存的行为模型,这个内存的一边接口是CS(ChipSelect)、WR(Write)、RD(Read)、DIN[15:0]、ROW[6:0]、COL[6:0]、DO[15:0],其地址由ROW,COL来替代,输出输入皆为Leveltrigger。Row为Page的概念。这个内存总共有96个Row(每个Row有96个Column)。每个存储元件为16位。另外一边则为OEN(Outputenable)、RROW[6:0](ReadRowaddress)、DO[96X16-1:0]。这一边能由输入Row直接读取96个Column的数据。所有的信号皆为Highactive。其时序图如图5-29所示。writecycle

readcycle图5-29时序图第6章习题1.从设计一个二输入的4位比较器起,设计一个四输入四输出的比较器。这个比较器的输出能将四输出依四输入的大小排列,然后输出。编写其VerilogHDL程序及测试平台。见ex6_1 2.将例ex6_3的乘法器扩展为8位乘以8位的乘法器。见ex6_23.理解Ripple加法器与Ripple减法器的电路,试着设计能由一个控制信号选项来执行加法或减法的4位Ripple加减法器电路。

foradditiontheoperationisfor(i=0;i<=3;i++){}forsubtractionfor(i=0;i<=3;i++){}4.参考本章所介绍的CSA加法器,设计一个八输入的CSA加法器,每一个数据的输入为4位,并编写测试平台验证。见ex6_4'

您可能关注的文档

- 《管理信息系统》课后习题答案.doc

- 《管理学》每章课后题及答案,杨洁 孙玉娟著.docx

- 《管理学》第三版 谭力文 武汉大学出版社 课后案例分析题答案.doc

- 《管理学原理》大纲、目录、课后习题参考答案.doc

- 《管理经济学》课后习题答案.pdf

- 《管理运筹学》 第八章 习题答案.pdf

- 《管理运筹学》习题3解答.doc

- 《管理运筹学》复习题及参考答案.doc

- 《管理运筹学》复习题及参考答案管.doc

- 《精馏》课后选做题-配有答案.pdf

- 《系统工程》复习题及答案.docx

- 《系统工程》第四版习题解答.doc

- 《线性代数》第3章习题解答(rr).doc

- 《线性代数》练习题(附答案).doc

- 《组织行为学》第三版 (张德 着) 课后习题答案 高等教育出版社.pdf

- 《经济学原理》练习题、答案.doc

- 《经济学基础》(精要版)第6版1-3章课后习题详解.docx

- 《经济学基础》各章习题及参考答案.doc

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明