- 3.17 MB

- 2022-04-22 11:29:34 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

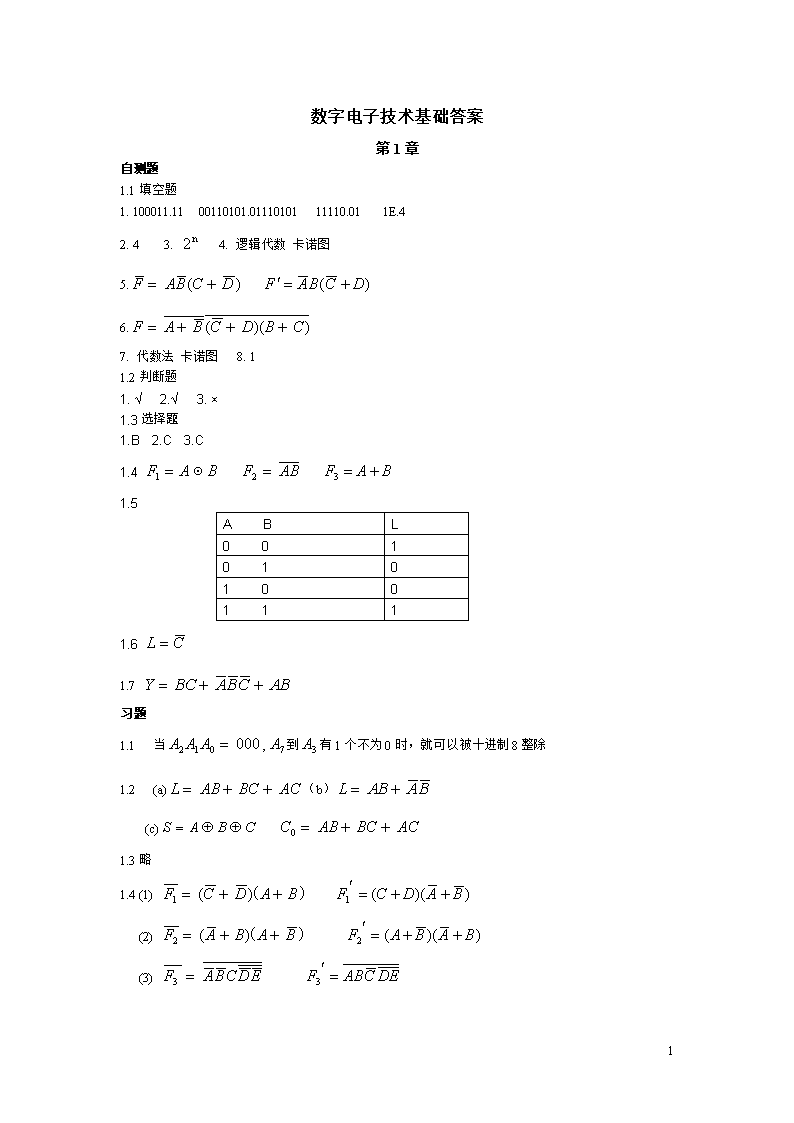

'数字电子技术基础答案第1章自测题1.1填空题1.100011.1100110101.0111010111110.011E.42.43.4.逻辑代数卡诺图5.6.7.代数法卡诺图8.11.2判断题1.√2.√3.×1.3选择题1.B2.C3.C1.4⊙1.5ABL0010101001111.61.7习题1.1当,到有1个不为0时,就可以被十进制8整除1.2(a)(b)(c)1.3略1.4(1)(2)(3)29

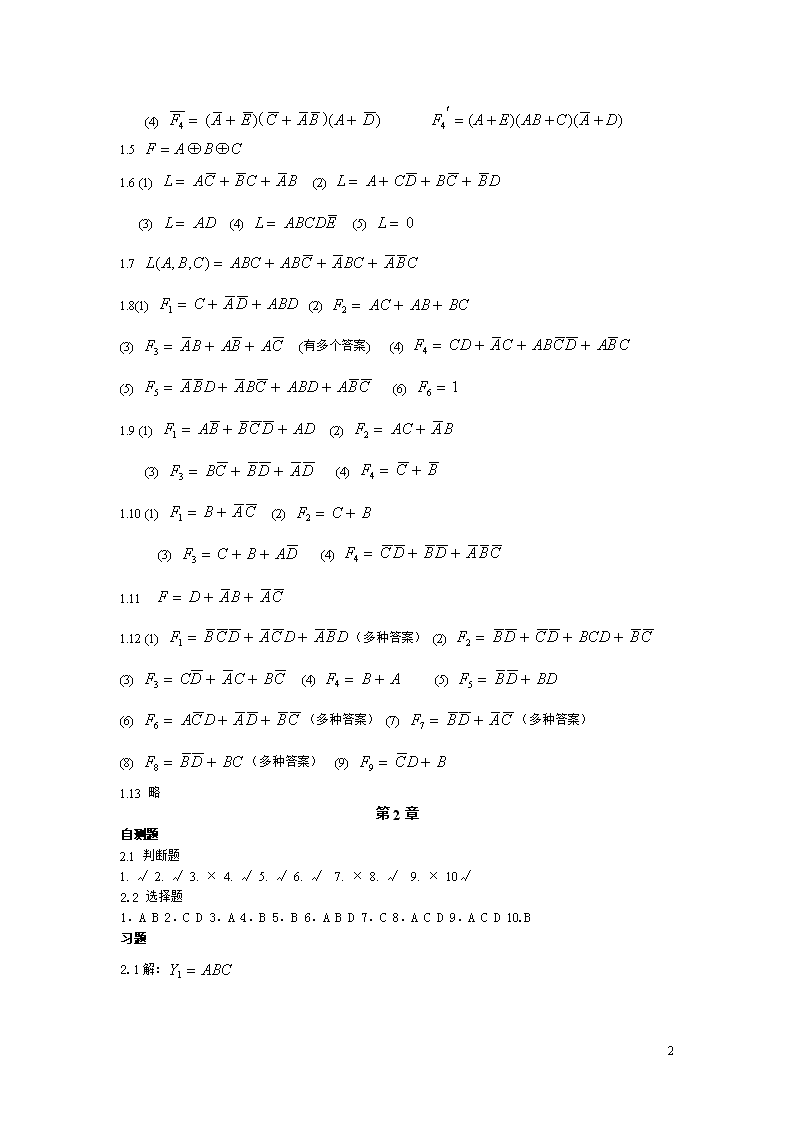

(4)1.51.6(1)(2)(3)(4)(5)1.71.8(1)(2)(3)(有多个答案)(4)(5)(6)1.9(1)(2)(3)(4)1.10(1)(2)(3)(4)1.111.12(1)(多种答案)(2)(3)(4)(5)(6)(多种答案)(7)(多种答案)(8)(多种答案)(9)1.13略第2章自测题2.1判断题1.√2.√3.×4.√5.√6.√7.×8.√9.×10√2.2选择题1.AB2.CD3.A4.B5.B6.ABD7.C8.ACD9.ACD10.B习题2.1解:29

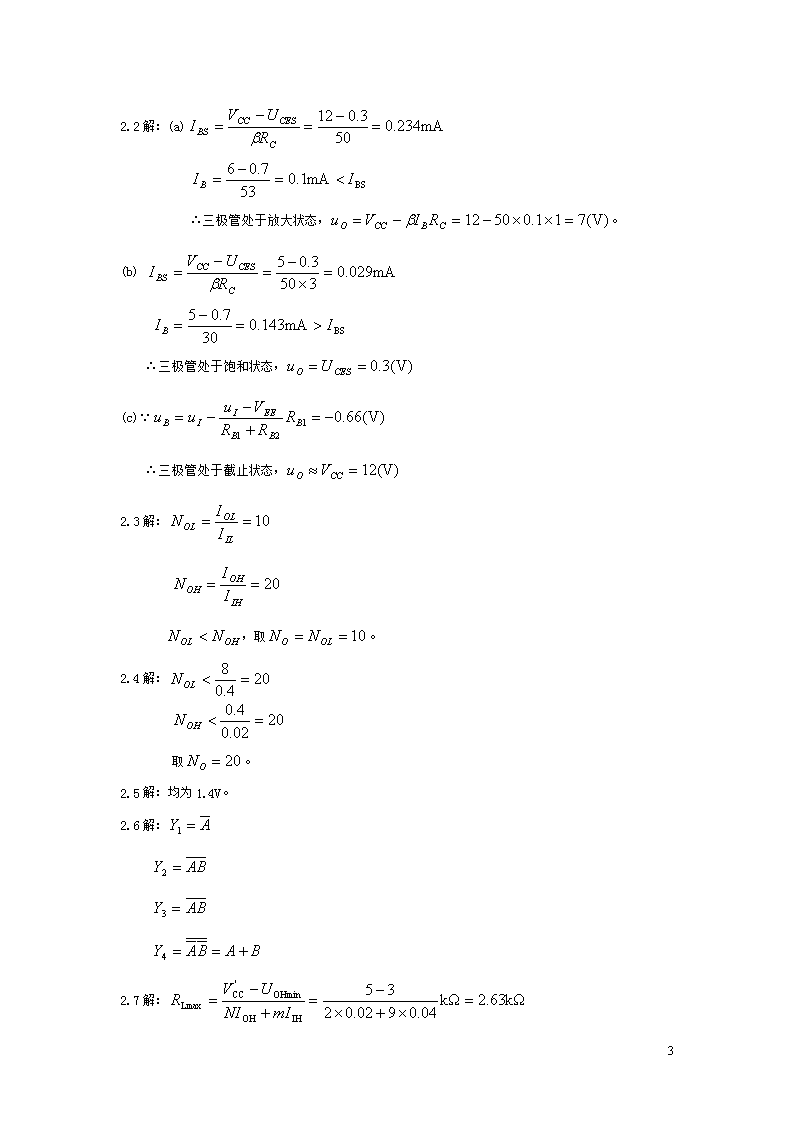

2.2解:(a)∴三极管处于放大状态,。(b)∴三极管处于饱和状态,(c)∵∴三极管处于截止状态,2.3解:,取。2.4解:取。2.5解:均为1.4V。2.6解:2.7解:29

,可以在此范围内选取某一标称阻值,如选或。2.8解:(1):1.4V:0.3V(2):1.4V:0.3V(3):0.3V:3.6V2.9解:(1):3.6V,(2):1.4V,(3):0V,(4):1.4V,2.10解:(a)√(b)×(c)√(d)×2.11解:2.12略2.13略第3章自测题3.1判断题1.×2.√3.√4.√5.×6.√7.×8.×3.2选择题1.CD2.B3.C4.D5.ACD6.A7.E8.D9.C10.C11.C12.D13.AB14.A15.AB3.3填空题1.低电平2.修改逻辑设计接入滤波电容加选通脉冲习题3.1解: (1) 输出函数逻辑表达式为: (2)列出真值表,略(3)分析逻辑功能:当A、B、C三个变量不一致时,电路输出为“1”,所以这个电路,称为“不一致电路”。3.2解:输出函数逻辑表达式为: (2)列出真值表,略(3)分析逻辑功能:该电路是函数发生器。29

3.3解:(a)输出函数逻辑表达式为:,逻辑功能:完成异或运算的逻辑功能。(b)输出函数逻辑表达式为:,逻辑功能:当M=0时,Y=B;当M=1时,Y=A。所以它的功能为:完成二选一数据选择器。 3.4解:(1)列出该组合的真值表如表3-4。 表3-4习题3.4的真值表ABCDF00001000110010100110010010101001100011111000110010101001011111000110111110111111(2)利用卡诺图化简并写出F的与非-与非表达式,画出逻辑电路图。3.5解:(a)Y=X2,2位二进制数的平方最大是1001,输出用4位二进制数Y3~Y0,真值表如表3.5所示。表3.5(a)Y=X2的真值表ABY3Y2Y1Y000000029

010001100100111001 根据真值表3.5(a),写出最简表达式,并转化为与非形式。 Y3= Y2= Y1=0 Y0=B逻辑电路图略。(2)Y=X3,3位二进制数的立方最大是(27)10用5位二进制Y4~Y0表示,真值表如表3.5(b)所示。 表3.5(b)Y=X3的真值表ABY4Y3Y2Y1Y00000000010000110010001111011 根据真值表3.5(b),写出最简表达式,并转化为与非形式,如下所示: Y4= Y3=A Y2=0 Y1= Y0=B实现逻辑电路略。3.6解:首先将F1,F2,F3表示成最小项之和的形式,把二片2线—4线译码器扩展成3线—8线译码器即可实现该多输出函数。实现逻辑电路略。 3.7解:(1) 逻辑电路图略。(2)将二片3线—8线译码器扩展为4线—16线译码器,实现F1,F2。逻辑电路图略。3.8解:(1)将要实现的函数转换3变量的最小项的形式,这3个变量要与74151的3个地址端对应,不妨取A、B、C这3个变量,整理后的式子为:将本题目要实现的组合逻辑函数与74151的输出表达式进行比较。输入变量ABC将接至数据选择器的输入端A2A1A0;输出变量接至数据选择器的输出端;将逻辑函数F的最小项表达式与74151的输出表达式相比较,F式中没有出现的最小项对应的数据输入端应接0,即:D0=D3=D5=D6=0;D1=D2=D4=D7=1。逻辑电路图略。 (2)29

将要实现的函数转换3变量的最小项的形式,这3个变量要与74151的3个地址端对应,不妨取A、B、C这3个变量,整理后的式子为:将本题目要实现的组合逻辑函数与74151的输出表达式进行比较。即可得到如下式子。逻辑电路图略。(3)将要实现的函数转换3变量的最小项的形式,这3个变量要与74151的3个地址端对应,不妨取A、B、C这3个变量,整理后的式子与74151的输出表达式进行比较。即可得到如下式子,画出连接电路图如图3.8(c)所示。逻辑电路图略。3.9解:(1)当T=0时,ABCD作为4变量的最小项可知:F=∑m(8,9,10,11)+∑d(12,13,14,15)当T=1时,ABCD作为4变量的最小项可知:F=∑m(2,3,4,5)+∑d(12,13,14,15)利用卡诺图化简可得表达式:逻辑电路图略。(2)将要实现的函数转换3变量的最小项的形式,这3个变量要与74151的3个地址端对应,不妨取A、B、C这3个变量,整理后的式子与74151的输出表达式进行比较。即可得到如下式子:逻辑电路图略。3.10解:根据数据选择器的功能,写出其函数式:3.11解:列出真值表如表3.11所示,其中A、B、C三个变量表示三个人,Y表示提议是否通过;表3.11ABCY00000010010001111000101111011111(1)写出最简表达式:逻辑电路图略。(2)写出最小项的表达式:Y=m3+m5+m6+m7=逻辑电路图略。29

3.12解:表3.12DCBAY3Y2Y1Y000110000010000010101001001100011011101001000010110010110101001111011100011001001(1)利用卡诺图化简,写出输出的最简表达式:逻辑电路图略。(2)根据真值表可得:Y3Y2Y1Y0=DCBA-0011可用74283表示减法运算,Y3Y2Y1Y0=DCBA-0011=DCBA+1100+1。逻辑电路图略。3.13解:根据真值表写出表达式:把上式表示成G1G0A这三个变量的最小项的形式,即可得到如下的式子:上式和8选一数据选择器的标准式子相比较,可以得到逻辑电路图略。3.14解:这实际是利用数据选择器的使能端将若干片4选1扩展为20选1。20选1的地址变量为5个,故高3位作为译码器的变量输入,译码器的输出作为4选1的选片信号,低2位作为4选1的地址变量。根据以上原理用5片4选1和3线—8线译码器及或门组成20选1。29

图3.14 3.15解: 图3.153.16解:该电路完成两个3位二进制数是否相同比较功能的电路。3.17解:将电路分成三个功能块:加法运算电路及比较器、译码电路、显示电路;分析各个功能块的逻辑功能:加法器的输出是A3~A0与B3~B0的和;比较器完成的是当加法器输出的和小于1010时,比较电路的输出YA

您可能关注的文档

- 商务谈判课后答案.doc

- 商品学概论练习题材及答案.doc

- 商品学概论试题及答案(汇总).doc

- 商品学试题及答案.doc

- 商师《土力学与基础工程》第三版(赵明华)课后习题答案武汉理工大学出版社.pdf

- 商法练习题答案.doc

- 商法网络课答案.docx

- 商法课后答案.doc

- 商用车汽车装配工助理操作师和操作师题库(带答案).doc

- 四川航天职业技术学院《互换性与测量技术基础》习题及答案汇总.doc

- 固体废物习题及答案.doc

- 固体物理习题与答案.doc

- 固体物理习题及答案汇总整理终极版.doc

- 固体物理习题解答-完整版.pdf

- 固体物理习题解答.pdf

- 固体物理基础参考解答.pdf

- 固体物理学习题解答(完整版).doc

- 固体物理学答案(朱建国版).doc

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明