- 240.18 KB

- 2022-04-22 11:30:48 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'课后答案网,用心为你服务!大学答案---中学答案---考研答案---考试答案最全最多的课后习题参考答案,尽在课后答案网(www.khdaw.com)!Khdaw团队一直秉承用心为大家服务的宗旨,以关注学生的学习生活为出发点,旨在为广大学生朋友的自主学习提供一个分享和交流的平台。爱校园(www.aixiaoyuan.com)课后答案网(www.khdaw.com)淘答案(www.taodaan.com)

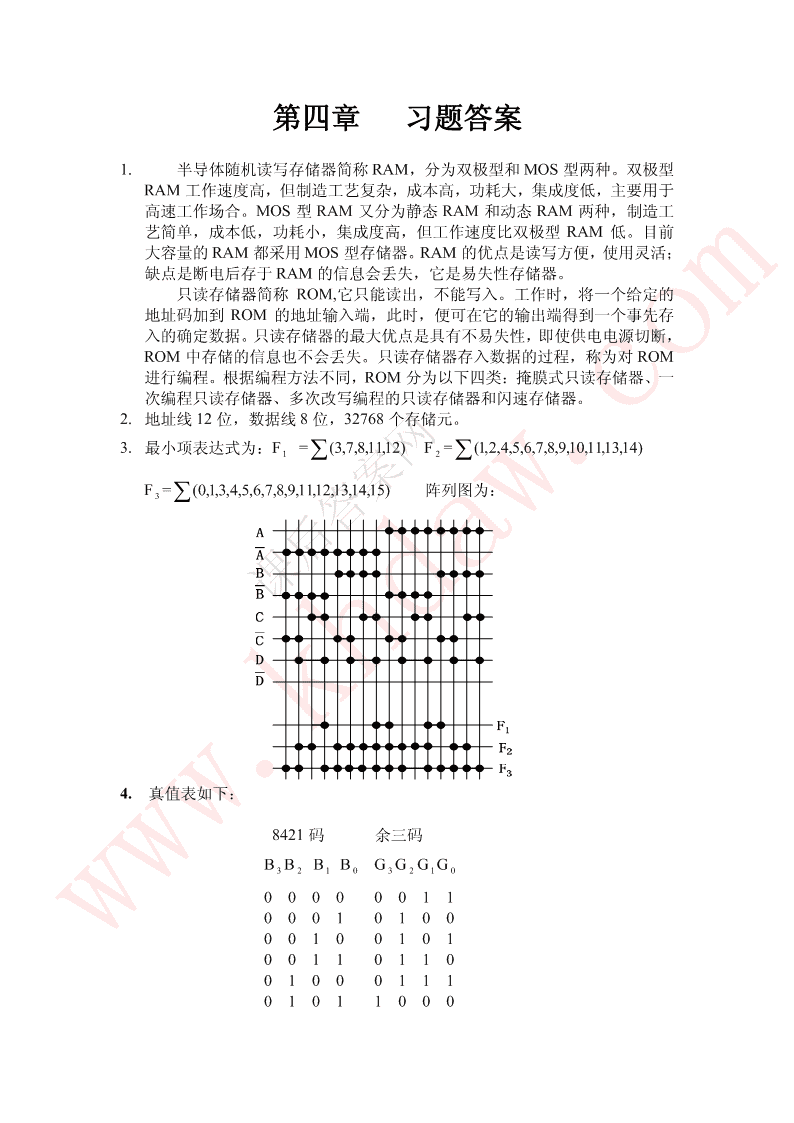

第四章习题答案1.半导体随机读写存储器简称RAM,分为双极型和MOS型两种。双极型RAM工作速度高,但制造工艺复杂,成本高,功耗大,集成度低,主要用于高速工作场合。MOS型RAM又分为静态RAM和动态RAM两种,制造工艺简单,成本低,功耗小,集成度高,但工作速度比双极型RAM低。目前大容量的RAM都采用MOS型存储器。RAM的优点是读写方便,使用灵活;缺点是断电后存于RAM的信息会丢失,它是易失性存储器。只读存储器简称ROM,它只能读出,不能写入。工作时,将一个给定的地址码加到ROM的地址输入端,此时,便可在它的输出端得到一个事先存入的确定数据。只读存储器的最大优点是具有不易失性,即使供电电源切断,ROM中存储的信息也不会丢失。只读存储器存入数据的过程,称为对ROM进行编程。根据编程方法不同,ROM分为以下四类:掩膜式只读存储器、一次编程只读存储器、多次改写编程的只读存储器和闪速存储器。2.地址线12位,数据线8位,32768个存储元。3.最小项表达式为:F1=(3,7,8,11,12)F2=(1,2,4,5,6,7,8,9,10,11,13,14)F3=(0,1,3,4,5,6,7,8,9,11,12,13,14,15)阵列图为:4.真值表如下:8421码余三码BBBBGGGG32103210000000110001010000100101001101100100011101011000

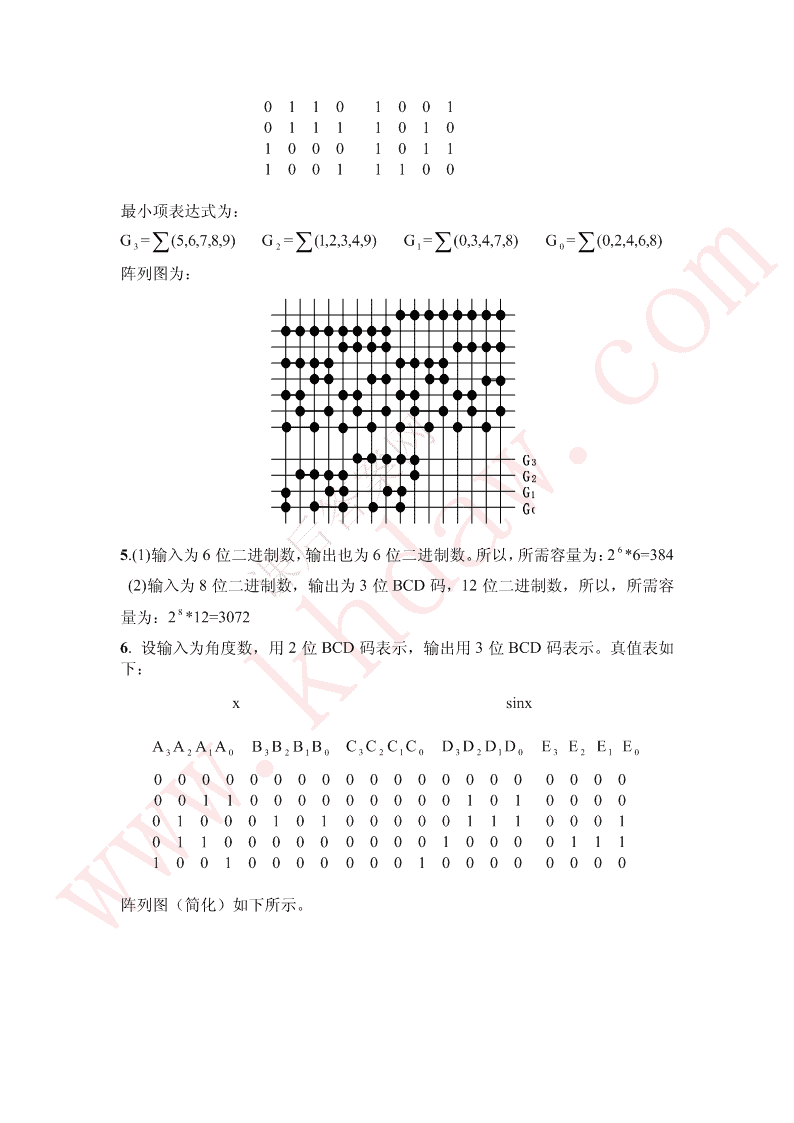

01101001011110101000101110011100最小项表达式为:G3=(5,6,7,8,9)G2=(1,2,3,4,9)G1=(0,3,4,7,8)G0=(0,2,4,6,8)阵列图为:65.(1)输入为6位二进制数,输出也为6位二进制数。所以,所需容量为:2*6=384(2)输入为8位二进制数,输出为3位BCD码,12位二进制数,所以,所需容8量为:2*12=30726.设输入为角度数,用2位BCD码表示,输出用3位BCD码表示。真值表如下:xsinxAAAABBBBCCCCDDDDEEEE321032103210321032100000000000000000000000110000000001010000010001010000011100010110000000001000011110010000000100000000阵列图(简化)如下所示。

7.经化简得F=ACD+ACD+BCDF=AB+AB+CD+CDF=B+C+D123阵列图为:8.真值表见第四题。经化简得:G=BBB+BBB+BBB3321321320G=BBB+BBB+BBBB23212103210G=BBB+BBB+BBB1310210310G=BB+BBB阵列图为:030210

9.真值表如下:ABCF1F2F3F4F5F6000000000001000001010000100011001001100010000101011001110100100111110001F=ABF=AB+ACF=ABC+ABCF=BCF=0F=C123456用FPLA较好,可节省空间。阵列图如下:10.真值表为:F=ABD+BCD+AC1F=ACD+ABC+ABCD+ABCD+ABC+ACD2F=BD+BD3ABCDF1F2F300000000001001001001000110110100001010101001100110111100100001010010111010100

10111011100011110110011101011111110阵列图如下:11.真值表为:n1n1n1n1Q4Q3Q2Q1Q4Q3Q2Q1Z000000010000100110001100100001001100011001110011101010010101000010011000110011010

110100001n1n1化简得:Q=QQQQ=QQ+QQ+QQ43213432131n1n1Q=QQ+QQQ=QQ+QQ+QQ221311324132用D触发器实现,可得阵列图如下:

12.5421BCD同步计数器状态转换表如下页所示:n1n1由该表可得Q=QQ+QQQ=QQQ443433321n1n1Q=QQ+QQQ=QQ所以,22121131J=K=QJ=QQK=1J=K=QJ=QK=14433213221131n1n1n1n1Q4Q3Q2Q1QQQQZ43210000000100001001000010001100011010000100100001000100101001101001010101101011110001100000015421BCD七段显示译码真值表如下:DCBAabcdefg显示000000000010000110011111001000100102001100001103010010011004100001001005100101000006101000011117101100000008110000001009由于DCBA=QQQQ,所以可化简得到4321a=QQ+QQQb=QQQc=QQQ43421432421d=QQ+QQQ+QQQe=Q+QQ+QQ4342142134141f=QQ+QQg=QQQ+QQQ2141432421阵列图如下页所示

13.ACAC(n)=00时OLMC的简化逻辑图如下:01专用组合输出结构ACAC(n)=01时OLMC的简化逻辑图如下:01

专用输入结构ACAC(n)=10时OLMC的简化逻辑图如下:01寄存器模式ACAC(n)=11时OLMC的简化逻辑图如下:01时序电路组合输入输出结构

选通组合输出结构14.组合方式下,15脚和16脚没有和邻级相连,所以不能当输入端使用。允许的输入信号最多为14个,分布在2~9脚、12、13、14、17、18和19脚上。带反馈的组合方式下,19脚和12脚要为1脚和11脚提供到与阵列的通路,所以不能当输入端使用。允许的输入信号最多为14个,分布在2~9脚、13、14、15、16、17和18脚上。寄存器方式下,2~9脚和12~19脚均可作为输入信号使用。所以最多有16个。15.moduledecoderA0..A7pin1..8;CS0..CS4pin10..14;ABUS=[A0..A7];CS=[CS0..CS4];EquationsCS0=((ABUS>=^h0F0)&(ABUS<=^h0FF));CS1=((ABUS>=^h070)&(ABUS<=^h0EF));CS2=((ABUS>=^h0F)&(ABUS<=^h0F));CS3=((ABUS>=^h0C)&(ABUS<=^h0D));CS4=((ABUS>=^h08)&(ABUS<=^h0B));enddecoder16.moduledcountflag‘-r3’title‘counter’GAL2device‘P16V8R’;CLK,C1,C0,OEpin1,2,3,11;Q3,Q2,Q1,Q0pin14,15,16,17;D3,D2,D1,D0pin4,5,6,7;CK,X,Z=.c.,.x.,.z.;mode=[C1,C0];clear=[0,0];load=[0,1];down=[1,0];

up=[1,1];S0=^b1111;S1=^b1110;S2=^b1101;S3=^b1100;S4=^b1011;S5=^b1010;S6=^b1001;S7=^b1000;S8=^b0111;S9=^b0110;Equations![Q3,Q2,Q1,Q0]:=(mode==clear)&![1,1,1,1];![Q3,Q2,Q1,Q0]:=(mode==load)&![D3,D2,D1,D0];State_diagram[Q3,Q2,Q1,Q0]StateS0:case(mode==up):S1;(mode==down):S9;endcase;StateS1:case(mode==up):S2;(mode==down):S0;endcase;StateS2:case(mode==up):S3;(mode==down):S1;endcase;StateS3:case(mode==up):S4;(mode==down):S2;endcase;StateS4:case(mode==up):S5;(mode==down):S3;endcase;StateS5:case(mode==up):S6;(mode==down):S4;endcase;StateS6:case(mode==up):S7;(mode==down):S5;endcase;StateS7:case(mode==up):S8;(mode==down):S6;endcase;StateS8:case(mode==up):S9;(mode==down):S7;endcase;StateS9:case(mode==up):S0;(mode==down):S8;endcase;[CK,0,load,1,1,0,0]->S3;[CK,0,up,X,X,X,X,]->S4;[CK,0,load,0,1,1,0]->S9;enddcount17.modulecountertitle‘Acontrolledcounter’;

Q0..Q3pin12..15istype’reg’;CLK,Cpin1,2;Q=[Q0..Q3];EquationsQ:=(Q+1)&C;Q:=(Q==9)&!C&[0,0,0,0]#(Q+1)&(Q!=9);Q.c=CLK;Endcounter18.EPROM的存储内容可以根据需要来写入,当需要更新存储内容时还可以将原存储内容抹去,再写入新的内容。他的与阵列是固定的,或阵列是可编程的。FPLA是将ROM中的地址译码器改为乘积项发生器的一种可编程逻辑器件。它的与阵列和或阵列均可编程,既可实现组合逻辑,也可实现时序逻辑。GAL是PAL的换代产品。从基本原理来说,GAL期间仍采用与-或阵列结构。它是一种电可擦除的编程器件,采用“输出逻辑宏单元”结构大大增强了逻辑上的灵活性,使得一种GAL器件可以替代许多种PAL器件,特别适合于研制开发阶段使用。FPGA是一种可编程的大规模集成器件,它既有门阵列的结构和性能,又具有现场可编程的特点,而且可以反复地擦除和重新编程,适用于ASIC的研制。FPGA的体系结构核心是可组态的逻辑块。19.modulesetopaSCK,SDIpin1,2;ACKpin3;Q0..Q3pin16..19istype‘reg’;OEpin11;INTpin13istype‘reg’;Q=[INT,Q3..Q0];EquationsQ:=!ACK&[Q3,Q2,Q1,Q0,SDI]#ACK&[0,0,0,0,1];Q.c=SCK;Q.oe=OE;Endsetopa20.modulebukcodeCLK,RSTpin1,2;Q0..Q2pin13..15istype‘reg’;OUTpin16;Q=[Q0..Q2];S0=[0,0,0];S1=[0,0,1];S2=[0,1,0];S3=[0,1,1];S4=[1,0,0];

S5=[1,0,1];S6=[1,1,0];State_diagramQstateS0:ifRST==0thenS1withOUT=1;ElseS0;stateS1:ifRST==0thenS2withOUT=1;ElseS0;stateS2:ifRST==0thenS3withOUT=1;ElseS0;stateS3:ifRST==0thenS4withOUT=0;ElseS0;stateS4:ifRST==0thenS5withOUT=0;ElseS0;stateS5:ifRST==0thenS6withOUT=1;ElseS0;stateS6:ifRST==0thenS0withOUT=0;ElseS0;EquationsQ.c=CLK;Endbukcode'

您可能关注的文档

- 数字电子技术基础 (毛炼成 谈进 著) 人民邮电出版社 课后答案

- 数字电子技术基础 (伍时和 吴友宇 著) 清华大学出版社 课后答案

- 数字电子技术基础 第二版 (侯建军 著) 高等教育出版社 课后答案

- 数字电子技术基础 第二版 (沈任元 著) 机械工业出版社 课后答案

- 数字电子技术基础

- 数字逻辑电路 (魏达 高强 金玉善 曹英晖 著) 科学出版社 课后答案

- 数字逻辑与数字系统 第四版 (白中英 著) 科学出版社 课后答案 chapter1 课后答案【】

- 数字逻辑与数字系统 第四版 (白中英 著) 科学出版社 课后答案 chapter2 课后答案【】

- 数字逻辑与数字系统 第四版 (白中英 著) 科学出版社 课后答案 chapter3 课后答案【】

- 数字逻辑与数字系统 第四版 (白中英 著) 科学出版社 课后答案 chapter5 课后答案【】

- 数字逻辑与数字系统 第四版 (白中英 著) 科学出版社 课后答案 chapter6 课后答案【】

- 数字逻辑与数字系统设计 (王永军 李景华 著) 高等教育出版社 课后答案

- 数字设计 第四版 英文 (Mano Ciletti 马诺 著) 电子工业出版社 课后答案

- 数字通信 基础与应用 第二版 (Bernard Sklar 著) 电子工业出版社 课后答案

- 数字图像处理 (胡学龙 许开宇 著) 电子工业出版社 课后答案

- 数字图像处理 第二版 (夏良正 著) 东南大学出版社 课后答案

- 数字图像处理 第三版 (冈萨雷斯 著) 电子工业出版社 部分答案 课后答案

- 数字信号处理 (刘兴钊 著) 电子工业出版社 课后答案

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明