- 1.10 MB

- 2022-04-22 11:51:14 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

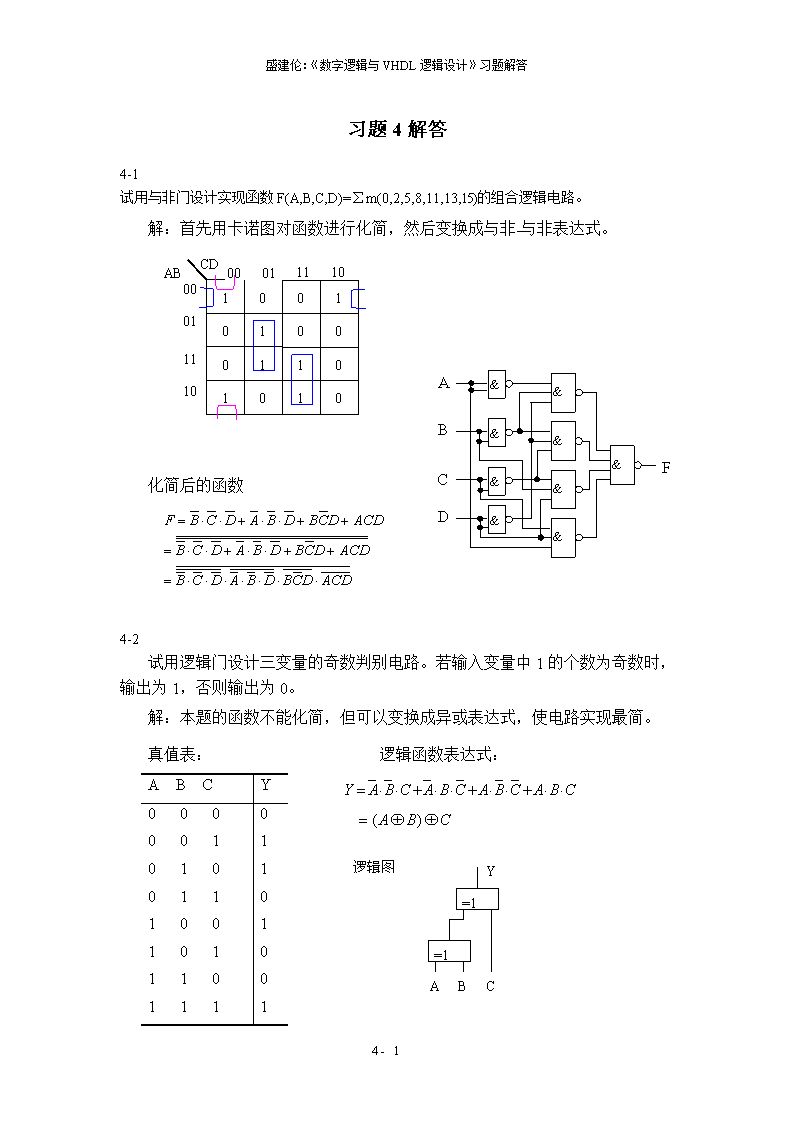

'盛建伦:《数字逻辑与VHDL逻辑设计》习题解答习题4解答4-1试用与非门设计实现函数F(A,B,C,D)=Σm(0,2,5,8,11,13,15)的组合逻辑电路。解:首先用卡诺图对函数进行化简,然后变换成与非-与非表达式。AB1001CD0001000101001110011010101110&&&&&&&化简后的函数&&4-2试用逻辑门设计三变量的奇数判别电路。若输入变量中1的个数为奇数时,输出为1,否则输出为0。解:本题的函数不能化简,但可以变换成异或表达式,使电路实现最简。真值表:逻辑函数表达式:ABCY=1=1ABCY逻辑图00000101001110010111011101101001224-

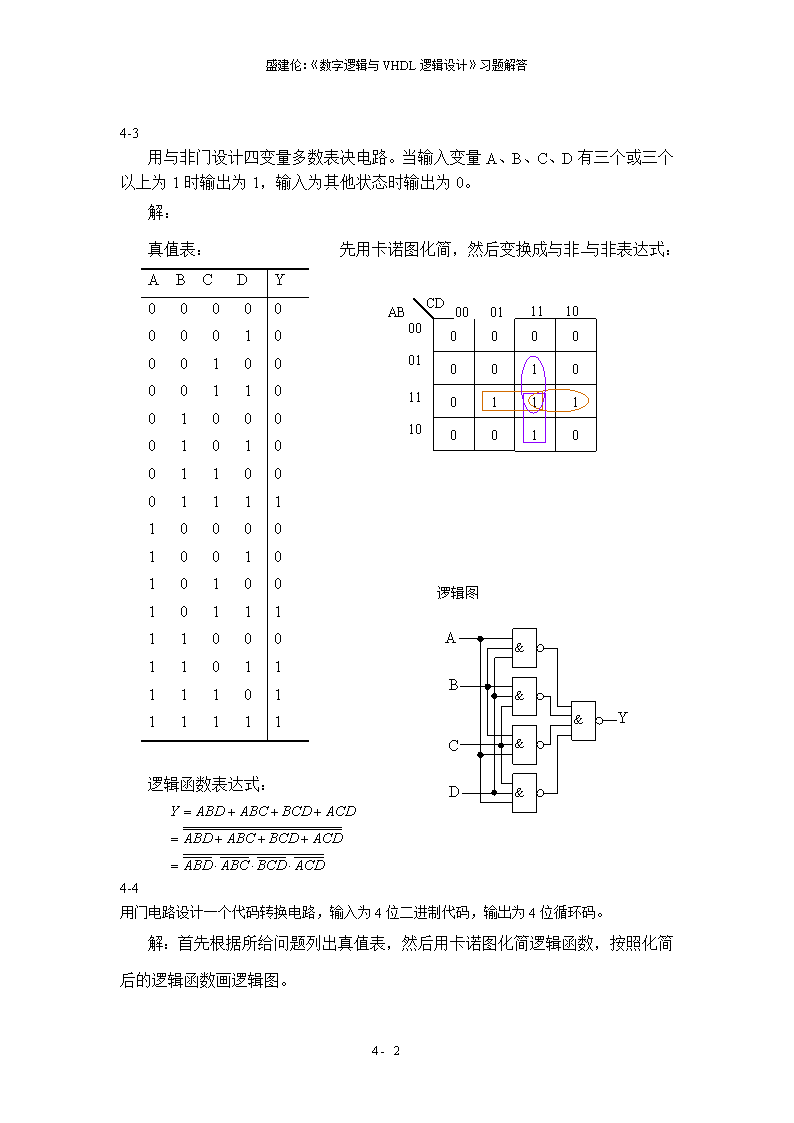

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答4-3用与非门设计四变量多数表决电路。当输入变量A、B、C、D有三个或三个以上为1时输出为1,输入为其他状态时输出为0。解:真值表:先用卡诺图化简,然后变换成与非-与非表达式:AB0000CD0001000100101110010011101110ABCDY逻辑图&&&&&00000001001000110100010101100111100010011010101111001101111011110000000100010111逻辑函数表达式:4-4用门电路设计一个代码转换电路,输入为4位二进制代码,输出为4位循环码。解:首先根据所给问题列出真值表,然后用卡诺图化简逻辑函数,按照化简后的逻辑函数画逻辑图。224-

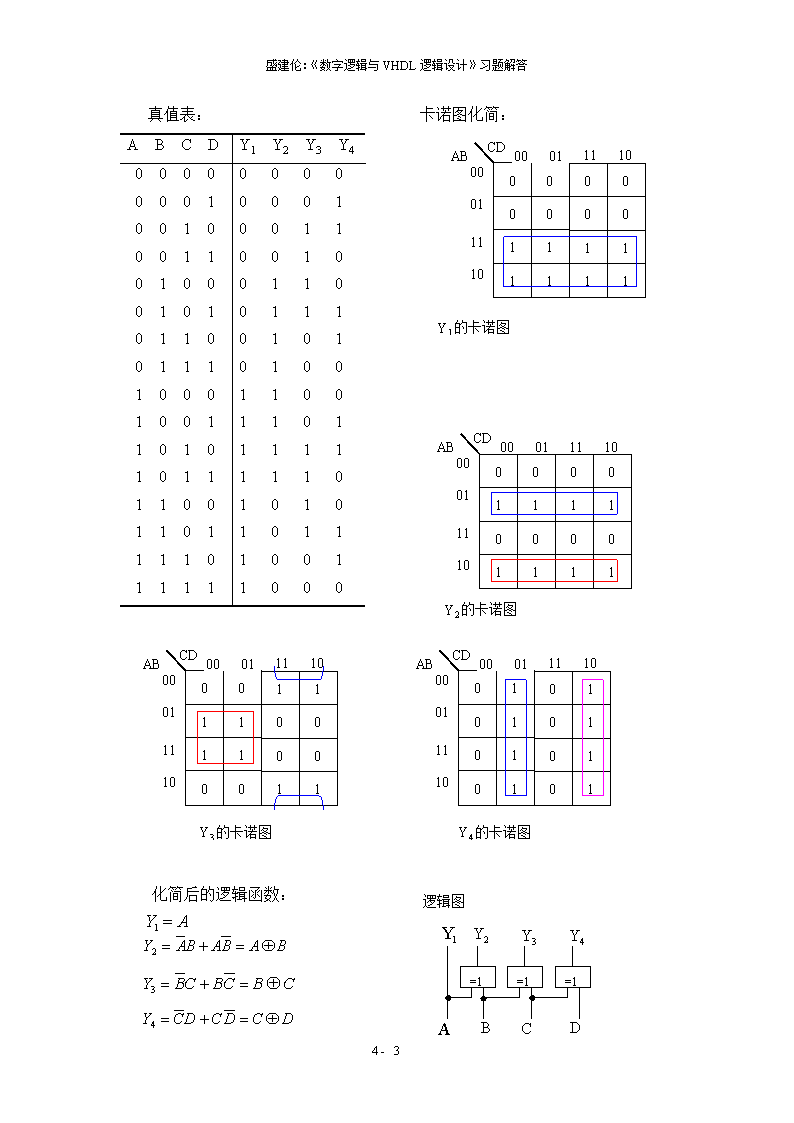

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答真值表:卡诺图化简:AB0000CD0001000100001110111111111110ABCDY1Y2Y3Y4AB0011CD0001000100111110001100111110Y1的卡诺图00000001001000110100010101100111100010011010101111001101111011110000000100110010011001110101010011001101111111101010101110011000AB0101CD0001000101011110010101011110Y3的卡诺图AB0011CD0001000111001110110000111110Y4的卡诺图Y2的卡诺图逻辑图化简后的逻辑函数:=1=1=1224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答4-5图4.48所示是一个由两台水泵向水池供水的系统。水池中安置了A、B、C三个水位传感器。当水池水位低于C点时,两台水泵同时供水。当水池水位低于B点且高于C点时,由水泵M1单独供水。当水池水位低于A点且高于B点时,由水泵M2单独供水。当水池水位高于A点时,两台水泵都停止供水。试设计一个水泵控制电路。要求电路尽可能简单。图4.48习题4-5的示意图解:设水位低于传感器时,水位传感器的输出为1,水位高于传感器时,水位传感器的输出为0。A0×0×BC000101××111110A0×1×BC000101××101110首先根据所给问题列出真值表。其中有几种情况是不可能出现的,用约束项表示。ABCM1M2M1的卡诺图M2的卡诺图00000101001110010111011100××××××01××1011如果利用约束项化简如果不利用约束项化简逻辑图=&&≥1&1(a)用约束项化简(b)不用约束项化简224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答习题4-5的逻辑图4-6试用3线-8线译码器74HC138和门电路实现如下多输出逻辑函数并画出逻辑图。解:先将逻辑函数变换成最小项之和的形式逻辑图再变换成与74HC138一致的形式1CBAY1&&&Y2Y3&Y4令74HC138的A2=A,A1=B,A0=C,4-7试用3线-8线译码器74HC138和逻辑门设计一组合电路。该电路输入X,输出Y均为3位二进制数。二者之间关系如下:当2≤X<7时,Y=X-2X<2时,Y=1X=7时,Y=6逻辑图解:首先根据所给问题列出真值表。1X0X1X2Y2A2A1A074HC138&Y1Y0&&X2X1X0Y2Y1Y0000001010011100101001001000001010011224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答110111100110逻辑函数:4-8试用4选1数据选择器产生逻辑函数解:将逻辑函数变换成最小项之和的形式若用输入变量AB作为地址,C作为数据输入,则即A1=A,A0=B,D0=D2=,D1=1,D3=C。逻辑图如下图(a)所示。若用输入变量AC作为地址,B作为数据输入,则即A1=A,A0=C,D0=1,D2=,D1=D3=B。逻辑图如下图(b)所示。A1A0D3D2D1D04选1数据选择器Y1A1A0D3D2D1D04选1数据选择器Y1(a)AB作为地址(b)AC作为地址4-9分析图4.49所示电路,写出输出Y的逻辑函数式并化简。A0D0D1D2D3D4D5D6D7A18选1数据选择器A2F224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答图4.49习题4-9的电路解:8选1数据选择器C=A2,B=A1,A=A0,D7=D3=0,D2=1,D5=D4=D1=D0=D,D6=,逻辑函数卡诺图化简DC0000BA0001000101011110111100011110化简后的逻辑函数4-10试用8选1数据选择器产生逻辑函数解:令A=A2,B=A1,C=A0,D7=D5=D2=D1=1,D6=D4=D3=D0=0,逻辑图A2D0D1D2D3D4D5D6D7A18选1数据选择器A0Z4-11试用3线-8线译码器74HC138和最少数量的二输入逻辑门设计一个不一致电路。当A、B、C三个输入不一致时,输出为1,三个输入一致时,输出为0。224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答解:首先根据所给问题列出真值表。真值表:ABCY00000101001110010111011101111110如果直接按照真值表写出逻辑函数表达式,很难用二输入逻辑门实现。但是,观察真值表不难发现,真值表中只有两行的Y为0,因此,按照真值表写出反函数表达式,应该容易用二输入逻辑门实现。逻辑函数表达式:题目要求用3线-8线译码器74HC138实现,而74HC138的每个输出对应一个最小项的反,因此,还必须把逻辑函数式变换成与74HC138的逻辑函数相同的形式。逻辑图逻辑图逻辑图A2A1A0&1ABCY74HC138224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答4-12试用8选1数据选择器产生逻辑函数解:如果用ABC作为数据选择器的地址(A=A2,B=A1,C=A0),D作为数据,则函数变换成A0D0D1D2D3D4D5D6D7A18选1数据选择器A2FD7=D6=D3=1,D5=D0=0,D4=D1=D,D2=,如果用BCD作为数据选择器的地址(B=A2,C=A1,D=A0),A作为数据,则函数变换成A0D0D1D2D3D4D5D6D7A18选1数据选择器A2FD7=D6=D4=1,D2=D0=0,D5=D1=A,D3=4-13根据表4.23所示的功能表设计一个函数发生器电路,用8选1数据选择器实现。表4.23习题4-13的功能表S1S0Y00A⊙B224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答011011A·BA+B解:首先根据所给问题列出真值表。真值表:卡诺图化简S1S01000AB0001000110101110010101111110S1S0ABY00000001001000111001010001010110011100011000100110101011011111001101111011110110化简后用S1AB作为地址,S0作为数据输入,即S1=A2,A=A1,B=A0。函数变换为1A0D0D1D2D3D4D5D6D7A18选1数据选择器A2FD6=D5=D3=1,D1=D2=D4=0,D7=D0=,因此,画出逻辑图如下:逻辑图224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答4-14图4.50所示是由3线8线译码器74HC138和8选1数据选择器构成的电路。试分析①当数据C2C1C0=D2D1D0时,输出F=?②当数据C2C1C0≠D2D1D0时,输出F=?74HC138图4.50习题4-14的电路解:①当数据C2C1C0=D2D1D0时,输出F=0②当数据C2C1C0≠D2D1D0时,输出F=1这个电路可以检验数据C2C1C0与D2D1D0是否相同。4-15设计用3个开关控制一个电灯的逻辑电路,要求改变任何一个开关的状态都能控制电灯由亮变灭或者由灭变亮。用数据选择器实现。解:用A、B、C分别表示3个开关的状态,Z=1表示电灯亮,Z=0表示电灯灭。令ABC=000时的状态Z=0。(注:此处先用格雷码写出变化表比较容易得真值表,初始状态也很重要)真值表:逻辑函数表达式:ABCZ00000101001110010111011101101001224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答A1A0D3D2D1D04选1数据选择器Y13个变量,可以用4选1数据选择器实现。若用输入变量AB作为地址,C作为数据输入,即A1=A,A0=B,D0=D3=C,D1=D2=。逻辑图4-16试用逻辑门设计一个带控制端的半加/半减器,控制端X=1时为半加器,X=0时为半减器。解:根据所给问题列出真值表。A、B为加/减的两个数。做加法运算时,S为半加/半减的和/首先差的输出,CO为进位输出。做减法运算时,S为差的输出,CO为借位输出。半加器的功能是S=A+B。半减器的功能是S=A-B。真值表:XABSCO0000010100111001011101110011100000101001=1&SCOAB=逻辑函数不能化简,但是可以变换成异或表达式。按照变换后的逻辑函数画逻辑图。4-17试用3线-8线译码器74HC138和门电路设计一个1位二进制全减器电路。输入是被减数、减数和来自低位的借位;输出是两数之差和向高位的借位信号。解:全减器的功能是Si=Ai-Bi-Ci。首先根据所给问题列出真值表。真值表:逻辑函数:AiBiCiSiCO224-

盛建伦:《数字逻辑与VHDL逻辑设计》习题解答0000010100111001011101110011110110000011把逻辑函数式变换成与74HC138的逻辑函数相同的形式:CiBiAiSiA2A1A074HC138&CO&逻辑图4-18试用4位数据比较器CC14585设计一个判别电路。若输入的数据代码D3D2D1D0>1001时,判别电路输出为1,否则输出为0。解:从CC14585的一个端口输入数据D3D2D1D0,另一个端口输入1001。CC14585的扩展输入端IA>B和IA=B必须接高电平,IA

您可能关注的文档

- 数字电子技术基础课后答案 阎石 第五版 第一章第二章 习题答案.pdf

- 数字电子技术第三章习题答案.doc

- 数字电子技术课后习题答案(全部).doc

- 数字电路与系统设计课后答案.pdf

- 数字电路与逻辑设计课后答案邹红.pdf

- 数字电路习题解答.doc

- 数字电路逻辑设计课后答案.docx

- 数字通信原理课后习题答案.doc

- 数字逻辑习题答案 毛法尧 第二版.doc

- 数字逻辑设计基础答案 (第1-13章).pdf

- 数字集成电路教程课后答案.pdf

- 数学书籍推荐.docx

- 数学新浙教版八年级5.1《常量与变量》同步练习题【带详解答案】.doc

- 数学模型第三版(高等教育出版社)课后习题答案.doc

- 数学模型第三版)课后习题答案.doc

- 数学模型第三版_课后习题答案.doc

- 数学模型第四版课后答案姜启源版.doc

- 数学物理方程与特殊函数(王元明)课后答案.pdf

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明