- 5.46 MB

- 2022-04-22 11:51:08 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

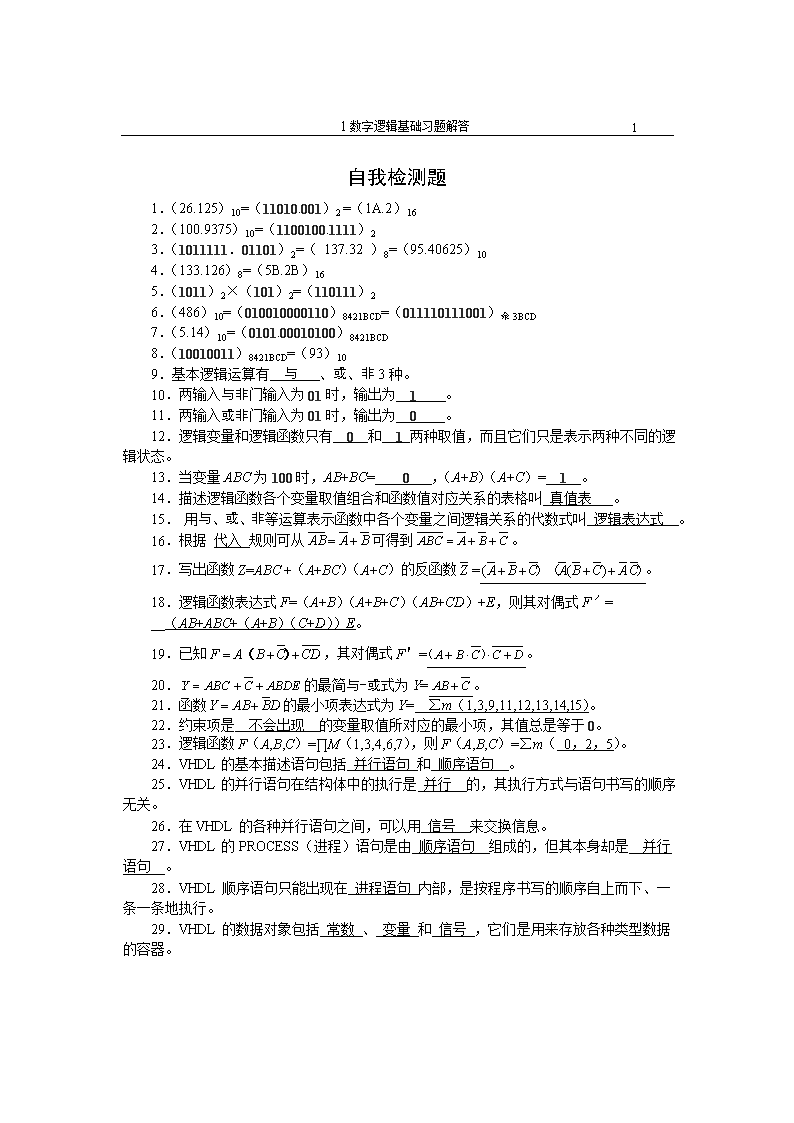

'1数字逻辑基础习题解答140自我检测题1.(26.125)10=(11010.001)2=(1A.2)162.(100.9375)10=(1100100.1111)23.(1011111.01101)2=(137.32)8=(95.40625)104.(133.126)8=(5B.2B)165.(1011)2×(101)2=(110111)26.(486)10=(010010000110)8421BCD=(011110111001)余3BCD7.(5.14)10=(0101.00010100)8421BCD8.(10010011)8421BCD=(93)109.基本逻辑运算有与、或、非3种。10.两输入与非门输入为01时,输出为1。11.两输入或非门输入为01时,输出为0。12.逻辑变量和逻辑函数只有0和1两种取值,而且它们只是表示两种不同的逻辑状态。13.当变量ABC为100时,AB+BC= 0,(A+B)(A+C)=__1__。14.描述逻辑函数各个变量取值组合和函数值对应关系的表格叫真值表。15.用与、或、非等运算表示函数中各个变量之间逻辑关系的代数式叫逻辑表达式。16.根据代入规则可从可得到。17.写出函数Z=ABC+(A+BC)(A+C)的反函数=。18.逻辑函数表达式F=(A+B)(A+B+C)(AB+CD)+E,则其对偶式F'=__(AB+ABC+(A+B)(C+D))E。19.已知,其对偶式F'=。20.的最简与-或式为Y=。21.函数的最小项表达式为Y=∑m(1,3,9,11,12,13,14,15)。22.约束项是不会出现的变量取值所对应的最小项,其值总是等于0。23.逻辑函数F(A,B,C)=∏M(1,3,4,6,7),则F(A,B,C)=∑m(0,2,5)。24.VHDL的基本描述语句包括并行语句和顺序语句。25.VHDL的并行语句在结构体中的执行是并行的,其执行方式与语句书写的顺序无关。26.在VHDL的各种并行语句之间,可以用信号来交换信息。27.VHDL的PROCESS(进程)语句是由顺序语句组成的,但其本身却是并行语句。28.VHDL顺序语句只能出现在进程语句内部,是按程序书写的顺序自上而下、一条一条地执行。29.VHDL的数据对象包括常数、变量和信号,它们是用来存放各种类型数据的容器。

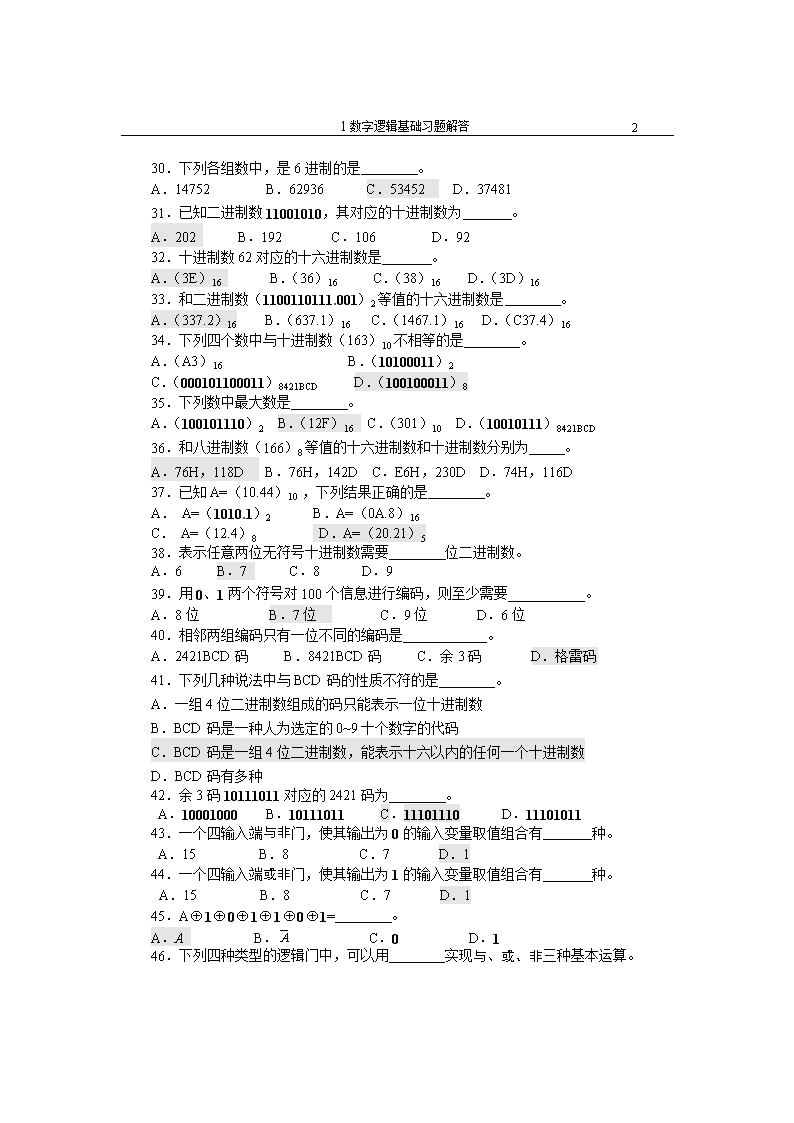

1数字逻辑基础习题解答14030.下列各组数中,是6进制的是。A.14752B.62936C.53452D.3748131.已知二进制数11001010,其对应的十进制数为。A.202B.192C.106D.9232.十进制数62对应的十六进制数是。A.(3E)16B.(36)16C.(38)16D.(3D)1633.和二进制数(1100110111.001)2等值的十六进制数是。A.(337.2)16B.(637.1)16C.(1467.1)16D.(C37.4)1634.下列四个数中与十进制数(163)10不相等的是。A.(A3)16B.(10100011)2C.(000101100011)8421BCDD.(100100011)835.下列数中最大数是。A.(100101110)2B.(12F)16C.(301)10D.(10010111)8421BCD36.和八进制数(166)8等值的十六进制数和十进制数分别为。A.76H,118DB.76H,142DC.E6H,230DD.74H,116D37.已知A=(10.44)10,下列结果正确的是。A.A=(1010.1)2B.A=(0A.8)16C.A=(12.4)8D.A=(20.21)538.表示任意两位无符号十进制数需要位二进制数。A.6B.7C.8D.939.用0、1两个符号对100个信息进行编码,则至少需要。A.8位B.7位C.9位D.6位40.相邻两组编码只有一位不同的编码是。A.2421BCD码B.8421BCD码C.余3码D.格雷码41.下列几种说法中与BCD码的性质不符的是。A.一组4位二进制数组成的码只能表示一位十进制数B.BCD码是一种人为选定的0~9十个数字的代码C.BCD码是一组4位二进制数,能表示十六以内的任何一个十进制数D.BCD码有多种42.余3码10111011对应的2421码为。A.10001000B.10111011C.11101110D.1110101143.一个四输入端与非门,使其输出为0的输入变量取值组合有种。A.15B.8C.7D.144.一个四输入端或非门,使其输出为1的输入变量取值组合有种。A.15B.8C.7D.145.A101101=。A.AB.C.0D.146.下列四种类型的逻辑门中,可以用实现与、或、非三种基本运算。

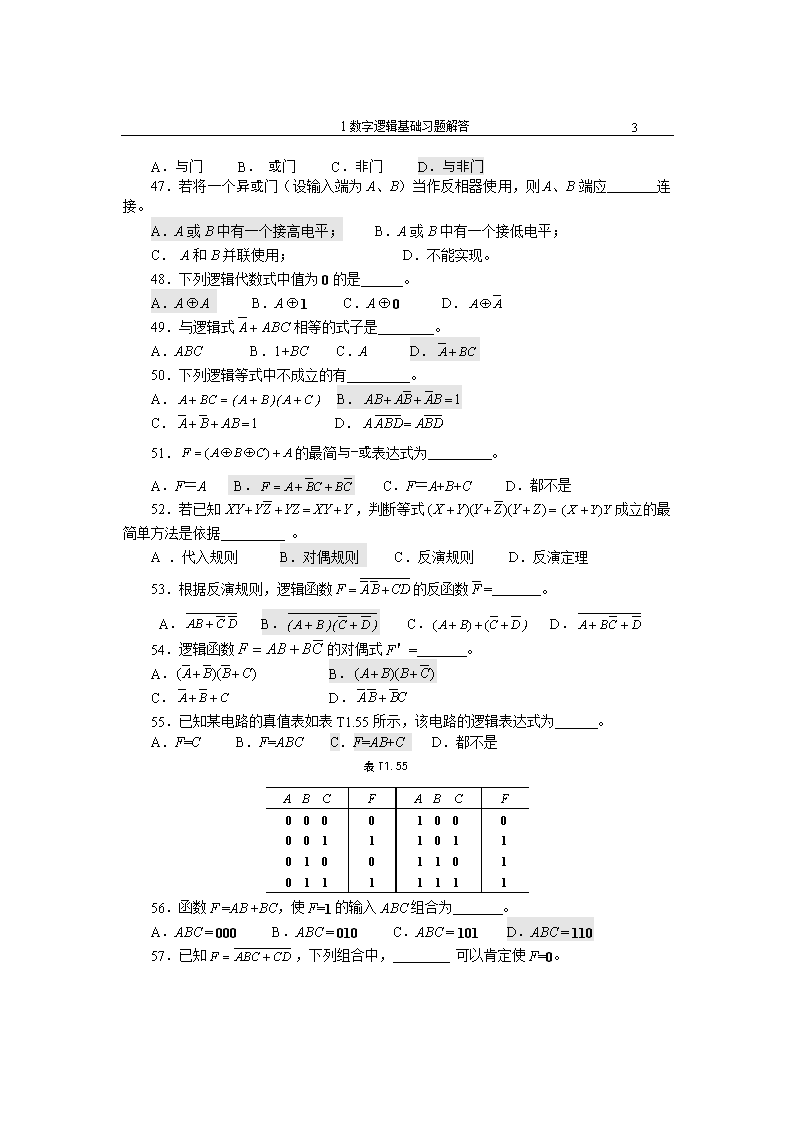

1数字逻辑基础习题解答140A.与门B.或门C.非门D.与非门47.若将一个异或门(设输入端为A、B)当作反相器使用,则A、B端应连接。A.A或B中有一个接高电平;B.A或B中有一个接低电平;C.A和B并联使用;D.不能实现。48.下列逻辑代数式中值为0的是。A.AÅAB.AÅ1C.AÅ0D.49.与逻辑式相等的式子是。A.ABCB.1+BCC.AD.50.下列逻辑等式中不成立的有。A.B.C.D.51.的最简与-或表达式为。A.F=AB.C.F=A+B+CD.都不是52.若已知,判断等式成立的最简单方法是依据。A.代入规则B.对偶规则C.反演规则D.反演定理53.根据反演规则,逻辑函数的反函数=。A.B.C.D.54.逻辑函数的对偶式F'=。A.B.C.D.55.已知某电路的真值表如表T1.55所示,该电路的逻辑表达式为。A.F=CB.F=ABCC.F=AB+CD.都不是表T1.55ABCFABCF0000010100110101100101110111011156.函数F=AB+BC,使F=1的输入ABC组合为。A.ABC=000B.ABC=010C.ABC=101D.ABC=11057.已知,下列组合中,可以肯定使F=0。

1数字逻辑基础习题解答140A.A=0,BC=1B.B=1,C=1C.C=1,D=0D.BC=1,D=158.在下列各组变量取值中,能使函数F(A,B,C,D)=∑m(0,1,2,4,6,13)的值为l是。A.1100B.1001C.0110D.111059.以下说法中,是正确的?A.一个逻辑函数全部最小项之和恒等于1B.一个逻辑函数全部最大项之和恒等于0C.一个逻辑函数全部最小项之积恒等于1D.一个逻辑函数全部最大项之积恒等于160.标准或-与式是由构成的逻辑表达式。A.与项相或B.最小项相或C.最大项相与D.或项相与61.逻辑函数F(A,B,C)=Σm(0,1,4,6)的最简与非-与非式为。A.B.C.D.62.若ABCDEFGH为最小项,则它有逻辑相邻项个数为。A.8B.82C.28D.1663.在四变量卡诺图中有个小方格是“1”。A.13B.12C.6D.564.VHDL是在年正式推出的。A.1983B.1985C.1987D.198965.VHDL的实体部分用来指定设计单元的。A.输入端口 B.输出端口C.引脚 D.以上均可66.一个实体可以拥有一个或多个。A.设计实体 B.结构体C.输入 D.输出67.在VHDL的端口声明语句中,用声明端口为输入方向。A.IN B.OUTC.INOUT D.BUFFER68.在VHDL的端口声明语句中,用声明端口为具有读功能的输出方向。A.IN B.OUTC.INOUT D.BUFFER69.在VHDL标识符命名规则中,以开头的标识符是正确的。A.字母B.数字C.字母或数字D.下划线70.在VHDL中,目标信号的赋值符号是。A.=:B.=C.:=D.<=

1数字逻辑基础习题解答140习题1.有人说“五彩缤纷的数字世界全是由‘0、1’及‘与、或、非’组成的。”你如何理解这句话的含义?答:任何复杂的数字电路都可由与、或、非门组成。数字电路处理的都是0、1构成的数字信号。2.用4位格雷码表示0、1、2、…、8、9十个数,其中规定用0000四位代码表示数0,试写出三种格雷码表示形式。解:G3G2G1G0G3G2G1G0G3G2G1G00000000000000001001001000011011011000010010010000110010110011110011110111111111110101101110111101100110001101000100000103.书中表1.2-4中列出了多种常见的BCD编码方案。试写出余3循环码的特点,它与余3码有何关系?解:余3循环码的主要特点是任何两个相邻码只有一位不同,它和余3码的关系是:设余3码为B3B2B1B0,余3循环码为G3G2G1G0,可以通过以下规则将余3码转换为余3循环码。(1)如果B0和B1相同,则G0为0,否则为1;(2)如果B1和B2相同,则G1为0,否则为1;(3)如果B2和B3相同,则G2为0,否则为1;(4)G3和B3相同。4.如果存在某组基本运算,使任意逻辑函数F(X1,X2,…,Xn)均可用它们表示,则称该组基本运算组成完备集。已知与、或、非三种运算组成完备集,试证明与、异或运算组成完备集。解:将异或门的其中一个输入端接高电平即转化为非门,根据可知,利用与门和非门可以构成或门,因此,与、异或运算可以实现与、或、非三种运算,从而组成完备集。5.布尔量A、B、C存在下列关系吗?

1数字逻辑基础习题解答140(1)已知A+B=A+C,问B=C吗?为什么?(2)已知AB=AC,问B=C吗?为什么?(3)已知A+B=A+C且AB=AC,问B=C吗?为什么?(4)最小项m115与m116可合并。解:(1)×,因为只要A=1,不管B、C为何值,A+B=A+C即成立,没有必要B=C。(2)×,不成立,因为只要A=0,不管B、C为何值,AB=AC即成立,没有必要B=C。(3)√,当A=0时,根据A+B=A+C可得B=C;当A=1时,根据AB=AC可得B=C。(4)×,115=1110011B116=1110100B逻辑不相邻。6.列出逻辑函数的真值表。解:ABCY000000100100011010011011110011107.写出如图P1.7所示逻辑电路的与-或表达式,列出真值表。图P1.7图P1.8解:ABF0000111011108.写出如图P1.8所示逻辑电路的与-或表达式,列出真值表。

1数字逻辑基础习题解答140解:表达式真值表ABCF000001010011100101110111000111009.试用与非门实现逻辑函数L=AB+BC。解:逻辑电路图10.根据图P1.10所示波形图,写出逻辑关系表达式Z=f(A,B,C),并将表达式简化成最简或非-或非表达式和最简与-或-非表达式。图P1.10解:根据波形图列出真值表:ABCZ00000011010001111000

1数字逻辑基础习题解答140101011011111利用卡诺图化简得到:或非-或非表达式与或非表达式11.用公式法证明:解:解法一:∴Y1=Y2解法二:12.证明不等式。解:令当D=0时,,列出函数真值表:ABCY1Y20000100110010010111110011101111100111111从真值表可知:Y1≠Y213.已知逻辑函数,求:最简与-或式、与非-与非式、最小项表达式。

1数字逻辑基础习题解答140解:最简与-或式:与非-与非式:最小项之和:14.已知F(A,B,C)=AB+BC,求其最大项之积表达式(标准或-与式)。解:方法一:先求最小项之和,再求最大项之积。方法二:直接求。15.某组合逻辑电路如图P1.15所示:(1)写出函数Y的逻辑表达式;(2)将函数Y化为最简与-或式;(3)用与非门画出其简化后的电路。图P1.15解:

1数字逻辑基础习题解答14016.与非门组成的电路如图P1.16所示:(1)写出函数Y的逻辑表达式;(2)将函数Y化为最简与-或式;(3)用与非门画出其简化后的电路。图P1.16解:,,,17.列出如图P1.17所示逻辑电路的真值表。

1数字逻辑基础习题解答140图P.17解:真值表ABCL1L2ABCL1L2000101000100101101010100111001011101110018.用公式法化简逻辑函数:(1)(2)(3)(4)解(1)(2)(3)(利用摩根定理)(包含律逆应用)(4)19.将以下逻辑函数化简为:(1)最简或-与式;(2)最简或非-或非式。解:

1数字逻辑基础习题解答140(1)求函数Y的对偶式Y"(2)化简Y"用公式化简法化简,得[配项ABD,结合律][](3)求Y"的对偶式(Y")",即函数Y[最简或-与式]再两次求反[最简或非-或非式]20.若两个逻辑变量X、Y同时满足X+Y=1和XY=0,则有。利用该公理证明:。证:令,∵且(利用公式)(利用公式)(利用公式)(利用公式)(利用公式)∴,原等式成立。21.试用卡诺图法将逻辑函数化为最简与-或式:(1)F(A,B,C)=∑m(0,1,2,4,5,7)(2)F(A,B,C,D)=∑m(4,5,6,7,8,9,10,11,12,13)(3)F(A,B,C,D)=∑m(0,2,4,5,6,7,12)+∑d(8,10)(4)F(A、B、C、D)=∑m(5、7、13、14)+∑d(3、9、10、11、15)解:(1)(2)

1数字逻辑基础习题解答140(3)(4)22.求下面函数表达式的最简与-或表达式和最简与-或-非表达式。F=∑m(0,6,9,10,12,15)+∑d(2,7,8,11,13,14)解:最简与-或表达式

1数字逻辑基础习题解答14023.求F(A,B,C,D)=∑m(0,1,4,7,9,10,13)+∑d(2,5,8,12,15)的最简与-或式及最简或-与式。解:(1)最简与-或式(2)最简或-与式方法一:根据最简与-或式变换得到:方法二:利用卡诺图对0方格画包围圈。24.用卡诺图化简逻辑函数,给定约束条件为:。解:

1数字逻辑基础习题解答14025.用卡诺图化简逻辑函数,给定约束条件为:AB+CD=0。解:26.用卡诺图化简逻辑函数:解:方法一:直接按照或-与表达式画卡诺图方法二:

1数字逻辑基础习题解答14027.用卡诺图化简逻辑函数:解:=∑m(1,2,3,6,7,9,11,12,13,14,15)·∑m(2,3,7,9,10,11,15)28.有两个函数F=AB+CD、G=ACD+BC,求M=F·G及N=F+G的最简与-或表达式。解:画出F和G的卡诺图如下:函数在进行与或运算时,只要将图中编号相同的方块,按下述的运算规则进行运算,即可求得它们的逻辑与、逻辑或等函数。其运算规则如表所示。.01×+01×0000001×101×1111×0××××1×根据表中运算规则,得到表达式:

1数字逻辑基础习题解答14029.有两个函数,F1(A,B,C,D)=∑m(0,2,7,8,10,13)+∑d(1,4,9),F2(A,B,C,D)=∏M(1,2,6,8,10,12,15)·∏D(4,9,13),其中m、M表示最小项和最大项,d、D表示无关项,试用卡诺图求:(1)的最简与-或表达式;(2)的最简或-与表达式。解:先将F2转化为最小项之和的形式:画出F1和F2的卡诺图:画出P1和P2的卡诺图:

1数字逻辑基础习题解答140自我检测题1.CMOS门电路采用推拉式输出的主要优点是提高速度,改善负载特性。2.CMOS与非门多余输入端的处理方法是接高电平,接电源,与其它信号引脚并在一起。3.CMOS或非门多余输入端的处理方法是接低电平,接地,与其它信号引脚并接在一起。4.CMOS门电路的灌电流负载发生在输出低电平情况下。负载电流越大,则门电路输出电压越高。5.CMOS门电路的静态功耗很低。随着输入信号频率的增加,功耗将会增加。6.OD门在使用时输出端应接上拉电阻和电源。7.三态门有3种输出状态:0态、1态和高阻态。8.当多个三态门的输出端连在一条总线上时,应注意任何时刻只能有一个门电路处于工作态。9.在CMOS门电路中,输出端能并联使用的电路有OD门和三态门;10.CMOS传输门可以用来传输数字信号或模拟信号。11.提高LSTTL门电路工作速度的两项主要措施是采用肖特基三极管和采用有源泄放电路。12.当CMOS反相器的电源电压VDD<VTN+(VTN、VTP分别为NMOS管和PMOS管的开启电压)时能正常工作吗?答:不能正常工作,因为,当反相器输入电压为1/2VDD时,将出现两只管子同时截止的现象,这是不允许的。13.CMOS反相器能作为放大器用吗?答:可以。在反相器的两端跨接了一个反馈电阻Rf就可构成高增益放大器。由于CMOS门电路的输入电流几乎等于零,所以Rf上没有压降,静态时反相器必然工作在vI=vO的状态,vI=vO=VT=VDD/2就是反相器的静态工作点。反相器的输入电压稍有变化,输出就发生很大变化。14.如果电源电压增加5%,或者内部和负载电容增加5%,你认为哪种情况会对CMOS电路的功耗产生较大影响?解:根据公式PD=(CL+CPD)VDD2f,电源的变化对功耗影响更大。15.当不同系列门电路互连时,要考虑哪几个电压和电流参数?这些参数应满足怎样的关系?解:应考虑以下参数:VOH(min)、VIH(min)、VOL(max)、VIL(max)、IOH(max)、IOL(max)、IIH(max),IIL(max),这些参数应满足以下条件:

1数字逻辑基础习题解答140VOH(min)≥VIH(min)VOL(max)≤VIL(max)≥nIIH(max)IOL(max)≥m16.已知图T2.16所示电路中各MOSFET管的=2V,若忽略电阻上的压降,则电路中的管子处于导通状态。A.B.C.D.图T2.1617.三极管作为开关时工作区域是。A.饱和区+放大区B.击穿区+截止区C.放大区+击穿区D.饱和区+截止区18.门电路参数由大到小排列正确的是。A.VOH(min)、VIH(min)、VIL(max)、VOL(max)B.VIH(min)、VOH(min)、VOL(max)、VIL(max)C.VOH(min)、VIH(min)、VOL(max)、VIL(max)D.VIH(min)、VOH(min)、VIL(max)、VOL(max)19.对CMOS门电路,以下说法是错误的。A.输入端悬空会造成逻辑出错B.输入端接510kΩ的大电阻到地相当于接高电平C.输入端接510Ω的小电阻到地相当于接低电平D.噪声容限与电源电压有关20.某集成电路芯片,查手册知其最大输出低电平VOL(max)=0.5V,最大输入低电平VIL(max)=0.8V,最小输出高电平VOH(min)=2.7V,最小输入高电平VIH(min)=2.0V,则其低电平噪声容限VNL=。A.0.4VB.0.6VC.0.3VC.1.2V21.某集成门电路,其低电平输入电流为1.0mA,高电平输入电流为10μA,最大灌电流为8mA,最大拉电流为400μA,则其扇出系数为N=。A.8B.10C.40D.2022.设图T2.22所示电路均为LSTTL门电路,能实现功能的电路是。

1数字逻辑基础习题解答140A.B.C.D.图T2.2223.设图T2.23所示电路均为CMOS门电路,实现功能的电路是。A.B.C.D.图T2.2324.如图T2.24所示LSTTL门电路,当=0时,F的状态为。A.B.C.D.图T2.24图T2.2525.OD门组成电路如图T2.25所示,其输出函数F为。A.B.C.D.习 题1.写出如图P2.1所示CMOS门电路的逻辑表达式。

1数字逻辑基础习题解答140图P2.1图P2.2解:(与非门)2.写出如图P2.2所示CMOS门电路的逻辑表达式。解:3.双互补对与反相器引出端如图P2.3所示,试将其分别连接成:(1)三个反相器;(2)3输入端与非门;(3)3输入端或非门;(4)实现逻辑函数;(5)一个非门控制两个传输门分时传送。图P2.3解:(1)3个反相器

1数字逻辑基础习题解答140(2)3输入与非门(3)3输入或非门(4)实现逻辑函数

1数字逻辑基础习题解答140连接图等效图当C=0时,Y=1;当C=1时,(5)一个非门控制两个传输门分时传送4.电路如图P2.4所示,G1为74HC系列CMOS门电路,其数据手册提供的参数为VOL(max)=0.33V,VOH(min)=3.84V,IOL(max)=4mA,IOH(max)=-4mA。三极管T导通时VBE=0.7V,饱和时VCES=0.3V,发光二极管正向导通时压降VD=2.0V。(1)当输入A、B取何值时,发光二极管D有可能发光?(2)为使T管饱和,T的β值应为多少?图P2.4

1数字逻辑基础习题解答140解:(1)要使发光二极管D发光,必须使T管饱和导通,要使T管饱和导通,必须使G1输出高电平,即A和B至少有一个为低电平。(2)为使三极管导通时进入饱和状态,三极管β的选择必须满足IB≥IBS,式中代入给定数据后,可求得β≥17。5.有一门电路内部电路如图P2.5所示,写出Y的真值表,画出相应的逻辑符号。解:真值表AENY00001高阻10111高阻逻辑符号6.分析如图P2.6所示电路的逻辑功能,画出其逻辑符号。图P2.5图P2.6解:A、B为电路输入变量,F为输出变量,只要列出真值表,就可判断其逻辑功能。ABY00011011高阻1高阻0

1数字逻辑基础习题解答1407.由三态门构成的总线传输电路如图P2.7所示,图中n个三态门的输出接到数据传输总线,D0、D1、…、Dn-1为数据输入端,、、…、为片选信号输入端。试问:(1)片选信号应满足怎样的时序关系,以便数据D0、D1、…、Dn-1通过总线进行正常传输?(2)如果片选信号出现两个或两个以上有效,可能发生什么情况?(3)如果所有的信号均无效,总线处在什么状态?图P2.7解:(1)片选信号任何时刻只能有一个为低电平;(2)总线冲突。(3)高阻态。8.分析如图P2.8(a)、(b)所示电路的逻辑功能,写出电路输出函数S的逻辑表达式。(a)(b)图P2.8解:(1)ABS000011101110

1数字逻辑基础习题解答140输出S是A和B的异或函数,即(2)ABS000011101110输出S是A和B的异或函数,即9.晶体管电路如图P2.9所示,试判断各晶体管处于什么状态?图P2.9解:(a)根据图中参数因为iB<iBS,故T1管处于放大状态。(b)因为iB>iBS,故T2管处于饱和状态。10.已知电路如图P2.10所示,写出F1、F2、F3和F与输入之间的逻辑表达式。

1数字逻辑基础习题解答140图P2.10解:,,,11.分析如图P2.11所示电路的逻辑功能,指出是什么门。图P2.11解:A、B加不同电平时,T4~T8的通断情况如表所示。ABT4T5T6T7T8F00offoffoffonoff101onoffoffoffon010offonoffoffon011onononoffoff1电路为OC输出的同或门.12.图P2.12(a)所示为LSTTL门电路,其电气特性曲线如图P2.12(b)所示。请按给定的已知条件写出电压表的读数(填表P2.12)。假设电压表的内阻≥100kΩ。

1数字逻辑基础习题解答140(a)(b)图P2.12表P2.12ABCK电压表读数/V001100110101断开断开闭合闭合解:ABCK电压表读数(V)001100110101断开断开闭合闭合04.31.10.213.图P3.13中G1、G2、G3为LSTTL门电路,G4、G5、G6为CMOS门电路。试指出各门的输出状态(高电平、低电平、高阻态?)。图P2.13

1数字逻辑基础习题解答140解:Y1高电平,Y2高阻态,Y3低电平,Y4高电平,Y5低电平,Y6低电平14.如图P2.14所示逻辑电路能否实现所规定的逻辑功能?如能的在括号内写“Y”,错的写“N”。图P2.14()L2=AB+CD()解:Y,N15.如图P2.15所示逻辑电路能否实现所规定的逻辑功能?如能的在括号内写“Y”,错的写“N”。图P2.15()()解:Y,N16.由门电路组成的电路如图P2.16所示。试写出其逻辑表达式。

1数字逻辑基础习题解答140图P2.16解:,,17.由门电路组成的电路如图P2.17所示。试写出其逻辑表达式。图P2.17解:18.一个发光二极管导通时的电压降约为2.0V,正常发光时需要5mA电流,当发光二极管采用如图2.2-21(a)那样连接到74LS00与非门上时,请确定电阻R的一个合适值。74LS00的相关参数可参见表2.2-3。解:注意:在大多数应用中,发光二极管串联电阻的准确值是不重要的,本例中可采用510Ω现成电阻。19.图P2.19中,LSTTL门电路的输出低电平VOL≤0.4V时,最大灌电流IOL(max)=8mA,输出高电平时的漏电流IOZ≤50μA;CMOS门的输入电流可以忽略不计。如果要求Z点高、低电平VH≥4V、VL≤0.4V,请计算上拉电阻RC的选择范围。图P2.19解:(1)当Z点输出高电平时,应满足下式:

1数字逻辑基础习题解答140VH=+5V-RCIOZ≥4VRC≤≤20kΩ(2)当Z点输出低电平时,应满足下式:VL=+5V-RCIOL(max)≤0.4VRC≥≥0.57kΩ∴0.57kΩ≤RC≤20kΩ20.在图P2.20中有两个线与的OC门G1、G2。它们的输出驱动3个LSTTL与非门G3、G4、G5。设OC门输出低电平时允许灌入的最大电流IOL(max)为14mA,输出高电平时输出管截止的漏电流IOZ为0.05mA;LSTTL与非门输入低电平电流IIL为0.22mA,每个输入端的高电平输入电流IIH为0.02mA。如果要求OC门高电平输出电压VOH≥3V,低电平输出电压VOL≤0.3V,试求外接电阻RC的取值范围。图P2.21解:(1)G1、G2均输出高电平时电阻RC上流过的电流IC=2IOZ+(2+2+3)IIH=(2×0.05+7×0.02)mA=0.24mARC上的压降会使输出高电平电压下降,根据题意应满足VOH=VCC-RC×IC≥3V因此RC应满足(2)G1或G2门输出低电平时考虑最不利的情况,只有一个OC门输出低电平,流入输出低电平OC门的电流IOL=IC+3×IIL=≤14mA所以352Ω≤RC≤8.33kΩ

1数字逻辑基础习题解答14021.根据表2.4-1,试计算下列情况下的低电平噪声容限和高电平噪声容限。(1)74HCT驱动74LS;(2)74ALS驱动74HCT。解:(1)VNL=VIL(max)(74LS)-VOL(max)(74HCT)=0.8-0.1=0.7VVNH=VOH(min)(74HCT)-VIH(min)(74LS)=4.4-2=2.4V(2)VNL=VIL(max)(74HCT)-VOL(max)(74ALS)=0.8-0.5=0.3VVNH=VOH(min)(74ALS)-VIH(min)(74HCT)=4.8-2=2.8V22.有人使用机器上一个光电传感器,传感器受触发时,输出高电平为5V,但把这个传感器输出端接到某一电路输入端时,再次测试其输出电平,发现是2V,电平被拉低了。当换了另外一个型号的光电传感器,同样传感器受触发时,输出高电平为5V,把这个传感器连接到同一电路输入端时,测试电压依然是5V。请分析可能的原因。答:最大的可能是前一种光传感器的带载能力不够,即光传感器不能提供电路输入端所需的电流,所以输出信号一接到电路输入端就会被拉低.建议:在光传感器的输出端和后级电路之间加一级驱动(射随器或三极管)。23.如图P2.24所示,集成电路IC1输出七段显示码a~g,高电平有效,由于IC1最大输出高电平电流很小,无法驱动共阴LED数码管(点亮每个笔划需5mA电流以上,数码管中的发光二极管导通压降为1.4V)。试从下表1提供的三种TTL非门中,选择合适器件设计共阴LED数码管的驱动电路,只需画出a和b的驱动电路,需算出限流电阻的数值。图P2.24表P2.24解:电路图为

1数字逻辑基础习题解答140(2)当输入变高时:R≤720Ω当输入变低时:R≥294Ω∴294Ω≤R≤720Ω自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号有关,与以前的输入信号无关。2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为竞争冒险。3.8线—3线优先编码器74LS148的优先编码顺序是、、、…、,输出为。输入输出均为低电平有效。当输入…为11010101时,输出为010。4.3线—8线译码器74HC138处于译码状态时,当输入A2A1A0=001时,输出=11111101。5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫数据分配器。6.根据需要选择一路信号送到公共数据线上的电路叫数据选择器。7.一位数值比较器,输入信号为两个要比较的一位二进制数,用A、B表示,输出信号为比较结果:Y(A>B)、Y(A=B)和Y(A<B),则Y(A>B)的逻辑表达式为。8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为全加器。9.多位加法器采用超前进位的目的是简化电路结构×。(√,×)10.组合逻辑电路中的冒险是由于引起的。A.电路未达到最简B.电路有多个输出C.电路中的时延D.逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?A.在输出级加正取样脉冲B.在输入级加正取样脉冲C.在输出级加负取样脉冲D.在输入级加负取样脉冲12.当二输入与非门输入为变化时,输出可能有竞争冒险。A.01→10B.00→10C.10→11D.11→0113.译码器74HC138的使能端取值为时,处于允许译码状态。A.011B.100C.101D.01014.数据分配器和有着相同的基本电路结构形式。A.加法器B.编码器C.数据选择器D.译码器15.在二进制译码器中,若输入有4位代码,则输出有个信号。

1数字逻辑基础习题解答140A.2B.4C.8D.1616.比较两位二进制数A=A1A0和B=B1B0,当A>B时输出F=1,则F表达式是。A.B.C.D.17.集成4位数值比较器74LS85级联输入IA<B、IA=B、IA>B分别接001,当输入二个相等的4位数据时,输出FA<B、FA=B、FA>B分别为。A.010B.001C.100D.01118.实现两个四位二进制数相乘的组合电路,应有个输出函数。A.8B.9C.10D.1119.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要个异或门。A.2B.3C.4D.520.在图T3.20中,能实现函数的电路为。(a)(b)(c)图T3.20A.电路(a)B.电路(b)C.电路(c)D.都不是习题1.分析图P3.1所示组合逻辑电路的功能,要求写出与-或逻辑表达式,列出其真值表,并说明电路的逻辑功能。

1数字逻辑基础习题解答140图P3.1解:CO=AB+BC+AC真值表ABCSCOABCSCO0000010010001101010101010110010110111111电路功能:一位全加器,A、B为两个加数,C为来自低位的进位,S是相加的和,CO是进位。2.已知逻辑电路如图P3.2所示,试分析其逻辑功能。

1数字逻辑基础习题解答140图P3.2解:(1)逻辑表达式,,,(2)真值表ABCFABCF00001001001110110101110101111110(3)功能从真值表看出,ABC=000或ABC=111时,F=0,而A、B、C取值不完全相同时,F=1。故这种电路称为“不一致”电路。3.试用与非门设计一组合逻辑电路,其输入为3位二进制数,当输入中有奇数个1时输出为1,否则输出为0。解:(1)真值表ABCFABCF00001001001110100101110001101111(2)(无法用卡诺图化简)(3)逻辑图

1数字逻辑基础习题解答1404.4位无符号二进制数A(A3A2A1A0),请设计一个组合逻辑电路实现:当0≤A<8或12≤A<15时,F输出1,否则,F输出0。解:(1)真值表:A3A2A1A0FA3A2A1A0F00000000000011110011001101010101111111111111111100001111001100110101010100001110(2)表达式(3)电路图(4)如果要求用与非门实现,则:逻辑图:

1数字逻辑基础习题解答1405.约翰和简妮夫妇有两个孩子乔和苏,全家外出吃饭一般要么去汉堡店,要么去炸鸡店。每次出去吃饭前,全家要表决以决定去哪家餐厅。表决的规则是如果约翰和简妮都同意,或多数同意吃炸鸡,则他们去炸鸡店,否则就去汉堡店。试设计一组合逻辑电路实现上述表决电路。解:(1)逻辑定义:A、B、C、D分别代表约翰、简妮、乔和苏。F=1表示去炸鸡店,F=0表示去汉堡店。(2)真值表ABCDFABCDF00000000000011110011001101010101000000011111111100001111001100110101010100011111(3)用卡诺图化简(4)逻辑图F=AB+ACD+BCD6.试设计一个全减器组合逻辑电路。全减器是可以计算三个数X、Y、BI的差,即D=X-Y-CI。当X<Y+BI时,借位输出BO置位。解:设被减数为X,减数为Y,从低位来的借位为BI

1数字逻辑基础习题解答140,则1位全减器的真值表如图(a)所示,其中D为全减差,BO为向高位发出的借位输出。(1)真值表XYBIDBOXYBIDBO0000010010001111010001011110000110111111由卡诺图得电路图7.设计组合逻辑电路,将4位无符号二进制数转换成格雷码。解:(1)列出4位二进制码→4位格雷码的转换真值表,如表所示。输入输出输入输出B3B2B1B0G3G2G1G0B3B2B1B0G3G2G1G00000000010001100000100011001110100100011101011110011001010111110

1数字逻辑基础习题解答1400100011011001010010101111101101101100101111010010111010011111000(2)根据真值表分别画出输出变量G3,G2,G1,G0的卡诺图,如图4.1.2-12所示。化简后,得,,,(3)由逻辑表达式得电路实现,如图所示。8.请用最少器件设计一个健身房照明灯的控制电路,该健身房有东门、南门、西门,在各个门旁装有一个开关,每个开关都能独立控制灯的亮暗,控制电路具有以下功能:(1)某一门开关接通,灯即亮,开关断,灯暗;(2)当某一门开关接通,灯亮,接着接通另一门开关,则灯暗;(3)当三个门开关都接通时,灯亮。解:设东门开关为A,南门开关为B,西门开关为C。开关闭合为1,开关断开为0。灯为Z,等暗为0,灯亮为1。根据题意列真值表如下:ABCZABCZ00001001001110100101110001101111(2)画出卡诺图如图所示。

1数字逻辑基础习题解答140(3)根据卡诺图,可得到该逻辑电路的函数表达式:(3)根据逻辑函数表达式,可画出逻辑电路图如图所示。9.设计一个能被2或3整除的逻辑电路,其中被除数A、B、C、D是8421BCD编码。规定能整除时,输出L为高电平,否则,输出L为低电平。要求用最少的与非门实现。(设0能被任何数整除)解:(1)真值表ABCDLABCDL00001100010001010011001011010×001111011×010011100×010101101×011011110×011101111×(2)用卡诺图化简(3)逻辑图10.如图P3.10所示为一工业用水容器示意图,图中虚线表示水位,A、B、C电极被水浸没时会有高电平信号输出,试用与非门构成的电路来实现下述控制作用:水面在A、B间,为正常状态,亮绿灯G;水面在B、C间或在A以上为异常状态,点亮黄灯Y;面在C以下为危险状态,点亮红灯R。要求写出设计过程。

1数字逻辑基础习题解答140图P3.10解:(1)真值表ABCGYRABCGYR000001100×××001010101×××010×××110×××011100111010(2)卡诺图化简(3)逻辑图11.试用卡诺图法判断逻辑函数式Y(A,B,C,D)=∑m(0,1,4,5,12,13,14,15)是否存在逻辑险象,若有,则采用增加冗余项的方法消除,并用与非门构成相应的电路。解:卡诺图如图(a)所示。最简逻辑函数式为:

1数字逻辑基础习题解答140此函数存在逻辑险象。只要如图所示增加冗余项即可,逻辑式变为:用与非门构成的相应电路如图(b)所示。(a)(b)12.已知,求Y的无竞争冒险的最简与-或式。解:卡诺图如图所示:上式中为冗余项,以消除竞争冒险。13.某一组合电路如图P3.13所示,输入变量(A,B,D)的取值不可能发生(0,1,0)的输入组合。分析它的竞争冒险现象,如存在,则用最简单的电路改动来消除之。

1数字逻辑基础习题解答140图P3.13解:解法1:从逻辑图得到以下表达式:根据表达式得到卡诺图:但由于从卡诺图可见,包围圈有两处相切,因此存在竞争冒险现象。可以通过相切点位置增加一个乘积项,得进一步分析,当ACD=000时,,由于输入变量(A,B,D)的取值不可能发生(0,1,0)的输入组合,因此,当ACD=000时,B必然为0,不会产生竞争冒险。因此,这一项不需要增加,只需要增加。电路图为:

1数字逻辑基础习题解答140解法二:如果逻辑表达式在某种取值下,出现、、、,就有可能出现竞争冒险。根据逻辑表达式,和不会出现。当A=C=D=0,出现,但由于输入变量(A,B,D)的取值不可能发生(0,1,0)的输入组合,因此,当ACD=000时,B必然为0,因此也不会产生竞争冒险。只有当A=B=1,D=0,出现,存在竞争冒险问题,加冗余项可消除竞争冒险。14.电路如图P3.14所示,图中①~⑤均为2线—4线译码器。(1)欲分别使译码器①~④处于工作状态,对应的C、D应输入何种状态(填表P3.12-1);(2)试分析当译码器①工作时,请对应A、B的状态写出的状态(填表P3.12-2);(3)说明图P3.14的逻辑功能。表P3.14-1表P3.14-2处于工作状态的译码器C、D应输入的状态ABCD①00②01③10④11

1数字逻辑基础习题解答140图P3.14解:处于工作状态的译码器C、D应输入的状态ABCD①00000111②01011011③10101101④11111110逻辑功能:由74LS139构成的4线—16线译码器15.图P3.15所示电路是由3线-8线译码器74HC138及门电路构成的地址译码电路。试列出此译码电路每个输出对应的地址,要求输入地址A7A6A5A4A3A2A1A0用十六进制表示。图P3.15解:由图可见,74HC138的功能扩展输入端必须满足E1=1、才能正常译码,因此E1=A3=1;,即A4=1,A5=1;,即A6=0,A7=0。所以,该地址译码器的译码地址范围为A7A6A5A4A3A2A1A0=00111A2A1A0

1数字逻辑基础习题解答140=00111000~00111111,用十六进制表示即为38H~3FH。输入、输出真值表如表1所示。表1地址译码器的真值表地址输入译码输出A7A6A5A4A3A2A1A038H0111111139H101111113AH110111113BH111011113CH111101113DH111110113EH111111013FH1111111016.写出图P3.16所示电路的逻辑函数,并化简为最简与-或表达式。图P3.16解:由图(a)写出逻辑函数并化简,得17.试用一片3线-8线译码器74HC138和最少的门电路设计一个奇偶校验器,要求当输入变量ABCD中有偶数个1时输出为1,否则为0。(ABCD为0000时视作偶数个1)。解:

1数字逻辑基础习题解答140连接图18.用一个8线-3线优先编码器74HC148和一个3线-8线译码器74HC138实现3位格雷码→3位二进制的转换。解:根据下表可得到连线图:G2G1G0B2B1B0000→000001→001011→010010→011110→100111→101101→110100→111

1数字逻辑基础习题解答14019.根据图P3.19所示4选1数据选择器,写出输出Z的最简与-或表达式。解:20.由4选1数据选择器和门电路构成的组合逻辑电路如图P3.20所示,试写出输出E的最简逻辑函数表达式。解:图P3.19图P3.2021.由4选1数据选择器构成的组合逻辑电路如图P3.21所示,请画出在图P3.21所示输入信号作用下,L的输出波形。图P3.21解:4选1数据选择器的逻辑表达式为:将A1=A,A0=B,D0=1,D1=C,,D3=C代入得根据表达式可画出波形图:

1数字逻辑基础习题解答14022.已知用8选1数据选择器74LS151构成的逻辑电路如图P3.22所示,请写出输出L的逻辑函数表达式,并将它化成最简与-或表达式。图P3.22解:(1)写出逻辑函数表达式:(2)用卡诺图化简23.用一个8选1数据选择器74LS151和非门实现:解:

1数字逻辑基础习题解答14024.图P3.24所示是用二个4选1数据选择器组成的逻辑电路,试写出输出Z与输入M、N、P、Q之间的逻辑函数式。图P3.24解;25.用二个4选1数据选择器实现函数L,允许使用反相器。解:电路图

1数字逻辑基础习题解答14026.一个组合逻辑电路有两个控制信号C1和C2,要求:(1)C2C1=00时,(2)C2C1=01时,(3)C2C1=10时,(4)C2C1=11时,试设计符合上述要求的逻辑电路(器件不限)解:方法一:真值表→卡诺图化简→逻辑图真值表C2C1ABFC2C1ABF00000100010001110010001011010000110101100100111000010111101001101111000111011111卡诺图化简逻辑图

1数字逻辑基础习题解答140方法二:利用数据选择器和少量门电路实现27.试用4选1数据选择器74LS153(1/2)和最少量的与非门实现逻辑函数。解:令A1=C,A0=D,,,D2=1,D3=0连线图:

1数字逻辑基础习题解答14028.P(P2P1P0)和Q(Q2Q1Q0)为两个三位无符号二进制数,试用一个74LS138和一个74LS151和尽可能少的门电路设计如下组合电路:当P=Q时输出F=1,否则F=0。解:29.试用8选1数据选择器74LS151实现逻辑函数L=AB+AC。解:30.用8选1数据选择器74LS151设计一个组合电路。该电路有3个输入A、B、C和一个工作模式控制变量M,当M=0时,电路实现“意见一致”功能(A,B,C状态一致时输出为1,否则输出为0),而M=1时,电路实现“多数表决”功能,即输出与A,B,C中多数的状态一致。解:

1数字逻辑基础习题解答140MABCFMABCF00000000000011110011001101010101100000011111111100001111001100110101010100010111电路图31.已知8选1数据选择器74LS151芯片的选择输入端A2的引脚折断,无法输入信号,但芯片内部功能完好。试问如何利用它来实现函数F(A,B,C)=∑m(1,2,4,7)。要求写出实现过程,画出逻辑图。解:对于LSTTL集成芯片,某个输入引脚折断后该脚悬空,相当于输入高电平1。74LS151的高位地址端A2折断后,输出不再响应D0,D1,D2,D3输入,8选1数据选择器只相当于一个4选1,此时地址输入为A1A0,数据输入为D4,D5,D6,D7,输出Y等于与函数F相比较不难看出,只要令AB为地址,则D4=C,D5=,D6=,D7=C。逻辑图如图所示。

1数字逻辑基础习题解答140图A4.2.2-5题4.2.2-11的电路实现32.用三片四位数值比较器74LS85实现两个12位二进制数比较。解:33.用一片4位数值比较器74HC85和适量的门电路实现两个5位数值的比较。解:高4位加到比较器数值输入端,最低位产生级联输入。W0V0I(A>B)I(A<B)I(A=B)00001010101010011001,,I(A=B)=W0⊙V0

1数字逻辑基础习题解答14034.用两个四位加法器74283和适量门电路设计三个4位二进制数相加电路。解:三个4位二进制数相加,其和应为6位。基本电路如图所示。两个加法器产生的进位通过一定的逻辑生成和的高两位。CO1CO2S5S40000010110011110,35.A、B为4位无符号二进制数(B≠0),用一个74LS283、非门和一个其它类型门电路实现:当A=(B-1)模16时,输出Y=1,否则为0。解:∵(B-1)模16即为B-1∴A=B-1时Y=1,否则Y=0,即B-1-A=B++1-1=B+为0时,Y=1。

1数字逻辑基础习题解答14036.A、B为四位二进制数,试用一片74283实现Y=4A+B。解:Y=4A+B=A3A2A1A000+B3B2B1B037.用一片74283和尽量少的门电路设计余3码到2421码的转换。解:余3码到2421码的转换的真值表为:A3A2A1A0B3B2B1B000110000010000010101001001100011011101001000101110011100101011011011111011001111从真值表中可以看到,当A3=0时,B=A-3,当A3=1时,B=A+3

1数字逻辑基础习题解答14038.设计一个一位8421BCD码乘以5的电路,要求输出也为8421BCD码。要求:(1)用4线/16线译码器及门电路实现;(2)只用四位全加器74LS283实现;(3)不用任何器件实现。解:根据题意列出真值表A3A2A1A0B7B6B5B4B3B2B1B0000000000000000100000101001000010000001100010101010000100000010100100101011000110000011100110101100001000000100101000101(1)从真值表可写出逻辑表达式:B7=0,B3=0,B1=0,B6=∑m(8,9),B5=∑m(4,5,6,7),B4=∑m(2,3,6,7),B0=B2=∑m(1,3,5,7,9)。

1数字逻辑基础习题解答140(2)用全加器实现逻辑图与36题同。(3)不用任何器件实现B7=0,B6=A3,B5=A2,B4=A1,B3=0,B2=A0,B1=0,B0=A039.利用两片并行进位加法器和必要的门电路设计一个8421BCD码加法器。8421BCD码的运算规则是:当两数之和小于等于9(1001)时,所得结果即为输出;当所得结果大于9时,则应加上6(0110)。解:连线图如图所示。加法器1完成两个加数得初始加法,加法器2对加法器1输出进行修正。

1数字逻辑基础习题解答140自我测验题1.图T4.1所示为由或非门构成的基本SR锁存器,输入S、R的约束条件是。A.SR=0B.SR=1C.S+R=0D.S+R=1图T4.1图T4.22.图T4.2所示为由与非门组成的基本SR锁存器,为使锁存器处于“置1”状态,其应为。A.=00B.=01C.=10D.=113.SR锁存器电路如图T4.3所示,已知X、Y波形,判断Q

1数字逻辑基础习题解答140的波形应为A、B、C、D中的B。假定锁存器的初始状态为0。(a)(b)图T4.34.有一T触发器,在T=1时,加上时钟脉冲,则触发器。A.保持原态B.置0C.置1D.翻转5.假设JK触发器的现态Qn=0,要求Qn+1=0,则应使。A.J=×,K=0B.J=0,K=×C.J=1,K=×D.J=K=16.电路如图T4.6所示。实现的电路是。A.B.C.D.图T4.67.电路如图T4.7所示。实现的电路是。A.B.C.D.图T4.78.电路如图T4.8所示。输出端Q所得波形的频率为CP信号二分频的电路为。

1数字逻辑基础习题解答140A.B.C.D.图T4.89.将D触发器改造成T触发器,如图T4.9所示电路中的虚线框内应是。图T4.9A.或非门B.与非门C.异或门D.同或门10.触发器异步输入端的作用是。A.清0B.置1C.接收时钟脉冲D.清0或置111.米里型时序逻辑电路的输出是。A.只与输入有关B.只与电路当前状态有关C.与输入和电路当前状态均有关D.与输入和电路当前状态均无关12.摩尔型时序逻辑电路的输出是。A.只与输入有关B.只与电路当前状态有关C.与输入和电路当前状态均有关D.与输入和电路当前状态均无关13.用n只触发器组成计数器,其最大计数模为。A.nB.2nC.n2D.2n14.一个5位的二进制加计数器,由00000状态开始,经过75个时钟脉冲后,此计数器的状态为:A.01011B.01100C.01010D.0011115.图T4.15所示为某计数器的时序图,由此可判定该计数器为。A.十进制计数器B.九进制计数器C.四进制计数器D.八进制计数器

1数字逻辑基础习题解答140图T4.1516.电路如图T4.16所示,假设电路中各触发器的当前状态Q2Q1Q0为100,请问在时钟作用下,触发器下一状态Q2Q1Q0为。图T4.16A.101B.100C.011D.00017.电路图T4.17所示。设电路中各触发器当前状态Q2Q1Q0为110,请问时钟CP作用下,触发器下一状态为。图T4.17A.101B.010C.110D.11118.电路如图T4.18所示,74LS191具有异步置数的逻辑功能的加减计数器,其功能表如表T4.18所示。已知电路的当前状态Q3Q2Q1Q0为1100,请问在时钟作用下,电路的下一状态Q3Q2Q1Q0为。

1数字逻辑基础习题解答140图T4.18A.1100B.1011C.1101D.0000表T4.1874LS191功能表CPD0D1D2D3Q0Q1Q2Q30×××d0d1d2d3d0d1d2d3100↑××××加法计数101↑××××减法计数11××××××保持19.下列功能的触发器中,不能构成移位寄存器。A.SR触发器B.JK触发器C.D触发器D.T和T'触发器。20.图T4.20所示电路的功能为。图T4.22A.并行寄存器B.移位寄存器C.计数器D.序列信号发生器21.4位移位寄存器,现态Q0Q1Q2Q3为1100,经左移1位后其次态为。A.0011或1011B.1000或1001C.1011或1110D.0011或111122.现欲将一个数据串延时4个CP的时间,则最简单的办法采用。A.4位并行寄存器B.4位移位寄存器C.4进制计数器D.4位加法器23.一个四位串行数据,输入四位移位寄存器,时钟脉冲频率为1kHz,经过可转换为4位并行数据输出。A.8msB.4msC.8µsD.4µs

1数字逻辑基础习题解答14024.由3级触发器构成的环形和扭环形计数器的计数模值依次为。A.8和8B.6和3C.6和8D.3和6习题1.由或非门构成的基本SR锁存器如图P4.1所示,已知输入端S、R的电压波形,试画出与之对应的Q和的波形。图P4.1解:2.由与非门构成的基本SR锁存器如图P4.2所示,已知输入端、的电压波形,试画出与之对应的Q和的波形。图P4.2解:

1数字逻辑基础习题解答1403.已知双门锁存器如图P4.3所示,试写出该锁存器的特性方程。图P4.3图P4.4解:先写出电路特性表。ABQnQn+1ABQnQn+100011001001110110100110101111111卡诺图4.写出图P4.4所示锁存器的特性方程解:CP=0时;RD=SD=0,Qn+1=QnCP=1时;,SD=S,5.钟控SR锁存器符号如图P4.5(a)所示,设初始状态为0,如果给定CP、S、R的波形如图P4.5(b)所示,试画出相应的输出Q波形。

1数字逻辑基础习题解答140(a)(b)图P4.5解:6.(1)分析图P4.6(a)所示由CMOS传输门构成的钟控D锁存器的工作原理。图P4.6(a)(2)分析图P4.6(b)所示主从D触发器的工作原理。图P4.6(b)(3)有如图P4.6(c)所示波形加在图P4.6(a)(b)所示的锁存器和触发器上,画出它们的输出波形。设初始状态为0。

1数字逻辑基础习题解答140图P4.6(c)解:(1)图所示是用两个非门和两个传输门构成的钟控D锁存器。当CP=1时,=0、C=1,TG1导通,TG2断开,数据D直接送到Q和端,输出会随D的改变而改变。但G1、G2没有形成正反馈,不具备锁定功能,此时称电路处于接收数据状态;CP变为低电平0时,=1,C=0,TG1断开,TG2导通,G1、G2形成正反馈,构成双稳态电路。由于G1、G2输入端存在的分布电容对逻辑电平有短暂的保持作用,因此,电路输出状态将锁定在CP信号由1变0前瞬间D信号所确定的状态。(2)由两个D锁存器构成的主从D触发器,采用上升沿触发方式,原理分析可参考4.2.1节有关内容。(3)D锁存器输出波形图D触发器输出波形图7.图P4.7(a)所示的为由D锁存器和门电路组成的系统,锁存器和门电路的开关参数如下:锁存器传输延时tpd(DQ)=15ns,tpd(CQ)=12ns,建立时间tSU=20ns;保持时间tH=0ns。与门的传输延迟时间tpdAND=16ns,或门的传输延迟时间tpdOR=18ns,异或门的传输延迟时间tpdXOR=22ns。(1)求系统的数据输入建立时间tSUsys;(2)系统的时钟及数据输入1的波形如图P4.7(b)所示。假设数据输入2和数据输入3均恒定为0,请画出Q的波形,并标明Q对于时钟及数据输入1的延迟。(a)(b)

1数字逻辑基础习题解答140图P4.7解:(1)系统的数据输入建立时间tSUsys=或门的传输延迟+异或门的传输延迟+锁存器的建立时间-与门的传输延迟=tpdOR+tpdXOR+tSU-tpdAND=18ns+22ns+20ns-16ns=44ns。(2)8.有一上升沿触发的JK触发器如图P4.8(a)所示,已知CP、J、K信号波形如图P4.8(b)所示,画出Q端的波形。(设触发器的初始态为0)(a)(b)图P4.8解:9.试画出如图P4.9所示时序电路在一系列CP信号作用下,Q0、Q1、Q2的输出电压波形。设触发器的初始状态为Q=0。

1数字逻辑基础习题解答140图P4.9解:先画Q0波形,再画Q1波形,最后画Q2波形。10.有一简单时序逻辑电路如图P4.10所示,试写出当C=0和C=1时,电路的状态方程Qn+1,并说出各自实现的功能。图P4.10解:当C=0时,J=X,K=X为T触发器当C=1时,J=X为D触发器11.用上升沿D触发器和门电路设计一个带使能EN的上升沿D触发器,要求当EN=0时,时钟脉冲加入后触发器也不转换;当EN=1时,当时钟加入后触发器正常工作,注:触发器只允许在上升沿转换。解:当EN=0,Qn+1=Qn;当EN=1,Qn+1=D,则,令即可。

1数字逻辑基础习题解答14012.由JK触发器和D触发器构成的电路如图P4.12(a)所示,各输入端波形如图P4.12(b),当各个触发器的初态为0时,试画出Q0和Q1端的波形,并说明此电路的功能。(a)(b)图P4.12解:根据电路波形,它是一个单发脉冲发生器,A可以为随机信号,每一个A信号的下降沿后;Q1端输出一个脉宽周期的脉冲。13.时序电路如图P4.13(a)所示。给定CP和A的波形如图P4.13(b)所示,画出Q1、Q2、Q3的波形,假设初始状态为0。(a)(b)图P4.13解:,,,

1数字逻辑基础习题解答14014.分析图P4.14示电路,要求:(1)写出JK触发器的状态方程;(2)用X、Y、Qn作变量,写出P和Qn+1的函数表达式;(3)列出真值表,说明电路完成何种逻辑功能。P4.14解:(1)(2)XYPXYP0000010001001011011001001110100111011111(3)串行加法器15.试分析如图P4.15同步时序逻辑电路,并写出分析过程。

1数字逻辑基础习题解答140图P4.15解:(1)写出驱动方程(2)写出状态方程,,(3)列出状态转换真值表000001100000001010101011010011110010011100111001(4)画出状态转换图(5)自启动校验,能够自启动(6)结论:具有自启动能力的同步五进制加法计数器。16.同步时序电路如图P4.16所示。(1)试分析图中虚线框电路,画出Q0、Q1、Q2波形,并说明虚线框内电路的逻辑功能。(2)若把电路中的Y输出和置零端连接在一起,试说明当X0X1X2为110时,整个电路的逻辑功能。

1数字逻辑基础习题解答140图P4.16解:(1)写出每级触发器的状态方程,,分析后,其状态转换图为:所以波形图为:电路是一个同步五进制可以自启动的加法计数器(2),当X1X2X3=110时,,当Q2Q1Q0出现011状态时,使计数器的状态清0,故此种情况下,整个电路功能为一个三进制加法计数器。

1数字逻辑基础习题解答14017.试用D触发器设计一个同步五进制加法计数器,要求写出设计过程。解:(1)状态转换图(2)状态真值表000001100000001010101×××010011110×××011100111×××(3)求状态方程(4)驱动方程,,(5)逻辑图(6)自启动检验。18.设计三相步进电机控制器:工作在三相单双六拍正转方式,即在CP

1数字逻辑基础习题解答140作用下控制三个线圈A、B、C按以下方式轮流通电。解:将A、B、C分别由三个触发器(Q2、Q1、Q0)的输出,则可画出状态转换图:根据状态转换图列出状态真值表(2)状态真值表000×××100110001101101100010011110010011001111×××(3)求状态方程(4)逻辑图(4)仿真结果

1数字逻辑基础习题解答14019.表P4.19为循环BCD码的编码表,试用JK触发器设计一个循环BCD码十进制同步加法计数器,并将其输出信号用与非门电路译码后控制交通灯:红灯R、绿灯G和黄灯Y。要求一个工作循环为:红灯亮30秒,黄灯亮10秒,绿灯亮50秒,黄灯亮10秒。要求写出设计过程,并画出CP、R、G和Y的波形图。写出设计过程并用QuartusII软件仿真。表P4.19循环BCD码十进制数DCBA十进制数DCBA00000511101000161010200117101130010810014011091000解:(1)列出状态真值表

1数字逻辑基础习题解答140000000010001001100100110001100100100×1×1×0×10101×1×1×1×1011011100111×1×1×1×0100000001001100010101011101110011100×0×0×0×01101×0×0×0×0111010101111×0×0×0×1(2)求状态方程

1数字逻辑基础习题解答140(3)驱动方程,,,,(4)电路图(5)自启动校验从状态表可知,无效状态通过几个CP脉冲以后能够进入有效循环,所以能够自启动。(6)译码电路设计真值表Q3Q2Q1Q0RGYQ3Q2Q1Q0RGY0000100100101000011001000001

1数字逻辑基础习题解答14000111000100×××00100010101×××01100100111×××11100101100×××10100101101×××10110101111×××表达式仿真波形20.图P4.20为一个米里型序列检测器的状态转换图。用D触发器实现该电路,并用QuartusII软件对该电路进行仿真,说明逻辑功能。(S0、S1、S2的编码分别为00、01、11)图P4.20解:(1)根据题意列出电路的状态表:

1数字逻辑基础习题解答140XZ0000000010100111101000101011101110010101×0×0×1100×0×1×(2)状态方程:,,(3)输出方程:(4)驱动方程:(5)电路图(6)仿真结果逻辑功能:该电路统计输入1的个数,当X输入3个1(不需要连续输入)时,输出Z为1。

1数字逻辑基础习题解答14021.设计一个串行编码转换器,把一个8421BCD码转换成余3BCD码。输入序列(X)和输出序列均由最低有效位开始串行输入和输出。要求将串行编码转换器设计成米里型状态机。解:如果8421BCD码的所有位同时可用,那么码转换器可以用一个4输入-4输出的组合逻辑电路来实现。但在这里BCD码是串行传输的数据,因此,必须用时序逻辑电路来实现。(1)列出状态转换图表1所示为8421BCD码和余3BCD码的对应表8421BCD码余3BCD码00000011000101000010010100110110010001110101100001101001011110101000101110011100状态设定设初始状态为S0,当8421BCD码第一位到达时,如果X=0,加上1,则Y=1(没有进位),进入状态S1(表示第一次加运算后没有进位);如果X=1,加上1,则Y=0(有进位),进入状态S2(表示有进位)。当8421BCD码第二位到达时,如果在状态S1,则若X=0,加上1,则Y=1,且没有进位,进入状态S3;若X=1,加上1,则Y=0,且有进位,进入状态S4。如果在状态S2,则若X=0,加上1,则Y=0,且有进位,进入状态S4;若X=1,加上1,则Y=1,且有进位,进入状态S4。当8421BCD码第三位到达时,如果状态为S3,则无任X=0还是为1,进入状态S5(无进位);如果状态为S4,当X=0时,进入状态S5,如果X=1,状态进入S6。当8421BCD码第四位到达时,不管状态为S5还是S6均回到S0。状态转换图如图所示。

1数字逻辑基础习题解答140状态表当前状态下一状态ZX=0X=1X=0X=1S0S1S210S1S3S410S2S4S401S3S5S501S4S5S610S5S0S001S6S0—1—状态编码为了减少逻辑门的数量,状态编码采用以下原则:(1)在给定输入的情况下,有相同次态的状态应给予只有一位不同的相邻赋值;(2)同一状态的次态应给予相邻赋值;(3)在给定输入的情况下,输出相同的状态给予相邻赋值。因此,状态编码如图所示。根据状态编码,列出状态转换真值表。YX=0X=1X=0X=100000110110

1数字逻辑基础习题解答1400011110111010101101101111110110010111100101011000000001010000×××1×100××××××××逻辑图

1数字逻辑基础习题解答14022.根据同步二进制计数器的构成规律,用上升沿触发T触发器和与非门设计8进制加减计数器,当M=0时为加法计数器,当M=1时为减法计数器,并要有进位和借位输出信号。画出电路。解:23.由四位二进制计数器74161及门电路组成的时序电路如图P4.23所示。要求:(1)分别列出X=0和X=1时的状态图;(2)指出该电路的功能。

1数字逻辑基础习题解答140图P4.23图P4.24解:(1)X=0时,电路为8进制加计数器,状态转换图为:(2)X=1时,电路为5进制加计数器,状态转换图为:24.由四位二进制计数器74161组成的时序电路如图P4.24所示。列出电路的状态表,假设CP信号频率为5kHz,求出输出端Y的频率。解:状态图如图所示:F信号为CP信号的五分频,因此其频率为1kHz。25.由四位二进制计数器74LS161和4位比较器74LS85构成的时序电路如图P4.25所示。试求:(1)该电路的状态转换图;(2)工作波形图;(3)简述电路的逻辑功能;(4)对电路做适当修改,实现N(N<16)进制计数。

1数字逻辑基础习题解答140P4.25解:(1)(2)(3)11进制加法计数器(4)将N从74LS85的B3B2B1B0输入即可。26.如图P4.26所示为由计数器和数据选择器构成的序列信号发生器,74161为四位二进制计数器,74LS151为8选1数据选择器。请问:(1)74161接成了几进制的计数器?(2)画出输出CP、Q0、Q1、Q2、L的波形(CP波形不少于10个周期)。

1数字逻辑基础习题解答140图P4.26解:(1)74161接成6进制计数器(2)波形如下:27.试分析如图P4.27所示电路的逻辑功能。图中74LS160为十进制同步加法计数器,其功能如表P4.27所示。图P4.27表P4.2774LS160功能表CPEPET工作状态×0×××置零↑10××预置数×1101保持×11×0保持(但CO=0)↑1111计数解:28进制加法计数器。(8421BCD码输出)28.用74161构成十一进制计数器。要求分别用“清零法”和“置数法”实现。解:(1)清零法

1数字逻辑基础习题解答140(2)置数法29.试用图P4.29(a)所示的电路和最少的门电路实现图P4.29(b)的功能,要求发光二极管亮三秒暗四秒,……,周期性地重复。(a)(b)图P4.29解:

1数字逻辑基础习题解答14030.用十六进制同步加法计数器74161设计能自启动的2421BCD码十进制加法计数器,可用必要的门电路。解:2421BCD码的状态转换图计至0100时置1011:,D3D2D1D0=1011,连线图为:31.设计一个可控计数器,X=0时实现8421BCD码计数器,X=1时实现2421BCD码计数器。8421BCD码2421BCD码00000000000100010010001000110011010001000101101101101100011111011000111010011111解:X=0时,计至9时置0000:,D3D2D1D0=0000

1数字逻辑基础习题解答140X=1时,计至4时置1011:,D3D2D1D0=1011,D2=0,D3=D1=D0=X32.如图P4.32所示为用两片74161构成的100进制计数器,两片74161采用同一时钟信号,每片74161均接成10进制计数器,然后级联。试用QuartusII软件对电路仿真,从仿真结果判断能否实现100进制计数,并分析原因。如不能实现100进制计数,请对电路做适当改进,并用QuartusII对电路重新仿真。图P4.32解:无法实现100进制计数,因为,当计数到10010000(90)时,再来一个CP脉冲就进入00000001(01)。其仿真结果为:改进后电路

1数字逻辑基础习题解答140对改进后电路的仿真结果:33.用两片集成计数器74161构成75进制计数器,画出连线图。解:34.用两片74161和门电路实现同步双模计数器。当M=0时24进制,M=1时60进制,要求电路不能过渡状态。解:M=0时:M=1时:

1数字逻辑基础习题解答14035.中规模集成计数器74LS193引脚图和逻辑符号、功能表分别如图P4.35和如表P4.35所示,其中和分别为进位和借位输出。(1)请画出进行加法计数实验时的实际连接电路。(2)试通过外部的适当连线,将74LS193连接成8421BCD码的十进制减法计数器。图P4.35表P4.35输入输出RDCPUCPDD3D2D1D0Q3Q2Q1Q01×××××××000000××d3d2d1d0d3d2d1d001↑1××××4位二进制加计数011↑××××4位二进制减计数解:(1)进行加法计数实验时的电路连接如图,CPD接1,CPU接计数脉冲,RD=0,接1,输出为Q3、Q2、Q1、Q0。(2)要求按8421编码十进制减法计数时,电路图如上右图所示,状态转换图为由功能表可知,74LS193是异步置数,因此当出现0000后,先出现1111,才能把计数器置成1001,随后开始减法计数,电路如图所示。

1数字逻辑基础习题解答14036.电路如图P4.36所示,设各触发器的初始状态为0。请画出在输入信号作用下,对应的输出Q0、Q1的波形,并描述电路实现的功能。图P4.36解:(1)波形图:(2)功能:右移寄存器37.一逻辑电路如图P4.37所示,试画出时序电路部分的状态图,并画出在CP作用下2—4译码器74LS139输出、、、的波形,设Q1、Q0的初态为0。2线—4线译码器的逻辑功能为:当时,电路处于工作状态,,,,。图P4.37解:(1)状态转换图(2)波形图

1数字逻辑基础习题解答14038.图P4.38所示右移寄存器中,已存入110101数码,JK触发器的初始状态为0。在CP脉冲作用下,试画出J、Q和Z端的波形。图P4.38解:39.分析如图P4.39所示电路,画出状态转换图和时序图,并说明CP和Q2是几分频。

1数字逻辑基础习题解答140图P4.39解:从图所示电路图可知,S1S0=01,根据表4.8-3所示的74LS194功能表,电路处于右移功能。右移数据输入端的逻辑表达式为:。图中异步清零端加了一负脉冲,使寄存器的初始状态Q0Q1Q2Q3=0000。根据右移寄存器的逻辑功能,可画出如图4.8-7所示的状态图。根据状态图,可画出如图所示的时序图。从上述时序图可知,CP与Q2之间的关系为七分频。40.画出如图P4.40所示由移位寄存器时序电路状态转换图和对应的输出Y。图P4.40解:状态转换图

1数字逻辑基础习题解答14041.采用如图P4.41所示的二片74LS194双向移位寄存器、一个1位全加器和一个D型触发器设计两个4位二进制数A=A3A2A1A0、B=B3B2B1B0的加法电路。要求画出电路,说明所设计电路的工作过程以及最后输出结果在何处。图P4.41解:工作过程:先将CLR置成低电平,将D触发清零,并使74LS194处于并行置数功能,在CP脉冲上升沿的作用下,将两个4位二进制数置入双向移位寄存器74LS194;将CLR恢复成高电平,使74LS194处于左移功能,在4个CP脉冲的作用下,完成加法运算,结果存在79LS194(0)中,4位加法器的进位输出存在D触发器中。CP和CLR的时序如下:

1数字逻辑基础习题解答140自我检测题1.在存储器结构中,什么是“字”?什么是“字长”,如何表示存储器的容量?解:采用同一个地址存放的一组二进制数,称为字。字的位数称为字长。习惯上用总的位数来表示存储器的容量,一个具有n字、每字m位的存储器,其容量一般可表示为n×m位。2.试述RAM和ROM的区别。解:RAM称为随机存储器,在工作中既允许随时从指定单元内读出信息,也可以随时将信息写入指定单元,最大的优点是读写方便。但是掉电后数据丢失。ROM在正常工作状态下只能从中读取数据,不能快速、随时地修改或重新写入数据,内部信息通常在制造过程或使用前写入,3.试述SRAM和DRAM的区别。解:SRAM通常采用锁存器构成存储单元,利用锁存器的双稳态结构,数据一旦被写入就能够稳定地保持下去。动态存储器则是以电容为存储单元,利用对电容器的充放电来存储信息,例如电容器含有电荷表示状态1,无电荷表示状态0。根据DRAM的机理,电容内部的电荷需要维持在一定的水平才能保证内部信息的正确性。因此,DRAM在使用时需要定时地进行信息刷新,不允许由于电容漏电导致数据信息逐渐减弱或消失。4.与SRAM相比,闪烁存储器有何主要优点?解:容量大,掉电后数据不会丢失。5.用ROM实现两个4位二进制数相乘,试问:该ROM需要有多少根地址线?多少根数据线?其存储容量为多少?解:8根地址线,8根数据线。其容量为256×8。6.简答以下问题:(1)CPLD和FPGA有什么不同?FPGA可以达到比CPLD更高的集成度,同时也具有更复杂的布线结构和逻辑实现。FPGA更适合于触发器丰富的结构,而CPLD更适合于触发器有限而积项丰富的结构。在编程上FPGA比CPLD具有更大的灵活性;CPLD功耗要比FPGA大;且集成度越高越明显;CPLD比FPGA有较高的速度和较大的时间可预测性,产品可以给出引脚到引脚的最大延迟时间。CPLD的编程工艺采用E2CPLD的编程工艺,无需外部存储器芯片,使用简单,保密性好。而基于SRAM编程的FPGA,其编程信息需存放在外部存储器上,需外部存储器芯片,且使用方法复杂,保密性差。(2)写出三家CPLD/FPGA生产商名字。Altera,lattice,xilinx,actel7.真值表如表T5.7所示,如从存储器的角度去理解,AB应看为地址,F0F1F2F3应看为数据。表T5.7ABF0F1F2F3000101

1数字逻辑基础习题解答1400110101001111111108.一个ROM共有10根地址线,8根位线(数据输出线),则其存储容量为。A.10×8B.102×8C.10×82D.210×89.为了构成4096×8的RAM,需要片1024×2的RAM。A.8片B.16片C.2片D.4片10.哪种器件中存储的信息在掉电以后即丢失?A.SRAMB.UVEPROMC.E2PROMD.PAL11.关于半导体存储器的描述,下列哪种说法是错误的。A.RAM读写方便,但一旦掉电,所存储的内容就会全部丢失B.ROM掉电以后数据不会丢失C.RAM可分为静态RAM和动态RAMD.动态RAM不必定时刷新12.有一存储系统,容量为256K×32。设存储器的起始地址全为0,则最高地址的十六进制地址码为3FFFFH。13.PAL是一种的可编程逻辑器件。A.与阵列可编程、或阵列固定的B.与阵列固定、或阵列可编程的C.与、或阵列固定的D.与、或阵列都可编程的习题1.现有如图P5.1所示的4×4位RAM若干片,现要把它们扩展成8×8位RAM。(1)试问需要几片4×4位RAM?(2)画出扩展后电路图(可用少量门电路)。图P5.1解:(1)用4×4位RAM扩展成8×8位RAM时,需进行字数和位数扩展,故需要4片4×4的RAM(2)扩展后电路如图:

1数字逻辑基础习题解答1402.在微机中,CPU要对存储器进行读写操作,首先要由地址总线给出地址信息,然后发出相应读或写的控制信号,最后才能在数据总线上进行信息交流。现有256×4位的RAM二片,组成一个页面,现需4个页面的存储容量,画出用256×4位组成1K×8位的RAM框图,并指出各个页面的地址分配。解:电路连接图如图所示。从左到右四个页面的地址为:000H~0FFH,100H~1FFH,200H~2FFH,300H~3FFH。3.试用4×2位容量的ROM实现半加器的逻辑功能,并直接在图P5.3中画出用ROM点阵图实现的半加法器电路。

1数字逻辑基础习题解答140图P5.3解:由于半加器的输出所以ROM点阵图如图所示。4.用EPROM实现二进制码与格雷码的相互转换电路,待转换的代码由I3I2I1I0输入,转换后的代码由O3O2O1O0输出。X为转换方向控制位,当X=0时,实现二进制码到格雷码的转换;当X=1时,实现格雷码到二进制码的转换。试求:(1)列出EPROM的地址与内容对应关系真值表;(2)确定输入变量和输出变量与ROM地址线和数据线对应关系。解:真值表为:XI3I2I1I0O3O2O1O0000000000000010001000100011000110010001000110001010111

1数字逻辑基础习题解答140001100101001110100010001100010011101010101111010111110011001010011011011011101001011111000100000000100010001100100011100110010101000111101010110101100100101110101110001111110011110110101100110111101111001000111011001111101011111111010输入变量和输出变量与ROM地址线和数据线对应关系如图所示:5.试分析如图P5.5所示PLA构成电路。写出F1、F2的逻辑表达式。

1数字逻辑基础习题解答140图P5.5解:6.试分析如图P5.6所示电路。(1)列出时序PLA的状态表和状态图(2)简述该时序PLA的逻辑功能。图P5.6

1数字逻辑基础习题解答140解:(1)根据电路图写出各触发器驱动方程,,,(2)写出各触发器状态方程(3)列出状态表Q2nQ1nQ0nCPQ2n+1Q1n+1Q0n+1000↓001001↓010010↓011011↓100100↓101101↓110110↓000111↓000(4)状态转换图(5)功能:同步七进制加法计数器。7.试分析如图P5.7所示由PLA实现的时序电路,列出状态转换表,简述该时序电路的逻辑功能。

1数字逻辑基础习题解答140图P5.7解(1)根据电路图写出各触发器状态方程:(2)根据特性方程列出状态真值表,如表所示。XQ2nQ1nQ0nQ2n+1Q1n+1Q0n+1XQ2nQ1nQ0nQ2n+1Q1n+1Q0n+10000001100000100010101001010001001110100110011100101110001001011100000010100011010000110111111001001110011111100(3)状态转换图由状态真值表可得电路在X=0与X=1时的状态转换图,如图所示。

1数字逻辑基础习题解答140(4)逻辑功能当X=0时,该时序电路为6进制加法计数器;当X=1时,该时序电路为5进制加法计数器。8.观察如图P5.8的可编程I/O模块,要求把此I/O模块配置成输入管脚,请标出数据输入通道,给出具体的5个配置比特,并给出T的值。图P5.8解:要将I/O引脚作为输入引脚,要将输出三态缓冲器输出置成高阻态,弱上拉禁止。因此可将三态控制T置1,三态反相置0,弱上拉置0,其余编程位无关。自我检测题1.集成单稳触发器,分为可重触发及不可重触发两类,其中可重触发指的是在暂稳态期间,能够接收新的触发信号,重新开始暂稳态过程。

1数字逻辑基础习题解答1402.如图T6.2所示是用CMOS或非门组成的单稳态触发器电路,vI为输入触发脉冲。指出稳态时a、b、d、e各点的电平高低;为加大输出脉冲宽度所采取的下列措施哪些是对的,哪些是错的。如果是对的,在()内打√,如果是错的,在()内打×。(1)加大Rd();(2)减小R();(3)加大C();(4)提高VDD();(5)增加输入触发脉冲的宽度()。图P6.2解:(1)×(2)×(3)√(4)×(5)×3.四个电路输入vI、输出vO的波形如图T6.3所示,试写出分别实现下列功能的最简电路类型(不必画出电路)。(a)二进制计数器;(b)施密特触发器;(c)单稳态触发器;(d)六进制计数器。图T6.34.单稳态触发器的主要用途是。A.整形、延时、鉴幅B.延时、定时、存储C.延时、定时、整形D.整形、鉴幅、定时

1数字逻辑基础习题解答1405.为了将正弦信号转换成与之频率相同的脉冲信号,可采用。A.多谐振荡器B.移位寄存器C.单稳态触发器D.施密特触发器6.将三角波变换为矩形波,需选用。A.单稳态触发器B.施密特触发器C.多谐振荡器D.双稳态触发器7.滞后性是的基本特性。A.多谐振荡器B.施密特触发器C.T触发器D.单稳态触发器8.自动产生矩形波脉冲信号为。A.施密特触发器B.单稳态触发器C.T触发器D.多谐振荡器9.由CMOS门电路构成的单稳态电路的暂稳态时间tw为。A.0.7RCB.RCC.1.1RCD.2RC10.已知某电路的输入输出波形如图T6.10所示,则该电路可能为。A.多谐振荡器B.双稳态触发器C.单稳态触发器D.施密特触发器图T6.1011.由555定时器构成的单稳态触发器,其输出脉冲宽度取决于。A.电源电压B.触发信号幅度C.触发信号宽度D.外接R、C的数值12.由555定时器构成的电路如图T6.12所示,该电路的名称是。A.单稳态触发器B.施密特触发器C.多谐振荡器D.SR触发器图T6.12习题1.电路如图P6.1所示,G1、G2均为CMOS系列。(1)说出电路名称;

1数字逻辑基础习题解答140(2)画出其传输特性;(3)列出主要参数计算公式。图P6.1解:(1)由门电路构成的施密特触发器。(2)传输特性(3)回差电压=2.图P6.2所示的电路是用施密特触发器构成的多谐振荡器,施密特触发器的阈值电压分别为VT+和VT—,试画出电容器C两端电压vC和输出电压vO的波形。如要使输出波形的占空比可调,试问电路要如何修改?图P6.2解:

1数字逻辑基础习题解答140占空比可调电路3.由CC40106构成的电路如图P6.3(a)所示,图P6.3(b)为CC40106的电压传输特性曲线,图P6.3(c)中的输入vI高电平脉宽和低电平脉宽均大于时间常数RC。要求画出vI作用下的vA、vO1和vO2波形。图P6.3解:波形图如下:

1数字逻辑基础习题解答1404.如图P6.4所示电路为由CMOS或非门构成的单稳态触发器。(1)画出加入触发脉冲vI后,vO1及vO2的工作波形;(2)写出输出脉宽tW的表达式。图P6.4解:工作波形为;TW=0.7RC5.用集成定时器555所构成的施密特触发器电路及输入波形vI如图P6.5所示,试画出对应的输出波形vO。

1数字逻辑基础习题解答140图P6.5解:6.由集成定时器555的电路如图P6.6所示,请回答下列问题:(1)构成电路的名称;(2)已知输入信号波形vI,画出电路中vO的波形(标明vO波形的脉冲宽度);图P6.6解:(1)555组成的单稳态触发器。(2)vI、vO波形如图所示。输出脉冲宽度由下式求得:TW=RCln3=100×103×3.3×10-6×1.1=363(ms)

1数字逻辑基础习题解答1407.图P6.7(a)所示为由555定时器构成的心率失常报警电路。经放大后的心电信号vI如图P6.7(b)所示,vI的峰值Vm=4V。(1)分别说出555定时器Ⅰ和555定时器Ⅱ所构成单元电路的名称;(2)对应vI分别画出A、B、D三点波形;(3)说明心率失常报警的工作原理。(a)(b)图P6.7解:(1)电路Ⅰ为施密特触发器,电路Ⅱ为可重触发单稳态触发器;(2)8.由集成定时器7555构成的电路如图P6.8所示,请回答下列问题。

1数字逻辑基础习题解答140(1)构成电路的名称;(2)画出电路中vC、vO的波形(标明各波形电压幅度,vO波形周期)。图P6.8解:(1)构成多谐振荡器;(2)参数计算:T=T1+T2=(R1+2R2)Cln2=(100×103+2×6.2×103)×10×10-6×0.7=78.7(ms)9.由555定时器构成的多谐振荡器如图P6.9所示,现要产生1kHz的方波(占空比不作要求),确定元器件参数,写出调试步骤和所需测试仪器。图P6.9解:取C=0.1μF,则取R2=5.1kΩ,则R1=4.1kΩ,可用一只3.3kΩ的固定电阻和一只2kΩ的精密电位器组成。原理图如图所示。

1数字逻辑基础习题解答140调试步骤:按原理图连好线,用示波器观察输出波形,调节精密电位器,使输出方波频率为1kHz。10.如图P6.10所示是一个由555定时器构成的防盗报警电路,a、b两端被一细铜丝接通,此铜丝置于盗窃者必经之路,当盗窃者闯入室内将铜丝碰断后,扬声器即发出报警声。(1)试问555接成何种电路?(2)说明本报警电路的工作原理。图P6.10解:(1)多谐振荡器(2)当细铜丝不断时,555定时器的置成低电平,使Q输出始终为低电平,喇叭不响。当细铜丝拉断时,555定时器的置成高电平,Q输出方波信号,喇叭发出报警声。11.4位二进制加法计数器74161和集成单稳态触发器74LS121组成如图P6.11(a)所示电路。(1)分析74161组成电路,画出状态图;(2)估算74LS121组成电路的输出脉宽TW值;(3)设CP为方波(周期T≥1ms),在图P6.11(b)中画出图P6.11(a)中vI、vO两点的工作波形。

1数字逻辑基础习题解答140(a)(b)图P6.11解:(1)计数器的状态转换图为:为三进制计数器。(2)TW=0.7RextCext=0.7×50×103×0.02×10-6=0.7ms(3)12.由555定时器和模数M=24同步计数器及若干I逻辑门构成的电路如图P6.12所示。(1)说明555构成的多谐振荡器,在控制信号A、B、C取何值时起振工作?(2)驱动喇叭啸叫的Z信号是怎样的波形?喇叭何时啸叫?(3)若多谐振荡器的多谐振荡器频率为640Hz,求电容C的取值。

1数字逻辑基础习题解答140图P6.12解:(1)T管截止时才能起振。因此AB=11或C=1时即可起振。(2)(3)T=0.7C(R1+2R2)自我检测题1.就实质而言,D/A转换器类似于译码器,A/D转换器类似于编码器。2.电压比较器相当于1位A/D转换器。3.A/D转换的过程可分为采样、保持、量化、编码4个步骤。4.就逐次逼近型和双积分型两种A/D转换器而言,双积分型的抗干扰能力强,逐次逼近型的转换速度快。5.A/D转换器两个最重要的指标是分辨率和转换速度。6.8位D/A转换器当输入数字量只有最低位为1时,输出电压为0.02V,若输入数字量只有最高位为1时,则输出电压为V。A.0.039B.2.56C.1.27D.都不是7.D/A转换器的主要参数有、转换精度和转换速度。A.分辨率B.输入电阻C.输出电阻D.参考电压8.图T7.8所示R-2R网络型D/A转换器的转换公式为。

1数字逻辑基础习题解答140图T7.8A.B.C.D.9.D/A转换器可能存在哪几种转换误差?试分析误差的特点及其产生误差的原因。解:D/A转换器的转换误差是一个综合性的静态性能指标,通常以偏移误差、增益误差、非线性误差等内容来描述转换误差。偏移误差是指D/A转换器输出模拟量的实际起始数值与理想起始数值之差。增益误差是指实际转换特性曲线的斜率与理想特性曲线的斜率的偏差。D/A转换器实际的包络线与两端点间的直线比较仍可能存在误差,这种误差称为非线性误差。10.比较权电阻型、R-2R网络型、权电流型等D/A转换器的特点,结合制造工艺、转换的精度和转换的速度等方面比较。解:权电阻型D/A转换器的精度取决于权电阻精度和外接参考电源精度。由于其阻值范围太宽,很难保证每个电阻均有很高精度,因此在集成D/A转换器中很少采用。R-2R网络型D/A转换器电阻网络中只有R和2R两种阻值的电阻,且比值为2。虽然集成电路技术制造的电阻值精度不高,但可以较精确地控制不同电阻之间的比值,从而使R-2R网络型D/A转换器获得较高精度。权电流型D/A转换器可以消除模拟开关导通电阻产生的影响。同时可获得较高的转换速度。11.Σ-Δ模/数(A/D)中包括哪些主要部分?它们各起什么作用?解:Σ-Δ模/数转换器由1个差分放大器、一个积分器、1个比较器、1个1bit的DAC和数字滤波器组成。差分放大器:将输入信号vI减去来自1位DAC的反馈信号得到误差信号,ve=vI-vf。积分器:积分器对误差信号ve进行积分。电压比较器:当积分器的输出电压vg>0V时,输出vg'为高电平(逻辑1);当vg≤0V时,vg'为低电平(逻辑0)。实际上,该电压比较器可以看成是1位的ADC。

1数字逻辑基础习题解答1401位的DAC:由一模拟选择开关构成。当输入为逻辑1时,把输出端vf接+VREF;当输入为逻辑0时,把输出端vf接地。在采样信号CP的作用下,D触发器的Q端送出一串行的数字序列c。此串行的数字序列经数字抽取滤波器滤波,从而获得并行n位数字量输出。12.从精度、工作速度和电路复杂性比较逐次逼近、并行比较、Σ-Δ型A/D转换器的特点。逐次逼近型A/D转换器的优点是电路结构简单,构思巧妙,转换速度较快(只需要n+2个CP周期,n是位数),所以在集成A/D芯片中用得最多。由于位数越多,转换时间越长,因此,分辨率在14位至16位,速率高于几Msps的逐次逼近ADC非常少见。并行比较型A/D转换器虽然具有转换速度极高的优点,但n位的A/D转换器需要提供2n-1个比较器。Σ-Δ转换器中的模拟部分非常简单(类似于一个1bitADC),而数字部分要复杂得多,按照功能可划分为数字滤波和抽取单元。由于更接近于一个数字器件,Σ-ΔADC的制造成本非常低廉。习题1.n位权电阻型D/A转换器如图P7.1所示。(1)试推导输出电压vO与输入数字量的关系式;(2)如n=8,VREF=-10V时,如输入数码为20H,试求输出电压值。图P7.1解:(1)(2)

1数字逻辑基础习题解答1402.10位R-2R网络型D/A转换器如图P7.2所示。(1)求输出电压的取值范围;(2)若要求输入数字量为200H时输出电压vO=5V,试问VREF应取何值?图P7.2解:(1)输出电压范围(2)3.已知R-2R网络型D/A转换器VREF=+5V,试分别求出4位D/A转换器和8位D/A转换器的最大输出电压,并说明这种D/A转换器最大输出电压与位数的关系。解:4位D/A转换器的最大输出电压:8位D/A转换器的最大输出电压由此可见,最大输出电压随位数增加而增加,但增加幅度并不大。4.已知R-2R网络型D/A转换器VREF=+5V,试分别求出4位D/A转换器和8位D/A转换器的最小输出电压,并说明这种D/A转换器最小输出电压与位数的关系。解:4位D/A转换器的最小输出电压8位D/A转换器的最小输出电压位数越多,最小输出电压越小。5.由555定时器、3位二进制加计数器、理想运算放大器A构成如图P7.5

1数字逻辑基础习题解答140所示电路。设计数器初始状态为000,且输出低电平VOL=0V,输出高电平VOH=3.2V,Rd为异步清零端,高电平有效。(1)说明虚框(1)、(2)部分各构成什么功能电路?(2)虚框(3)构成几进制计器?(3)对应CP画出vO波形,并标出电压值。图P7.5解:(1)虚框(1)电路为多谐振荡器,虚框(2)电路为D/A转换器,(2)虚框(3)为4进制计数器(3)利用叠加定理可得D/A转换器的输出表达式为当Q2Q1Q0=000时,vO=0V;当Q2Q1Q0=001时,vO=-0.4V;当Q2Q1Q0=010时,vO=-0.8V;当Q2Q1Q0=011时,vO=-1.2V;因此,对应CP的vO波形为:6.一程控增益放大电路如图P7.6所示,图中Di=1时,相应的模拟开关Si与vI相接;

1数字逻辑基础习题解答140Di=0,Si与地相接。(1)试求该放大电路的电压放大倍数与数字量D3D2D1D0之间的关系表达式;(2)试求该放大电路的输入电阻与数字量D3D2D1D0之间的关系表达式。图P7.6解:(1)(2)7.对于一个8位D/A转换器:(1)若最小输出电压增量VLSB为0.02V,试问当输入代码为01001101时,输出电压vO为多少伏?(2)假设D/A转换器的转换误差为1/2LSB,若某一系统中要求D/A转换器的精度小于0.25%,试问这一D/A转换器能否应用?解:(1)当8位D/A转换器的最小输出电压增量为0.02V时,输入代码为01001101所对应的输出电压:vO=0.02(26+23+22+20)=1.54V。(2)8位D/A转换器的分辨率百分数为:(3)由于D/A转换器的转换误差为1/2LSB,若要求D/A转换器的精度小于0.25%(精度是转换误差与最大输出电压之比),则其分辨率应小于0.5%,因此这一8位D/A转换器满足要求。8.A/D转换器中取量化单位为Δ,把0~10V的模拟电压信号转换为3位二进制代码,若最大量化误差为Δ,要求列表表示模拟电平与二进制代码的关系,并指出Δ的值。

1数字逻辑基础习题解答140模拟电平二进制代码000001010011100101110111解:模拟电平(V)二进制代码0<vI≤1.250001.25<vI≤2.50012.5<vI≤3.750103.75<vI≤5.00115.0<vI≤6.251006.25<vI≤7.51017.5<vI≤8.751108.75<vI≤10.01119.一个6位并行比较型A/D变换器,为量化0~5V电压,问量化值△应为多少?共需多少比较器?工作时是否要取样保持电路?为什么?解:共需要63个比较器。工作时不需要采样保持器,因为转换速度极快,在转换过程中可认为输入电压不变。10.3位并行比较型A/D转换器原理图如图P7.12所示。基准电压VREF=3.2V。(1)该电路采用的是哪种量化方式?其量化误差为何值?(2)该电路允许变换的电压最大值是多少?(3)设输入电压VI=2.213V,问图中编码器的相应输入数据C6C5C4C3C2C1C0和输出数据D2D1D0各是多少?解:(1)采用4舍5入的量化方式。。电路的最大量化误差不大于。(2)该电路允许变换的电压最大值为:

1数字逻辑基础习题解答140(3)当输入电压为2.213V时,代码转换器(即编码器)的输入数据C6C5C4C3C2C1C0=0011111,输出数据D2D1D0=101。11.如图P7.11(a)所示为一4位逐次逼近型A/D转换器,其4位D/A输出波形vO与输入电压vI分别如图P7.11(b)和(c)所示。(1)转换结束时,图P7.11(b)和(c)的输出数字量各为多少?(2)若4位A/D转换器的输入满量程电压VFS=5V,估计两种情况下的输入电压范围各为多少?(a)(b)(c)图P7.11解:(1)图(b)输出的数字量为0100,图(c)输出的数字量为1011(2)VLSB=,且A/D转换器采用只舍不入量化方式。输出数字量0100对应的电压范围为1.25<vI<1.5625;输出数字量1011对应的电压范围为3.4375<vI<3.75。12.计数式A/D转换器框图如图P7.12所示。D/A转换器输出最大电压vomax=5V,vI为输入模拟电压,X为转换控制端,CP为时钟输入,转换器工作前X=0,RD使计数器清零。已知,vI>vO时,vC=1;vI≤vO时,vC=0。当vI=1.2V时,试问(1)输出的二进制数D4D3D2D1D0=?(2)转换误差为多少?(3)如何提高转换精度?图P7.12

1数字逻辑基础习题解答140解:(1)A/D分辨率即最小量化单位当VI=1.2V时,(2)转换误差=23×S-1.2=0.903V(3)可用两种措施:增加计数器位数采用四舍五入量化,在D/A输出加一个负向偏移电压1/2VLSB。对于n位的计数型A/D转换器,其最大的转换时间可达2n-1个时钟周期。而且计数器的时钟频率不能太高,以便在每个时钟周期内DAC能建立稳定的电压输出。因此,计数型A/D转换器只能用于对转换速度要求不高的场合。13.10位双积分型D/A转换器的基准电压VREF=8V,时钟频率fCP为1MHz,则当输入电压vI=2V时,完成A/D转换器所需要的时间。解:第1次积分所需要的时间:T1=TCP×210=1us×1024=1024us第2次积分所需要的时间:T2=TCP×210×0.25=1us×256=256us总共需要时间T=T1+T2=1024+256=1280us14.双积分式A/D如图P7.14所示。(1)若被测电压vI(max)=2V,要求分辨率≤0.1mV,则二进制计数器的计数总容量N应大于多少?(2)需要多少位的二进制计数器?(3)若时钟频率fcp=200kHz,则采样保持时间为多少?(4)若fcp=200kHz,∣vI∣<∣VREF∣=2V,积分器输出电压的最大值为5V,此时积分时间常数RC为多少毫秒?图P7.14解:(1)ADC的分辨率为:

1数字逻辑基础习题解答140计数器的总容量N为:(回答20000亦可算对)(2)∵215-1<N<215故需15位的二进制计数器,如果包括控制开关S用的一位时,应采用16位二进制计数器。(回答15位可以算对)(3)采样/保持时间(4)则RC=65.536ms自我检测题1.什么是数字系统?数字系统是指对数字信息进行存储、传输、处理的电子系统。只要包括控制单元和数据处理单元就称为数字系统。2.说明自顶向下的设计方法及步骤。首先从系统设计入手,在顶层将整个系统划分成几个子系统,然后逐级向下,再将每个子系统分为若干功能模块,每个功能模块还可以继续向下划分成子模块,直至分成许多最基本模块实现。练习题1.如图P8.1(a)是一电机数字转速表原理框图。电机转动一圈,红外线光电转换电路产生一个脉冲。记录一秒钟脉冲的个数并用四只七段数码管显示出来,即可测量出被测物体每秒的转数。信号源是石英晶体多谐振荡器,振荡频率为2048Hz,框图中各点的波形如图P8.1(b)所示。(1)写出框图中电路1至电路5的名称;(2)写出控制电路可综合的VHDL代码;(3)用QuartusII对控制电路进行仿真。

1数字逻辑基础习题解答140(a)(b)图P8.1解:(1)电路1:分频器电路2:施密特触发器电路3:计数器电路4:锁存器电路5:BCD-七段码译码(2)控制电路可以采用摩尔状态机实现。其状态转换图如图所示。该状态机由频率为8Hz的时钟驱动,每隔0.125s,状态变化一次。控制电路采用摩尔型状态机,10个状态采用Gray码编码,以消除控制信号的毛刺。control的VHDL代码为libraryieee;useieee.std_logic_1164.all;entitycontrolisport(CLK:instd_logic;CS,R,L:outstd_logic);endcontrol;architecturebehavofcontrolissignalcurrent_state,next_state:std_logic_vector(3downto0);constantS0:std_logic_vector:=“0000”;constantS1:std_logic_vector:=“0001”;constantS2:std_logic_vector:=“0011”;constantS3:std_logic_vector:=“0010”;constantS4:std_logic_vector:=“0110”;constantS5:std_logic_vector:=“0111”;

1数字逻辑基础习题解答140constantS6:std_logic_vector:=“1111”;constantS7:std_logic_vector:=“1110”;constantS8:std_logic_vector:=“1100”;constantS9:std_logic_vector:=“1000”;begincom:process(current_state)begincasecurrent_stateiswhenS0=>next_state<=S1;R<=‘1’;CS<=‘0’;L<=‘0’;whenS1=>next_state<=S2;R<=‘0’;CS<=‘1’;L<=‘0’;whenS2=>next_state<=S3;R<=‘0’;CS<=‘1’;L<=‘0’;whenS3=>next_state<=S4;R<=‘0’;CS<=‘1’;L<=‘0’;whenS4=>next_state<=S5;R<=‘0’;CS<=‘1’;L<=‘0’;whenS5=>next_state<=S6;R<=‘0’;CS<=‘1’;L<=‘0’;whenS6=>next_state<=S7;R<=‘0’;CS<=‘1’;L<=‘0’;whenS7=>next_state<=S8;R<=‘0’;CS<=‘1’;L<=‘0’;whenS8=>next_state<=S9;R<=‘0’;CS<=‘1’;L<=‘0’;whenS9=>next_state<=S0;R<=‘0’;CS<=‘0’;L<=‘1’;whenothers=>next_state<=S0;R<="0";CS<="0";L<="0";endcase;endprocesscom;reg:process(clk)beginif(clk"eventandclk="1")thencurrent_state<=next_state;endif;endprocessreg;endbehav;(3)仿真结果2.某交通十字路口的示意图如图P8.2-2(a)所示。在主干道和支干道上两个方向上都安装红、黄、绿三色信号灯。Ca和Cb

1数字逻辑基础习题解答140分别是安装在主干道和支干道上的传感器,输出高电平说明有车需要通过。交通信号灯的技术要求为:图8.2-2(1)主干道的通车时间最短为60秒,超过60秒后,如果支干道上有车,则交通灯改变,即主干道黄灯亮10秒后,支干道绿灯亮;(2)支干道的通车时间最短为50秒,超过50秒后,如果支干道上还有车,而主干道无车,则支干道一直保持绿灯亮,其它情况交通灯改变,即支干道黄灯亮10秒后,主干道绿灯亮。按上述要求设计交通灯控制器。画出交通灯控制器状态图,写出交通灯控制器的VHDL代码。解:交通灯控制器可采用摩尔型状态机设计。状态机由一周期为10秒的时钟信号控制,每隔10秒钟状态就会变化一次。交通灯控制器的状态图如图所示。图中符号GaRb表示Ga=Gb=1,其它的输出变量均为0。箭头上的表示Ca=0且Cb=1时,状态将按箭头方向转移。交通灯控制器VHDL代码如下:libraryieee;useieee.std_logic_1164.all;useieee.std_logic_signed.all;entitytrafficisport(clk,Ca,Cb:instd_logic;

1数字逻辑基础习题解答140Ra,Ya,Ga,Rb,Yb,Gb:outstd_logic);end;architectureoneoftrafficissignalstate,nextstate:integerrange0to12;beginprocess(state,Ca,Cb)beginRa<="0";Ya<="0";Ga<="0";Rb<="0";Yb<="0";Gb<="0";casestateiswhen0to4=>Ga<="1";Rb<="1";nextstate<=state+1;when5=>Ga<="1";Rb<="1";if(Cb="1")thennextstate<=6;elsenextstate<=5;endif;when6=>Ya<="1";Rb<="1";nextstate<=7;when7to10=>Ra<="1";Gb<="1";nextstate<=state+1;when11=>Ra<="1";Gb<="1";if(Ca="1"orCb="0")thennextstate<=12;elsenextstate<=11;endif;when12=>Ra<="1";Yb<="1";nextstate<=0;endcase;endprocess;process(clk)beginif(clk"eventandclk="1")thenstate<=nextstate;endif;endprocess;end;3.某交通十字路口的示意图如图P8.2-3(a)所示。在主干道和支干道上两个方向上都安装红、黄、绿三色信号灯。Ca和Cb分别是安装在主干道和支干道上的传感器,输出高电平表示有车需要通过。交通灯控制系统的功能要求为:(1)如果只有一个方向有车时,则保持该方向畅通;当两个方向都有车时,主干道和支干道交替通行;(2)在只有主干道有车时,主干道亮绿灯,支干道亮红灯;当只有支干道有车时,主干道亮红灯,支干道亮绿灯;(3)当两个方向都有车时,则轮流亮绿灯和红灯。主干道每次亮绿灯40秒,支干道每次亮绿灯20秒,在由绿灯转红灯之间亮5秒的黄灯;(4)用7段LED数码管显示亮灯时间。

1数字逻辑基础习题解答140图P8.2-3(b)所示为交通灯控制系统结构框图。控制系统由控制器和定时器两部分组成。定时器用于亮灯时间控制,CNT是由控制器传送到定时器的初始定时值,LD是初始定时值的同步预置信号,高电平有效。ST是定时器状态信号,当定时结束时,ST输出为高电平。clk是周期为秒的时钟信号。reset是复位信号,低电平有效。(a)(b)图P8.2-3根据交通灯控制系统的功能要求和结构图,完成以下内容:(1)画出控制器的状态转换图;(2)写出控制器和定时器的可综合的VHDL代码;(3)设计交通灯控制系统的顶层原理图;解:(1)控制器模块控制器的状态转换图如图所示。由S0、S1、S2、S3四个不同的状态组成,分别表示4种不同的信号灯状态。控制模块control的VHDL代码libraryieee;useieee.std_logic_1164.all;useieee.std_logic_signed.all;entitycontrolisport(reset,clk,ST,Ca,Cb:instd_logic;Ra,Ya,Ga,Rb,Yb,Gb,LD:outstd_logic;CNT:OUTbit_vector(7downto0));end;architectureoneofcontrolis

1数字逻辑基础习题解答140constantT1:bit_vector(7downto0):="01000000";constantT2:bit_vector(7downto0):="00100000";constantT3:bit_vector(7downto0):="00000101";constantS0:bit_vector(1downto0):="00";constantS1:bit_vector(1downto0):="01";constantS2:bit_vector(1downto0):="11";constantS3:bit_vector(1downto0):="10";signalstate:bit_vector(1downto0);beginprocess(reset,clk)beginif(reset="0")thenstate<=S0;elsif(clk"eventandclk="1")thenif(ST="1")thencasestateiswhenS0=>if(Cb="0")thenstate<=S0;elsestate<=S1;endif;whenS1=>state<=S2;whenS2=>if(Ca="0")thenstate<=S2;elsestate<=S3;endif;whenS3=>state<=S0;endcase;endif;endif;endprocess;process(state,Ca,Cb)beginRa<="0";Ya<="0";Ga<="0";Rb<="0";Yb<="0";Gb<="0";casestateiswhenS0=>Ga<="1";Rb<="1";if(Cb="0")thenCNT<=T1;elseCNT<=T3;endif;whenS1=>Ya<="1";Rb<="1";CNT<=T2;whenS2=>Ra<="1";Gb<="1";if(Ca="0")thenCNT<=T2;elseCNT<=T3;endif;whenS3=>Ra<="1";Yb<="1";CNT<=T1;endcase;endprocess;LD<=ST;end;(2)定时器模块定时器模块counter

1数字逻辑基础习题解答140的逻辑功能为BCD减法计数器。初始计数值通过LD预置。计数器计到0后,给出高电平的状态信号ST。定时器模块的VHDL代码:libraryieee;useieee.std_logic_1164.all;useieee.std_logic_signed.all;entitycounterisport(reset,clk,LD:instd_logic;CNT:instd_logic_vector(7downto0);BCD1:outstd_logic_vector(3downto0);BCD0:outstd_logic_vector(3downto0);ST:outstd_logic);end;architectureoneofcounterissignalQ:std_logic_vector(7downto0);beginprocess(reset,clk)beginif(reset="0")thenQ<="00000000";elsif(clk"eventandclk="1")thenif(LD="1")thenQ<=CNT;elsif(Q(3downto0)="0000")thenQ<=Q-7;elseQ<=Q-1;endif;endif;endprocess;process(Q)beginif(Q=0)thenST<="1";elseST<="0";endif;endprocess;BCD0<=Q(3downto0);BCD1<=Q(7downto4);end;(3)BCD-7段显示译码器模块假设显示器件采用共阴LED数码管,其VHDL代码为libraryieee;

1数字逻辑基础习题解答140useieee.std_logic_1164.all;entitydecoderisport(din:instd_logic_vector(3downto0);led7s:outstd_logic_vector(6downto0));end;architectureoneofdecoderisbeginprocess(din)begincasediniswhen"0000"=>led7s<="0111111";when"0001"=>led7s<="0000110";when"0010"=>led7s<="1011011";when"0011"=>led7s<="1001111";when"0100"=>led7s<="1100110";when"0101"=>led7s<="1101101";when"0110"=>led7s<="1111101";when"0111"=>led7s<="0000111";when"1000"=>led7s<="1111111";when"1001"=>led7s<="1101111";when"1010"=>led7s<="1110111";when"1011"=>led7s<="1111100";when"1100"=>led7s<="0111001";when"1101"=>led7s<="1011110";when"1110"=>led7s<="1111001";when"1111"=>led7s<="1110001";whenothers=>led7s<=null;endcase;endprocess;end;(4)交通灯控制系统traffic的顶层原理图根据设计要求,交通灯控制系统traffic的顶层原理图如图所示。图中CA、CB、RESET、CLK为输入信号,输出信号RA、YA、GA、RB、YB、GB用于驱动交通信号灯,高电平表示信号灯亮。LED7S1[6..0]、LED7S1[6..0]驱动两只共阴的7段LED数码管。

1数字逻辑基础习题解答1405.设计一4×4的编码式键盘接口电路。原理框图如图P8.2-4所示。图中Y0~Y3为列扫描信号,低电平有效;X0~X3为行输入线,当没有按键按下时,输入被上拉电阻拉成高电平。主要功能要求:图P8.2-4(1)将每个按键转化为4位键编码。当K0按下时,D3~D0输出键编码为0000,…,当K15按下时,输出键编码为1111。同时,检测到有效按键时,DAV给出高电平信号。(2)具有按键消抖功能。画出键盘接口电路原理框图,写出译码器、消抖电路和扫描器的VHDL代码。解:键盘扫描器采用以下设计方按:(1)检测有无键按下,方法是将Y0~Y3同时置成低电平,如果有键按下,键检测信号K=X3X2X1X0变为低电平。(2)判断何键按下,采用逐列扫描的方法,确定闭合键的位置。(3)等待按键松开,方法是将Y0~Y3同时置成低电平,如果键松开,则键检测信号K恢复为高电平。第(3)个步骤是必要的,这样可以保证每次按键只生成一个有效信号。

1数字逻辑基础习题解答140机械式按键闭合初始阶段,会产生抖动,键盘接口电路应具有消抖功能。按键消抖是通过一个具有异步清零和保持功能的16进制加法计数器(CNT16A)来检测的。其基本原理是:将键检测信号K作为CNT16A的清零信号。当没有键按下时,K为高电平,CNT16A一直处于清零状态;当有按键闭合时,K变为低电平,CNT16A在时钟信号的作用下计数。当CNT16A计到15(Q3Q2Q1Q0=1111)时,停止计数并保持该计数值直到按键松开,K恢复成高电平。假设CNT16A的时钟信号周期为1ms,则只有按键闭合时间超过15ms时,CNT16A的计数值才能由0计到15。由于按键抖动产生的脉冲高低电平持续时间一般不超过10ms,因此只有按键稳定闭合后,CNT16A的计数值才有可能达到15。将CNT16A的状态相与非得到键有效信号KAV,即。当键稳定闭合时,键有效信号KAV产生由高到低的跳变。键有效以后,应通过译码电路将闭合的键转化为4位键编码。键编码决定于闭合键的位置,即由X0~X3和Y0~Y3决定。译码器真值表如表所示。需要指出的是,该译码器具有8个输入变量,但只有16种有效组合,其余组合可视为无关项。X3X2X1X0Y3Y2Y1Y0D3D2D1D0111011100000111011010001111010110010111001110011110111100100110111010101110110110110110101110111101111101000101111011001101110111010101101111011011111101100011111011101011110111110011101111111根据真值表,可直接写出输出的函数表达式。,D2=X2X0,,得到4位键值以后,再存入寄存器。根据上述思路,可得到如图所示的键盘扫描电路原理框图。

1数字逻辑基础习题解答140libraryieee;useieee.std_logic_1164.all;useieee.std_logic_signed.all;entitykeyisport(clk,X0,X1,X2,X3:inbit;Y0,Y1,Y2,Y3:bufferbit;D0,D1,D2,D3,DAV:outbit);end;architectureoneofkeyissignalK,KAV,LOCK:bit;signalq:std_logic_vector(3downto0);signalstate,nextstate:integerrange0to6;beginK<=X0andX1andX2andX3;DAV<=KAV;process(clk,K)——消抖beginif(clk"eventandclk="1")thenif(K="1")thenq<="0000";elsif(q=15)thenq<="1111";elseq<=q+1;endif;endif;endprocess;process(q)begin

1数字逻辑基础习题解答140if(q="1111")thenKAV<="0";elseKAV<="1";endif;endprocess;键盘扫描器ASM图process(state,Y0,Y1,Y2,Y3,K,KAV)——键盘扫描beginY0<="1";Y1<="1";Y2<="1";Y3<="1";casestateiswhen0=>nextstate<=1;LOCK<="0";when1=>Y0<="0";Y1<="0";Y2<="0";Y3<="0";LOCK<="0";if(KAV="0")thennextstate<=2;elsenextstate<=1;endif;when2=>Y0<="0";LOCK<="1";ifK="0"thennextstate<=6;elsenextstate<=3;endif;when3=>Y1<="0";LOCK<="1";ifK="0"thennextstate<=6;elsenextstate<=4;endif;when4=>Y2<="0";LOCK<="1";ifK="0"thennextstate<=6;elsenextstate<=5;endif;when5=>Y3<="0";LOCK<="1";nextstate<=6;when6=>Y0<="0";Y1<="0";Y2<="0";Y3<="0";LOCK<="0";ifK="1"thennextstate<=1;elsenextstate<=6;endif;endcase;endprocess;process(clk)——译码及寄存beginifclk="1"andclk"eventthenstate<=nextstate;ifLOCK="1"thenD3<=X1andX0;D2<=X2andX0;

1数字逻辑基础习题解答140D1<=Y1andY0;D0<=Y2andY0;endif;endif;endprocess;end;'

您可能关注的文档

- 数字图像处理 (许录平 著)课后习题答案 科学出版社.pdf

- 数字图像处理与分析习题及答案.doc

- 数字电子技术基础 阎石第四版课后习题答案详解.pdf

- 数字电子技术基础习题及答案1.pdf

- 数字电子技术基础课后答案 阎石 第五版 第一章第二章 习题答案.pdf

- 数字电子技术第三章习题答案.doc

- 数字电子技术课后习题答案(全部).doc

- 数字电路与系统设计课后答案.pdf

- 数字电路与逻辑设计课后答案邹红.pdf

- 数字电路逻辑设计课后答案.docx

- 数字通信原理课后习题答案.doc

- 数字逻辑习题答案 毛法尧 第二版.doc

- 数字逻辑第四章课后答案.doc

- 数字逻辑设计基础答案 (第1-13章).pdf

- 数字集成电路教程课后答案.pdf

- 数学书籍推荐.docx

- 数学新浙教版八年级5.1《常量与变量》同步练习题【带详解答案】.doc

- 数学模型第三版(高等教育出版社)课后习题答案.doc

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明