- 1.62 MB

- 2022-04-22 11:51:03 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'数字电路与系统设计课后答案

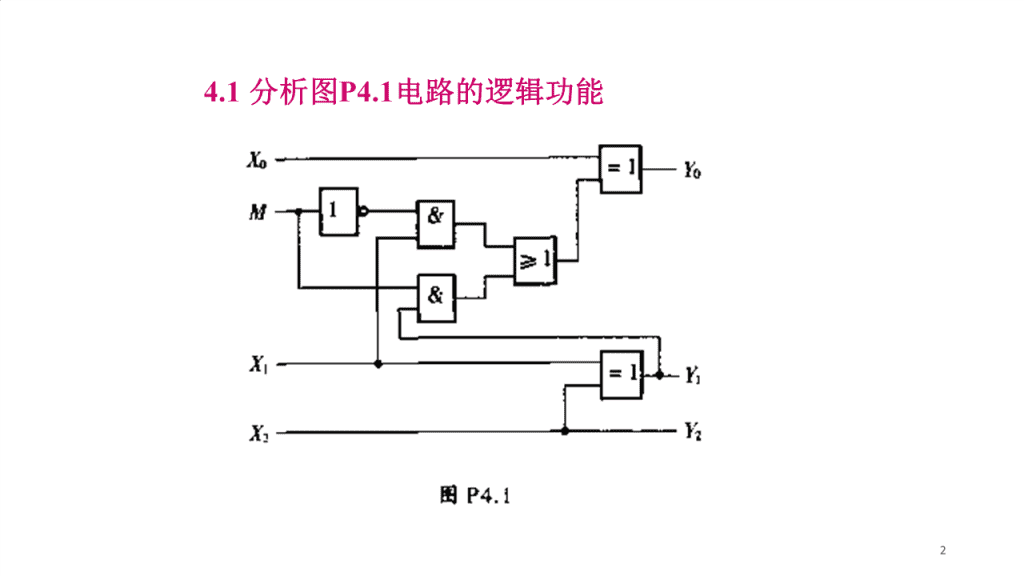

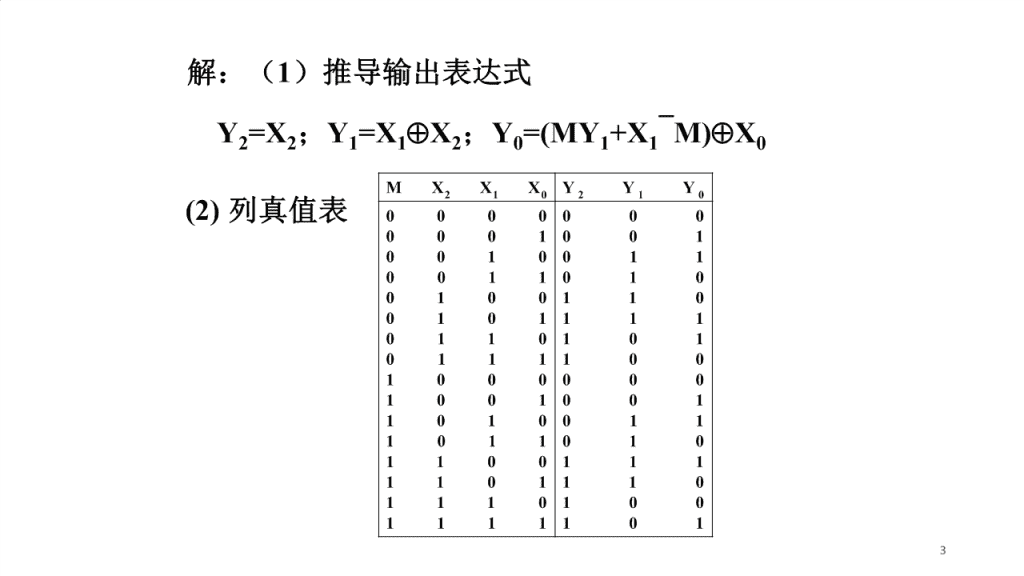

4.1分析图P4.1电路的逻辑功能2

解:(1)推导输出表达式Y2=X2;Y1=X1X2;Y0=(MY1+X1M)X0MXXXYYY210210(2)列真值表00000000001001001001100110100100110010111101101010111100100000010010011010011101101011001111101110111010011111013

(3)逻辑功能:当M=0时,实现3位自然二进制码转换成3位循环码。当M=1时,实现3位循环码转换成3位自然二进制码。4

1234.2分析图P4.2电路的逻辑功能。B=1=1CF1D&A11F2&图P4.25CBA123

解:(1)从输入端开始,逐级推导出函数表达式F1=A⊕B⊕CF2=A(B⊕C)+BC=ABC+ABC+ABC+ABC(2)列真值表6

(3)确定逻辑功能ABCFF1200000假设变量A、B、C和00111函数F1、F2均表示一01011位二进制数,那么,01101由真值表可知,该电10010路实现了全减器的功10100能。11000111117

A、B、C、F1、F2分别表示被减数、减数、来自低位的借位、本位差、本位向高位的借位。A被减数-B减数F2C借位F1差8

4.4设ABCD是一个8421BCD码,试用最少与非门设计一个能判断该8421BCD码是否大于等于5的电路,该数大于等于5,F=1;否则为0。解:(1)列真值表9

ABCDFABCDF00000100010001010011001001010Ø001101011Ø010001100Ø010111101Ø011011110Ø011111111Ø10

(2)写最简表达式CDAB0001111000F=A+BD+BC0111111ØØØØ=A·BD·BC1011ØØ(3)画逻辑电路,如下图所示:11

D&BD&&FCA&题4.4图12CBA1234

4.10电话室对3种电话编码控制,按紧急次序排列优先权高低是:火警电话、急救电话、普通电话,分别编码为11,10,01。试设计该编码电路。解:设火警为A,急救为B,普通为C,列真值表为:ABCFF1211101100010100013

BCA0001111001111111F1=A+BBCA000111100111111F2=AB14

4.11试将2/4译码器扩展成4/16译码器A3A1ENY3A02/4Y2A2译码器Y1Y0ENENENENAA12/4(1)A12/4(2)A12/4(3)A12/4(4)1A0AAA000A0Y0Y1Y2Y3Y0Y1Y2Y3Y0Y1Y2Y3Y0Y1Y2Y3Y0Y1Y2Y3Y4Y5Y6Y7Y8Y9Y10Y11Y12Y13Y14Y1515

4.12试用74138设计一个多输出组合网络,它的输入是4位二进制码ABCD,输出为:F1:ABCD是4的倍数。F2:ABCD比2大。F3:ABCD在8~11之间。F4:ABCD不等于0。16

解:由题意,各函数是4变量函数,故须将74138扩展为4-16线译码器,让A、B、C、D分别接4-16线译码器的地址端A3、A2、A1、A0,可写出各函数的表达式如下:F1(A,B,C,D)m(0,4,8,12)=m0m4m8m12=Y0Y4Y8Y1217

F2(A,B,C,D)m(0,1,2)=m0m1m2=Y0Y1Y2F3(A,B,C,D)m(8,9,10,11)=m8m9m10m11=Y8Y9Y10Y11F(A,B,C,D)m40=Y018

123456实现电路如下图所示:F1Y0DA0&Y1F2CA1Y2BA2Y3D74138DY41E1Y5AE2A&Y60E2BY7F3Y0A0Y1A1Y2A2Y3&74138Y4E1F4Y50E2AY60E2BY719CCBBAATitleSizeNumberRevisionBDate:4-Mar-2002SheetofFile:E:DesignExplorer99SELibraryYangHengXinMyDesign.ddbDrawnBy:123456

4.13试将八选一MUX扩展成三十二选一MUX。A2A1A0ENA2A1A0YD0D0D01D174151(1)YD2D3D4D5DD67D7A5A2Y0A4A1Y1YAA0Y21374138Y31E1Y40E2AY5E2BY60ENY7A2A1A0D56D0D57D174151(8)YD2Y7D3D4D5D6D63D720

4.14试用74151实现下列函数:(1)F(A,B,C,D)m(1,2,4,7)。(4)F(A,B,C,D)m(0,3,12,13,14)(7,8)。解:(1)函数有4个输入变量,而74151的地址端只有3个,即A2、A1、A0,故须对函数的卡诺图进行降维,即降为3维。21

CD00011110BCAB000111100011A0DDDD0111100001110A1A0令A=A2、B=A1、A000111102C=A0则:0D0D1D3D2D=D=D,1D4D5D7D603D1=D2=D,D4=D5=D6=D7=022

相应的电路图如下所示:ENCA0BA1CAA2DD0D174151YFDD2D3D4D5D6D723BA1

(4)函数有4个输入变量,而74151的地址端只有3个,即A2、A1、A0,故须对函数的卡诺图进行降维,即降为3维。BC00011110ACD0DD0000011110AB100D1001101ØA1A011111A00011110210Ø0D0D1D3D21D4D5D7D624

令A=A2、B=A1、C=A0则:D0=D7=D,ENCA0D=D,D=1,BA1C16AA2DD0D2=D3=D4=D5=0。DD174151YFD2D3相应的电路图D4D5如右图所示:1D6DD74.14(4)25BA12

4.15用½74153实现下列函数:(1)F(A,B,C,D)m(1,2,4,7,15)。解:(1)函数有4个输入变量,而½74153的地址端只有2个,即A1、A0,故须对函数的卡诺图进行降维,即降为2维。26

CD00011110BCAB000111100011A0DDDD0111100D011110AB00101A1A0DD0C⊕DC⊙D011DD10CD2327

令A=A1、B=A0,则:D0=C⊕D,D1=C⊙D,D2=0,D3=CD,相应的电路图如下图所示:BA0=1AA1CD1_0741532=D1YFD2&D3ENCD28BA123

4.16试在图4.2.31的基础上增加一片7485,构成25位数据比较器。A24A23A22A21B24B23B22B21A19A18A17A16B19B18B17B16A14A13A12A11B14B13B12B11A9A8A7A6B9B8B7B6A3A2A1A0B3B2B1B0A3A2A1A0B3B2B1B0A3A2A1A0B3B2B1B0A3A2A1A0B3B2B1B0A20A15A10A5(A>B)i(A>B)i(A>B)i(A>B)i====(A=B)7485(4)(A=B)i7485(1)(A=B)i7485(2)(A=B)i7485(3)i(ABFA=BFABFA=BFABFA=BFABFA=BFAB)i(A>B)i=(A=B)i7485(5)(A=B)i7485(6)(ABFA=BFABFA=BFABFA=BFA1001时,须加0110修正项进行调整,计算结果为C4C3C2C1C0。C4S3AA3AS3≥132AA22A2SC1ACO4A11A1COSC0AS3A030AS1C03CI74283S202CI74283S2CB3B3S11B3S1CB2B2S00BB2S0B1B01B01B0B030

4.18用74283将8421BCD码转换为余3BCD码。解:由于同一个十进制数码的余3BCD码比相应的8421BCD码大3,故用一片74283既可以实现,电路图如下所示:C8421BCDA0A1S0余A23BCDA3S10CI74283S20B0S30B11B2CO1B331BATitleSizeNumberBDate:5-Mar-2002File:E:DesignExplorer99SELibraryYangHengXinMyDesign.ddb12345

4.19用74283和必要的门电路将余3BCD码转换成8421BCD码。余3BCDA3A2ACO码18421BCDAS030CI74283S2BS1311B2S0码0B11B032

4.20用74283将8421BCD码转换为5421BCD码。分析:当一个十进制数码大于4时,其5421BCD码比相应的8421BCD码大3,其余情况下,两种BCD码一样,故用一片7485和一片74283可以实现C8421A08421BCDBA0A17485A1S余BCD0A2FA>BA23BCD5421A3A3S1BCD(A>B)i(A=B)0CI74283S2iFA=B(ABB2DAA10332Y数0(A>B)iA12D11(A=B)iFA=BB23D074157输0(AC1串入M74194CRM074194CR0DDDSRDSLSRSLRQCP>CPD0D1D2D3>CPD0D1D2D30111111CR

方法二:触发器输出作Q4’Q0’Q1’Q2’Q3’1Q4’Q5’Q6’Q7’Q8’1M1Q0Q1Q2Q3DQM1Q0Q1Q2Q31M0CR1M0CR串入DSR74194(1)DSL>C1DSR74194(2)DSLRQCP>CPD0D1D2D3>CPD0D1D2D30111111CR

方法三:触发器输出作Q0’BQ"0Q"1Q"2Q"3Q"4Q"Q"Q"Q"56781串行输入Q0Q1Q2Q31Q0Q1Q2Q311DCRM0CRM0RDC1CP74194(1)M1CP74194(2)M1RDSRDSLDSRDSLD0D1D2D3D0D1D2D3DSL01CPA123

6.5在下图基础上增加一片74194或DFF构成8位并行串行码的转换电路。启动&C&串行输出1Q0Q1Q2Q3Q0Q1Q2Q3CRM0CRM0CP74194(1)M1CP74194(2)M1DSRDSLDSRDSLD0D1D2D3D0D1D2D311CPD"3D"4D"5D"60D"D"D"012BATitleSizeNumberBDate:31-Mar-2002File:E:DesignExplorer99SELibraryYangHengXinMyDesign.ddb12345

启动&CC&串行输出1Q0Q1Q2Q3Q0Q1Q2Q3CRM0CRM0CP74194(1)M1CP74194(2)M1DSRDSLDSRDSLD0D1D2D3D0D1D2D311CPD"3D"4D"5D"60D"D"D"012BⅠⅡBM0M1下一操作QQQQQQQQ01230123启动øøøøøøøø11准备并入CP1↑0D′0D′1D′2D′3D′4D′5D′610准备右移CP2↑10D′0D′1D′2D′3D′4D′510准备右移CP3↑110D′0D′1D′2D′3D′410准备右移CP4↑1110D′0D′1D′2D′310准备右移ACP5↑11110D′0D′1D′210准备右移ATitleCP6↑111110D′0D′110准备右移SizeNumberRevisionCP7↑1111110BD′011准备并入Date:31-Mar-2002SheetofFile:E:DesignExplorer99SELibraryYangHengXinMyDesign.ddbDrawnBy:123456

MD方法一:触发器输出作Q’1001D=M110启动启动启动&&&&&&BBBBBBQ1"Q1"Q1"Q2"Q2"Q2"Q3"Q3"Q3"Q4"Q4"Q4"Q5"Q5"Q5"Q6"Q6"Q6"Q7"Q7"Q7"Q8"Q8"Q8"Q0"Q0"Q0"串行输出串行输出串行输出QQQ000QQQ111QQQ222QQQ333111QQQ000QQQ111QQQ222QQQ333111CRCRCRMMM000CRCRCRMMM0001D1D1DCPCPCP741947419474194(1)(1)(1)MMM111CPCPCP741947419474194(2)(2)(2)MMM111C1C1C1DDDSRSRSRDDDSLSLSLDDDSRSRSRDDDSLSLSLDDD000DDD111DDD222DDD333DDD000DDD111DDD222DDD333CPCPCPD"D"D"4D"D"D"5D"D"D"6D"D"D"774455667D"D"D"0D"D"D"1D"D"D"2D"D"D"300112233AAAAAATitleTitleTitleSizeSizeSizeNumberNumberNumberRevisionRevisionRevisionBBBDate:Date:Date:10-May-200210-May-200210-May-2002SheetofSheetofSheetofFile:File:File:C:MyDocumentsprotelC:MyDocumentsprotelC:MyDocumentsprotelDrawnBy:DrawnBy:DrawnBy:111222333444555666

状态转移表:Q"Q"Q"Q"Q"Q"Q"Q"Q"MM操作01234567801启动11准备并入CP0D0"D1"D2"D3"D4"D5"D6"D7"10准备右移1CP10D0"D1"D2"D3"D4"D5"D6"10准备右移2CP110D0"D1"D2"D3"D4"D5"10准备右移3CP1110D0"D1"D2"D3"D4"10准备右移4CP11110D0"D1"D2"D3"10准备右移5CP111110D0"D1"D2"10准备右移6CP1111110D0"D1"10准备右移7CP11111110D0"11准备并入8

方法二:触发器输出作Q4’MD10Q’3D=M1Q3’+M1D3’1D’3ⅠⅡM0M1下一操作QQQQQQQQ01234567启动øøøøøøøø11准备并入CP1↑0D′0D′1D′2D′3D′4D′5D′610准备右移CP2↑10D′0D′1D′2D′3D′4D′510准备右移CP3↑110D′0D′1D′2D′3D′410准备右移CP4↑1110D′0D′1D′2D′310准备右移CP5↑11110D′0D′1D′210准备右移CP6↑111110D′0D′110准备右移CP7↑1111110D′011准备并入

方法二:触发器输出作Q4’启动D=MQ’+MD’131311Q0’Q1’Q2’Q3’Q4’Q5’Q6’Q7’Q8’串行输出M1Q0Q1Q2Q3DQM1Q0Q1Q2Q31M0CR1M0CRDSR74194(1)DSL>C1DSR74194(2)DSL1RQCP>CPD0D1D2D3>CPD0D1D2D30D0’D1’D2’D3’D4’D5’D6’D7’CR

6.8分析图P6.8电路,画出其全状态转移图并说明能否自启动。BQ1Q2Q31J1J1JC1C1C11K1K1KCP图P6.8A12

解:1)该电路为异步时序电路,无输入控制信号,属于Moore型,其激励方程为:J=1,K=QnQn+1=[Qn+QnQn]·CP,1121121J=Qn,K=1232Qn+1=[QnQn]·CP,J=1,K=Qn232332次态方程为:n+1nnnQn+1=[Qn+QnQn]·Q,Q1=[Q1+Q2Q1]·CP3,3231Q2n+1=[Q3nQ2n]·CP,Q3n+1=[Q3n+Q2nQ3n]·Q1,

次态方程卡诺图Qn+1=[Qn+QnQn]·CP,1121Qn+1=[QnQn]·CP,232Qn+1=[Qn+QnQn]·Q,33231QnQnQnQnQnQn212121Qn300011110Qn00011110Qn0001111033011011110111111111Qn+1Qn+1Qn+1321

QnQnQnQnQnQn212121Qn300011110Qn00011110Qn0001111033011011101111111111Qn+1Qn+1Qn+1321序号QQQ3210000状态转移表1011200131104101偏离010001状态100101111101

QQQ321000011001有效循环101110010偏离状态100111图P6.8的状态转移图逻辑功能:该电路是一个M=5的具有自启动性的异步计数器

6.11试用JKFF设计符合图6.11波形,并且具备自启动性的同步计数电路。解:1)根据波形列状态转移表

解:1)根据波形列状态转移表QnQnQnQn+1Qn+1Qn+1321321CP0000100CP0100111CP0111012CP1011103CP1101004CP10000052)根据状态转移表知:有6个有效状态和2个偏离态,偏离态的输出先按任意项处理,由此可得次态方程卡诺图为:

QnQnQnQn+1Qn+1Qn+1321321CP0000100CP0100111CP0111012CP1011103CP1101004CP1000005在上面卡诺圈的圈法下,检查自启动性:001110,111101,两个偏离态都能进入有效循环,因此,以此圈法设计的电路具有自启动性。

求激励方程:Qn+1=QnQn+(Qn+Qn)Qn313123J=Qn,K=Qn+Qn31312Qn+1=(Qn+Qn)Qn+QnQnQn2312312J=Qn+Qn,K=QnQn231231Qn+1=QnQnQn+QnQn132121J=QnQn,K=Qn13212

6.12用四个DFF设计以下电路(1)异步二进制加法C计数器。(2)在(1)的基础上用复“0”法构成M=12的异步加法计数器。解(1)QQQQ43211D1D1D1DC1C1C1C1CPC(2)反馈状态为1100&Q3Q2Q1Q41D1D1D1DC1RC1RC1RC1CPBBAATS123DF12345

C&Q3Q2Q1Q41D1D1D1DC1RC1RC1RC1CPBA12345

BB6.13用四个DFF设计以下电路:(1)异步二进制减法计数器。(2)在(1)的基础上用复“0”法构成M=13的异步计数器。QQQQ43211D1D1D解(1)1DC1C1C1C1CP(2)反馈状态为0011。&Q4QQ2Q13AA1D1D1D1DC1C1C1C1RRRRCP123451234

&Q4QQ2Q13ATitle1D1D1D1DC1C1C1C1RRRRCPSizeBDate:File:12345

C6.17写出图P6.17电路的状态转移表及模长M=?1QQQQQCC3210PCR74161TLDDDDDCPCP32101nn解:由图知,74161的预置数为Q3Q211,预置数控制端L接Qn。电路先异步清零,则起始状D1B态为0000,列状态转移表如下所示。A1234

C题P6.17状态转移表1QQQQ3210QQQQQCC3210PCR74161T0000LDDDDDCPCP321000111010001111000B101111001111由状态转移表知,模长M=8,且具备自启动性。ATitleSizeBDate:File:12345

D6.18试分析图6.18能实现M=?的分频。&1QQQQQQQQPQCC3210PQCC3210TCR74161(2)TCR74161(1)LDDDDDCPLDDDDDCPCP32103210C解:74161(1)的Q3接至74161(2)的CP,两74161为异步级联,反馈状态为(4C)=76,又利用异步清0端,所以HM=76。BA123

6.19试用74161设计循环顺序为0,1,2,3,4,5,10,11,12,13,14,15,0,1…的模长为12的计数电路。解:思路:当计数计到5时,让其置数为10。反馈状态为0101。C1&1QQQQPQCC3210TCR74161LDDDDDCP32101010BA123

6.20试用74161设计能按8421BCD译码显示的0~59计数的60分频电路。解:思路:先将两片74161分别接成M=10和M=6的形式,再让两者级联,实现M=610=60。C&&1PQCCQ3Q2Q1Q0PQCCQ3Q2Q1Q0TCR74161(2)TCR74161(1)LDDDDDCPLDD3D2D1D0CP3210BA1234

6.22试分析图P6.22(b)计数器的分频比为多少?1QQQQQCC3210P1CR74161(1)TCPBLDDDDDCP32100011QQQQZQCC3210P1CR74161(2)TLDDDDDCP32100A12

CPQ0Q1Q2Q3LD1Q4Q5Q6Q7

解:两片74161都处于计数状态(P=T=1),第1片74161的预置数为(1001)2,第2片74161的预置数为(0111)2,都使用置最小数法实现任意进制计数器。对第1片74161:M1=N1-9,M1=7对第2片74161:M2=N2-7,M2=9两片74161采用异步级联方式,所以总模值M为M=M1M2=7×9=63即:fCP:fZ=63:1

6.23试说明图6.23电路的模值为多少,并画出74160(Ⅰ)的Q0、Q1、Q2、Q3端,74160(Ⅱ)的Q0和RD端的波形,至少画出一个周期。QCC

QCC解:M=15

6.35用DFF设计移存型序列信号发生器,要求产生的序列信号为(1)11110000…;解:①求触发器的级数M=8,由log2Mnlog2M1得n=3。②列状态转移表Q3Q2Q1状态转移路线模数111M=1111×

③取n=4,列状态转移表及相应D1的值。Q4Q3Q2Q1状态转移路线模数D1111101110M=80110001000√0000010001100111011111111

④求激励函数D1QQ21QQ000111104300111Ø01ØØ1ØD1=Q4110Ø00C100ØØØ⑤画电路图D1QQQQ43211D1D1D1DSC1SC1SC1SC1CPBATitleSizeNumberRevisionBDate:13-Apr-2002SheetofFile:E:DesignExplorer99SELibraryYangHengXinMyDesign.ddbDrawnBy:123456

6.37试用JKFF设计循环长度M=12的序列信号发生器。解:该题要求设计一个已知序列长度的序列信号发生器,可以用修改最长线性序列的方法得到:取n=4,M=2n-1=15的最长线性序列:111100010011010,将其左移3(15-12=3)位,再与本身相异或:

异或结果中寻找“1”后面接n-1个0的码,对应到原始序列得到的码为0001,所以反馈状态为Q4Q3Q2Q1。修改反馈函数为:f=(Q4Q3)起跳状态+全0项=(Q4Q3)Q4Q3Q2Q1+Q4Q3Q2Q1此时产生的序列为:111100011010(跳过了原序列0001后面的001的3位)

f=(Q4Q3)Q4Q3Q2Q1+Q4Q3Q2Q1123Q4&Q3Q3=1Q2Q41Q1Q4&Q3Q2Q1DQ4Q3Q2Q1Q01D1D1D1DZSSSSC1C1C1C1CPCBA123

6.40写出图P6.40中74161输出端的状态编码表及74151输出端产生的序列信号。0EN&A0A1A21D0QQQQ1D1FBQCC3210P174151Y0D2CR74161T1Q0D3Q0D41LDDDDDCP32100D50D60D7CP解:74161采用复0法,实现模M=10的计数器,A1234

0EN&A0A1A21D0QQQQ1D1FBQCC3210P174151Y0D2CR74161T1Q0D3Q0D41LDDDDDCP32100D5Q3Q2Q1Q0F0D60D7CP00001000110010174151输出端产生的序列信号为:00111010001111000110,…01010011000111110001A10010Title1/001/00SizeNumberBDate:13-Apr-2002File:E:DesignExplorer99SELibraryYangHengXinMyDesign.ddb12345

6.43试用74161、74151及少量与非门实现如下功能:当S=0时,产生序列1011010;当S=1时,产生序列1110100。SQQQF21000001解(1)采用计数型序列码发00010生器。将74161通过异步复00101零法实现模长为7的计数器。001110100001011(2)设计组合电路,列真值011000111φ表:100011001110101101101100111010111001111φ

QQSQQQF1021000001SQ200011110000100011100101011φ00111111φ010001011101011011010111φ100011001110101Q1Q010110Q2000111101100101SS111010111100SSφ01111φ

QQ10Q200011110EN01SS11D0SD74151Y11SSφ01D2FSD3SD4SD50D6D7A2A1A01PQQQQ32101T74161Qcc1LDCR>CPDDDDCP3210

6.44用74161、74151及若干与非门设计一电路同时输出两个不同的序列信号Z1=111100010,和Z2=101110001(不另加控制信号)。解:可以将74161变换成移位寄存器,实现移存型序列码发生器,产生序列码Z1,在将该74161和74151组和形成计数型序列码发生器产生序列码Z2。QQQQD3210SL111101110011000DSL=Q2Q0+Q3Q2+Q3Q2100010001000101010111011101111

DSL=Q2Q0+Q3Q2+Q3Q2列计数型序列码发生器的真值表:QQQZ3212Q0111111110011001100010001100100010101011001111

例:电路如下图所示。(1)该电路的模长M=_____138;(2)该电路______有(有、无)自启动性;(3)如门G的输出断开,则电路的状态Q3(II)Q2(II)Q1(II)Q0(II)Q3(I)Q2(I)Q1(I)Q0(I)为:________________________11111111。解:置最大数法实现任意进制计数器:LD=M–2,则(10001000)2=(136)10,M=136+2=138

7.1在图P7.1555定时器构成的多谐振荡器中设RA=RB=5kΩ,C=960pF。试求输出波形的振荡频率f及占空比q。解:输出波形的振荡周期为:TTT0.7(R2R)CPHPLAB312=0.715109601051.00810s振荡频率为11f5T1.0081049.910Hz99KHz109

7.1在图P7.1555定时器构成的多谐振荡器中设RA=RB=5kΩ,C=960pF。试求输出波形的振荡频率f及占空比q。占空比:tTRRWPHABqTTTR2RPHPLAB10==66.7%15110

7.2对于图P7.2占空比可调的多谐振荡器:(1)试计算其q最大值qmax和最小值qmin;(2)说明该电路在改变占空比时振荡频率f是否发生变化,原因何在?解:(1)tTRWPHAqTTTRRPHPLAB11q91.7%max121q8.3%min12111

7.2对于图P7.2占空比可调的多谐振荡器:(1)试计算其q最大值qmax和最小值qmin;(2)说明该电路在改变占空比时振荡频率f是否发生变化,原因何在?(2)该电路在改变占空比时振荡频率f不发生变化。因为TTT0.7(RR)CPHPLAB而(RARB)为常数。112

7.5己知施密特反相器的输入信号如图P7.4所示.试作出对应的输出波形Uo。113

7.5己知施密特反相器的输入信号如图P7.4所示.试作出对应的输出波形Uo。uIUT+UT-tOuOuOHtuOLO114

8.1有一个DAC电路,n=8,其分辨率是多少?解:分辨率=1/(2n-1)=1/(28-1)=0.392%8.3若倒T型DAC电路中R=RF=10KΩ,UREF=5V,求对应输入011,101,110这3种情况下的输出电压。解:URn1REFFiuon2Di2Ri0当输入数字量为011时,输出电压uO为:URn1REFFi515uon2Di33V2Ri028115

8.4一个8位逐次逼近式ADC要求转换时间小于200ns,则时钟周期TCP应为多少?解:逐次逼近式ADC转换器完成一次转换所需要的节拍数为(n+1),其中n为二进制代码的个数,完成一次转换所需的时间为(n+1)TCP,其中TCP为时钟脉冲周期。因此:(n+1)TCP≤200nsTCP≤200/9=22.2ns。116

8.5有一个ADC电路,UI=10V,n=4,试分别求出舍尾量化和四舍五入量化方式时的量化单位∆。如果UI=6.28V,则转换后的数字量分别为什么?117

舍尾法四舍五入法量化量化编码编码电平电平10V量化单位量化单位30/3115∆1111∆=1/16×10V111115∆15/1628/3114∆1110∆=2/31×10V111014∆14/16=0.625V26/3113∆1101=0.645V110113∆13/1624/3112∆1100最大量化110012∆12/1622/3111∆1011最大量化101111∆11/16误差20/3110∆1010误差101010∆10/16=1∆10019∆9/1618/319∆1001=½∆16/318∆10006.875V10008∆8/1614/317∆011101117∆7/166.25V01106∆6/1612/316∆011001015∆5/1610/315∆01016.77V10.5∆uI=6.2801004∆4/168/314∆010000113∆3/166/313∆00116.13V9.5∆00102∆2/164/312∆001000011∆1/162/311∆00016.28在9.5∆~10.5∆之00000∆000∆0000间,量化成10∆。6.28在10∆~11∆之118间。量化成10∆。0V

例:有一个ADC电路,UREF=5V,n=4,试分别求出采用四舍五入量化和舍尾量化方式时的量化单位△。如果uI=3.9V,则转换后的数字量分别为多少?若用自然二进制码表示转换后的数字量,则对应的代码分别是什么?解:1.采用四舍五入量化方式:22量化单位n1UREF50.323(V)2131u在(11.5~12.5)之间,被量化为(12),I10相应的自然二进制码为:(1100)。自然二进制码119

例:有一个ADC电路,UREF=5V,n=4,试分别求出采用四舍五入量化和舍尾量化方式时的量化单位△。如果uI=3.9V,则转换后的数字量分别为多少?若用自然二进制码表示转换后的数字量,则对应的代码分别是什么?解:2.采用舍尾量化方式:11量化单位U50.313(V)nREF216u在(12~13)之间,被量化为(12),I10相应的自然二进制码为:(1100)。自然二进制码120

9.2试用ROM阵列图实现下列一组多输出逻辑函数F(A,B,C)ABABBC1F2(A,B,C)m(3,4,5,7)F(A,B,C)ABCABCABCABCABC3解:首先应将以上三个逻辑函数化成由最小项组成的标准“与-或”式,即F1(A,B,C)m(2,3,4,5,7)F2(A,B,C)m(3,4,5,7)F3(A,B,C)m(0,1,3,6,7)121

mm07AA1BB1CC1(D)0F1(D)1F(D)22F3F1(A,B,C)m(2,3,4,5,7)F2(A,B,C)m(3,4,5,7)题9.1ROM阵列F3(A,B,C)m(0,1,3,6,7)122

9.7有容量为256×4,64K×1,1M×8,128K×16为的ROM,试分别回答:这些ROM有多少个基本存储单元?这些ROM每次访问几个基本存储单元?这些ROM个有多少个地址线?答:(1)分别有1024个,1024×64个,1M×8个,128K×16个。(2)分别为4个,1个,8个,16个。(3)分别有8,16,20,17条地址线123

9.7试用位扩展方法,将2片256×4位的RAM组成一个256×8位的RAM,画出电路图。CSR/WA0A7A7LA0R/WCSA7LA0R/WCS256×4(I)256×4(Ⅱ)D3D2D1D0D3D2D1D0D7D6D5D4D3D2D1D0数据输出题9.7256×4芯片位扩展124

9.10用2114构成2K×8的静态存储器,画出逻辑图A101R/WA0A9A9…A0R/WCSA9…A0R/WCSA9…A0R/WCSA9…A0R/WCS2114×4(1)2114×4(2)2114×4(3)2114×4(4)D3D2D1D0D3D2D1D0D3D2D1D0D3D2D1D0D7...D0题9.7256×4芯片位扩展125

练习:试画出下图所示算法流程图的ASM图。要求状态数最少。0S11A←X,B←Y,C←0,R←0,CNT←0A←SL(A),R←SL(R),R0←A301R≥BC←SL(C)R←R-B,C←SL(C),CNT←CNT+1C←1,CNT←CNT+100CNT=41126

T000S1S111A←X,B←Y,A←X,B←Y,C←0,C←0,R←0,R←0,CNT←0CNT←0T1A←SL(A),R←SL(R),A←SL(A),R←SL(R),T201R≥B01C←SL(C)R←R-B,C←SL(C),R≥BCNT←CNT+1CNT←CNT+1C←SL(C)R←R-B,C←SL(C),CNT←CNT+1CNT←CNT+10CNT=410CNT=41271

12.2在T1状态下,如果控制输入Y和Z等于1和0,系统实现条件操作,寄存器增1,并转换到状态T2。试按上述条件画出一个部分ASM图。解:Y和Z优先权相同。128

12.2在T1状态下,如果控制输入Y和Z分别等于1和0,系统实现条件操作,寄存器增1,并转换到状态T2。试按上述条件画出一个部分ASM图。解:Y和Z具有优先权。129

12.3试分别画出满足下列状态要求的数字系统的ASM图。(1)如果X=0,控制器从状态T1变到状态T2;如果X=1,产生一个条件操作,并从状态T1变到状态T2。(2)如果X=1,控制器从状态T1变到状态T2;然后变到状态T3;如果X=0,控制器从状态T1变到状态T3。(3)在T1状态下,若XY=00,变到状态T2;若XY=01,变到状态T3;若XY=10,变到状态T1;否则变到状态T4。130

(1)如果X=0,控制器从状态T1变到状态T2;如果X=1,产生一个条件操作,并从状态T1变到状态T2。解:131

(2)如果X=1,控制器从状态T1变到状态T2;然后变到状态T3;如果X=0,控制器从状态T1变到状态T3。解:132

(3)在T1状态下,若XY=00,变到状态T2;若XY=01,变到状态T3;若XY=10,变到状态T1;否则变到状态T4。解:133

12.4数字系统的ASM图表示于图P12.4。试用每态一个触发器的方法实现系统控制器。解:D0=T0·W+T2·YD1=T0·W+T3·Y·ZD2=T1·X+T2·Y·Z+T3·YD3=T1·X+T2·Y·Z+T3·Y·Z134

D0=T0·W+T2·YD1=T0·W+T3·Y·ZD2=T1·X+T2·Y·Z+T3·YD3=T1·X+T2·Y·Z+T3·Y·Z135

10.5控制器的状态转移表题图如图P12.5所示,它有4个状态和2个输入端。请完成下列问题:(1)试画出等效的ASM图(状态框是空的);(2)用数据选择器和译码器实现控制器。136

XY=10,为无关项137

建立状态转移表138

139

140

12.6设计一个数字系统,它有3个四位寄存器A、B和C,并实现下0列操作:S1(1)启动信号出现,1传送两个二进制数给AA←X1,B←X2和B;(2)如果AB,右移B0A

您可能关注的文档

- 数字信号处理答案第三版丁玉美.docx

- 数字化学习技术习题册及答案.doc

- 数字图像处理 (许录平 著)课后习题答案 科学出版社.pdf

- 数字图像处理与分析习题及答案.doc

- 数字电子技术基础 阎石第四版课后习题答案详解.pdf

- 数字电子技术基础习题及答案1.pdf

- 数字电子技术基础课后答案 阎石 第五版 第一章第二章 习题答案.pdf

- 数字电子技术第三章习题答案.doc

- 数字电子技术课后习题答案(全部).doc

- 数字电路与逻辑设计课后答案邹红.pdf

- 数字电路习题解答.doc

- 数字电路逻辑设计课后答案.docx

- 数字通信原理课后习题答案.doc

- 数字逻辑习题答案 毛法尧 第二版.doc

- 数字逻辑第四章课后答案.doc

- 数字逻辑设计基础答案 (第1-13章).pdf

- 数字集成电路教程课后答案.pdf

- 数学书籍推荐.docx

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明