- 1.80 MB

- 2022-04-22 11:51:16 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

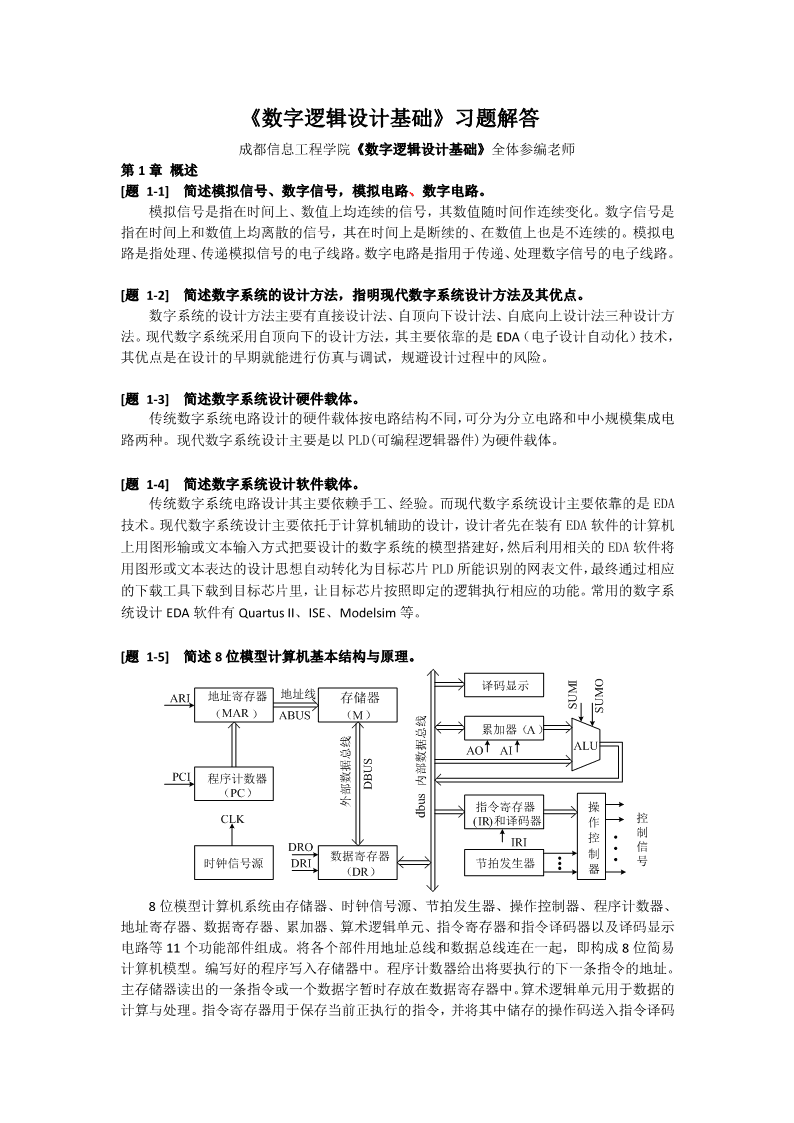

'《数字逻辑设计基础》习题解答成都信息工程学院《数字逻辑设计基础》全体参编老师第1章概述[题1-1]简述模拟信号、数字信号,模拟电路、数字电路。模拟信号是指在时间上、数值上均连续的信号,其数值随时间作连续变化。数字信号是指在时间上和数值上均离散的信号,其在时间上是断续的、在数值上也是不连续的。模拟电路是指处理、传递模拟信号的电子线路。数字电路是指用于传递、处理数字信号的电子线路。[题1-2]简述数字系统的设计方法,指明现代数字系统设计方法及其优点。数字系统的设计方法主要有直接设计法、自顶向下设计法、自底向上设计法三种设计方法。现代数字系统采用自顶向下的设计方法,其主要依靠的是EDA(电子设计自动化)技术,其优点是在设计的早期就能进行仿真与调试,规避设计过程中的风险。[题1-3]简述数字系统设计硬件载体。传统数字系统电路设计的硬件载体按电路结构不同,可分为分立电路和中小规模集成电路两种。现代数字系统设计主要是以PLD(可编程逻辑器件)为硬件载体。[题1-4]简述数字系统设计软件载体。传统数字系统电路设计其主要依赖手工、经验。而现代数字系统设计主要依靠的是EDA技术。现代数字系统设计主要依托于计算机辅助的设计,设计者先在装有EDA软件的计算机上用图形输或文本输入方式把要设计的数字系统的模型搭建好,然后利用相关的EDA软件将用图形或文本表达的设计思想自动转化为目标芯片PLD所能识别的网表文件,最终通过相应的下载工具下载到目标芯片里,让目标芯片按照即定的逻辑执行相应的功能。常用的数字系统设计EDA软件有QuartusII、ISE、Modelsim等。[题1-5]简述8位模型计算机基本结构与原理。译码显示IMOARI地址寄存器地址线存储器UMUSS(MAR)ABUS(M)线累加器(A)总线据AOAIALU总S数据U部PCI程序计数器数B内D(PC)部s外ub指令寄存器操CLKd(IR)和译码器作控制IRI控DRO信数据寄存器制时钟信号源DRI节拍发生器号(DR)器8位模型计算机系统由存储器、时钟信号源、节拍发生器、操作控制器、程序计数器、地址寄存器、数据寄存器、累加器、算术逻辑单元、指令寄存器和指令译码器以及译码显示电路等11个功能部件组成。将各个部件用地址总线和数据总线连在一起,即构成8位简易计算机模型。编写好的程序写入存储器中。程序计数器给出将要执行的下一条指令的地址。主存储器读出的一条指令或一个数据字暂时存放在数据寄存器中。算术逻辑单元用于数据的计算与处理。指令寄存器用于保存当前正执行的指令,并将其中储存的操作码送入指令译码

器中。节拍发生器用于产生节拍脉冲信号。操作控制器按照时间节拍,并根据指令译码器输出的操作要求,向各个功能部件发出有序控制指令。模型计算机原理框图如上图所示。第2章数制和码制[题2-1]将下列十进制数转换成二进制数(1)(357)10(2)(54.369)10(3)(0.954)10(4)(54)10解:十进制数转换成二进制数时,整数部分和小数部分需要分别进行转换。其中,整数部分除10取余法,逆序排列。小数部分乘10取整法,顺序排列。(小数取5位)(1)(357)10=(101110111)2(2)(54.369)10=(110110.01011)2(3)(0.954)10=(0.11110)2(4)(54)10=(110110)2[题2-2]将下列二进制数转换成十进制数(1)(101000)2(2)(11001.01)2(3)(0.10011)2(4)(101.11)2解:二进制数转换成十进制数的方法为:将被转换的数按权展开,再按十进制的运算规律累加。53(1)(101000)2=1×2+1×2=(40)10430-2(2)(11001.01)2=1×2+1×2+1×2+1×2=(25.25)10-1-4-5(3)(0.10011)2=1×2+1×2+1×2=(0.59475)1020-1-2(4)(101.11)2=1×2+1×2+1×2+1×2=(5.75)10[题2-3]将下列二进制数转换成八进制数和十六进制数(1)(1010001101)2(2)(110110001.11001)2(3)(0.11100011)2(4)(1001101.110011)2解:将二进制数转换为八进制或十六进制的方法是:以小数点为中心,分别向左、右按3位一组转换为八进制,或按4位一组转换为十六进制,最后不满3位或4位的需补0组成,将每组以对应等值的八进制数或十六进制数代替。(1)(1010001101)2=(1215)8=(28D)16(2)(110110001.11001)2=(661.62)8=(1B1.C8)16(3)(0.11100011)2=(0.706)8=(0.E3)16(4)(1001101.110011)2=(115.63)8=(4D.CC)16[题2-4]将下列十六进制数转换成二进制数、八进制数和十进制数(1)(4E8.3)16(2)(AB4.0C1)16(3)(0.CD2)16(4)(AF1.D1)16解:(1)(4E8.3)16=(10011101000.0011)2=(2350.14)8=(1256.1875)10(2)(AB4.0C1)16=(101010110100.000011000001)2=(5264.03401)8=(2740.004147690625)10(3)(0.CD2)16=(0.110011010010)2=(0.6322)8=(0.80126953125)10(4)(AF1.D1)16=(101011110001.11010001)2=(4361.642)8=(2289.81640625)10

[题2-5]将下列二进制数转换成八进制数和十进制数(1)(10110100101)2(2)(100110101.10101)2(3)(0.101110011)2(4)(1011001.101011)2解:(1)(10110100101)2=(5515)8=(2893)10(2)(100110101.10101)2=(465.52)8=(309.65625)10(3)(0.101110011)2=(0.563)8=(0.65625)10(4)(1011001.101011)2=(131.53)8=(89.671875)10[题2-6]将下列十进制数转换成8421BCD码、5211BCD码和余三BCD码(1)(76)10(2)(167.358)10(3)(0.912)10(4)(64.51)10解:(1)(76)10=(1110110)8421BCD=(11001001)5211BCD=(10101001)余三BCD(2)(167.358)10=(101100111.001101011000)8421BCD=(110101011.010110001101)5211BCD=(010010011010.011010001011)余三BCD(3)(0.912)10=(0.100100010010)8421BCD=(0.111100100100)5211BCD=(0.110001000101)余三BCD(4)(64.51)10=(01100100.01010001)8421BCD=(10100111.10000010)5211BCD=(10010111.10000100)余三BCD[题2-7]将下列8421BCD码、5211BCD码和余三BCD码转换成十进制数(1)(10010100.001)8421BCD(2)(100110100.01101)5421BCD(3)(10110001010.1011)5211BCD(4)(10110100.101)余三BCD解:(1)(10010100.001)8421BCD=(94.2)10(2)(100110100.01101)5421BCD=(134.65)10(3)(10110001010.1011)5211BCD=(356.7)10(4)(10110100.101)余三BCD=(81.2)10[题2-8]写出下列各数的原码、反码和补码(1)(0.110101)2(2)(0.0000)2(3)(-10110)2解:原码的编码规律可概括为:正数的符号位用0表示,负数的符号位用1表示,数位部分则和真值完全一样。反码又称为“对1的补数”,对于正数,反码和原码相同,对于负数,是将原码数位部分按位求反。补码的表示:正数的补码与原码相同,负数的补码符号位为1,数值位是将原码按位取反后末位加1。(以8位二进制数为基准进行表示)

(1)(0.110101)2→(0.1101010)原→(0.1101010)反→(0.1101010)补(2)(0.0000)2→(0.0000000)原→(0.0000000)反→(0.0000000)补(3)(-10110)2→(10010110)原→(11101001)反→(11101010)补第3章逻辑代数基础[题3-1]分别指出变量(A,B,C,D)在何种取值组合时,下列函数的值为1。(1)YABCCD(2)Y(ABD)(ACD)解:(1)要使函数的值为1,当且仅当ABC取101,D可取0或1;当且仅当CD取11,AB可取00、01、10、11。即ABCD对应取值组合有1010、1011、0011、0111、1111时,函数的值为1。(2)对于或与式,可先求函数的值为0的组合。当且仅当ABD取100,C可取0或1;当且仅当ACD取001,B可取0或1。即ABCD对应取值组合有1000、1010、0001、0101时,函数的值为0。则函数的值为1的ABCD对应取值组合有0000、0010、0011、0100、0110、0111、1001、1011、1100、1101、1110、1111。[题3-2]试用真值表验证下列表达式:(1)ABBCABBC(2)ABAB(AB)(AB)(3)(AB)CACBC(4)ABAB1解:(1)将等式左边和右边对应列出真值表,如表题3.2(1)所示。则ABBCABBC的恒等关系得以证明。表题3.2(1)ABCABBCABBC0001100100010110111110011101001100011100(2)将等式左边和右边对应列出真值表,如表题3.2(2)所示。则

ABAB(AB)(AB)的恒等关系得以证明。表题3.2(2)ABABAB(AB)(AB)0000011110111100(3)将等式左边和右边对应列出真值表,如表题3.2(3)所示。则(AB)CACBC的恒等关系得以证明。表题3.2(3)ABC(AB)CACBC0000000100010000111110000101111100011100(4)将等式左边和右边对应列出真值表,如表题3.2(4)所示。则ABAB1的恒等关系得以证明。表题3.2(4)ABABAB10011010010001111[题3-3]用逻辑代数的基本公式和定律将下列逻辑函数式化简为最简与或表示式:(1)YABCBCC(2)Y(ACACB)BC

(3)YABACADBCBDBCE(4)YABAB(ABAB)AB(5)YA(BC)BCADBDEBCD(6)YACABCBCACABBCDE(7)Y(AB)CDACDAC(AD)(8)Y(ABD)(CE)(ABDCE)解:(1)YABCBCCBC(AB1)CBCCBC(2)Y(ACACB)BCABCBC(ABB)C(AB)CACBC(3)YABACADBCBDBCEABACADBDBC(1E)ABACADBDBC(ABBCAC)(ABAD)BDABBCADBDBDABBC(ABB)DABBCD

(4)YABAB(ABAB)ABABAB(ABAB)AB(AB)(AB)(ABAB)AB(ABAB)(ABAB)ABABABABA(BB)B(AA)AB(5)YA(BC)BCADBDEBCD(ABCBC)ADBDEBCDABCADBDEBCD(AAD)BDEBC(1D)ADBDEBCAD(1BE)BCADBC(6)YACABCBCACABBCDEC(AABB)ACABBCDEC(ABB)ACABBCDEC(A1)ACABBCDECACABBCDECAABBCDECABBCDEABC(7)Y(AB)CDACDAC(AD)(ABA)CDACD

CDACDCD(1A)CD(8)Y(ABD)(CE)(ABDCE)(ABD)(CE)(ABD)(CE)(ABD)(CE)(ABD)(CE)(ABDABD)(CE)CECE[题3-4]证明下列恒等式(证明方法不限):(1)ABACBCDCEABC(2)ABCABCABCAABC(3)ABCABCABBCAC(4)ABCABCABCABCABC证明:(1)ABACBCDCEABC左边ABACBCDCEABACBCBCDCEABACCDCEABC(A1DE)ABC右边结果与等式右边相等,证毕。(2)ABCABCABCAABC左边ABCABCABC

AB(CC)AC(BB)ABAC右边AABCA(ABC)ABAC左边结果等式左边与边相等,证毕。(3)ABCABCABBCAC右边ABBCAC(AB)(BC)(AC)(AB)(ABACBC)ABCABC左边结果与等式左边相等,证毕。(4)ABCABCABCABCABC右边A(BCBC)A(BCBC)A(BCBC)A(BCBC)ABCABCABCABC左边结果与等式左边相等,证毕。[题3-5]根据反演规则求出下列逻辑函数的反函数:(1)YAB(CD)C(2)YABCDABCD(3)YABBCAC(ABC)(4)YABAB(ABAB)AB解:(1)YAB(CD)C

Y(ABCD)C(2)YABCDABCDYAB(CD)(AB)CD(3)YABBCAC(ABC)Y(AB)(BC)(AC)ABC(4)YABAB(ABAB)ABY(AB)(AB)(AB)(AB)(AB)[题3-6]根据对偶规则求出下列逻辑函数的对偶函数:(1)YAC(BD)AC(2)YABCDABCD(3)Y(AB)(ABC)(CD)(ABD)(4)YABABABAC解:(1)YAC(BD)ACY(ACBD)(AC)(2)YABCDABCDYAB(CD)(AB)CD(3)Y(AB)(ABC)(CD)(ABD)YABABCCDABD(4)YABABABACYAB(AB)(AB)(AC)[题3-7]将下列逻辑函数表示成“最小项之和”形式及“最大项之积”形式:(1)F(A,B,C)ABACBC

(2)F(A,B,C)(AC)ACBC(3)F(A,B,C,D)ABCDABCABBCBD(4)F(A,B,C,D)A(BC)解:(1)F(A,B,C)ABACBCAB(CC)AC(BB)BC(AA)ABCABCABCABCABCABCABCABCABCABCm(1,3,6,7)直接由“最小项之和”形式得出“最大项之积”形式F(A,B,C)ABACBC(ABC)(ABC)(ABC)(ABC)M(0,2,4,5)(2)F(A,B,C)(AC)ACBC(AC)(AC)(BC)(ACAC)(BC)ABCABCACABCABCAC(BB)ABCABCABCABCABCABCABCm(3,4,6)直接由“最小项之和”形式得出“最大项之积”形式F(A,B,C)(AC)ACBC(ABC)(ABC)(ABC)(ABC)(ABC)M(0,1,2,5,7)

(3)F(A,B,C,D)ABCDABCABBCBDABBCBD先进行适当简化AB(CC)(DD)BC(AA)(DD)BD(AA)(CC)AB(CDCDCDCD)BC(ADADADAD)BD(ACACACAC)ABCDABCDABCDABCDABCDABCDABCDm(4,6,7,12,13,14,15)直接由“最小项之和”形式得出“最大项之积”形式F(A,B,C,D)ABCDABCABBCBD(ABCD)(ABCD)(ABCD)(ABCD)(ABCD)(ABCD)(ABCD)(ABCD)(ABCD)M(0,1,2,3,5,8,9,10,11)(4)F(A,B,C,D)A(BC)ABCA(BB)(CC)(DD)BC(AA)(DD)A(BCDBCDBCDBCDBCDBCDBCDBCD)BC(ADADADAD)ABCDABCDABCDABCDABCDABCDABCDABCDABCDABCD)m(2,3,8,9,10,11,12,13,14,15)直接由“最小项之和”形式得出“最大项之积”形式F(A,B,C,D)A(BC)(ABCD)(ABCD)(ABCD)(ABCD)(ABCD)(ABCD)M(0,1,4,5,6,7)[题3-8]用卡诺图化简将下列逻辑函数为最简与或表示式:(1)YABACBCBC

(2)YABACDACBC(3)YABADBDBCDABCD(4)YACDBCDBCDABAD(5)YACDCD(AB)AC(CD)(6)F(A,B,C)m(0,1,5,7)(7)F(A,B,C,D)m(0,1,2,3,5,7,8,10,13,15)(8)F(A,B,C,D)m(1,6,8,9,11,12)d(0,2,3,13,14,15)(9)F(A,B,C,D)m(0,3,4,9,10,12,13)d(1,2,6,7,8,11,14)YABCDACDABCCD(10)BCDAC0解:(1)YABACBCBC由逻辑表达式作卡诺图,如图题3.8(1)所示。由卡诺图得最简与或表达式YBACCDAB00011110BC001111A000111100001101010010111110011100011图题3.8(1)图题3.8(2)(2)YABACDACBC由逻辑表达式作卡诺图,如图题3.8(2)所示。由卡诺图得最简与或表达式YABACDAC(3)YABADBDBCDABCD

由逻辑表达式作卡诺图,如图题3.8(3)所示。由卡诺图得最简与或表达式YBCBDABCDCDAB00011110AB00011110000000000110011110010110111110110111101111101111图题3.8(3)图题3.8(4)(4)YACDBCDBCDABAD由逻辑表达式作卡诺图,如图题3.8(4)所示。由卡诺图得最简与或表达式YDACAB(5)YACDCD(AB)AC(CD)方法一:先将逻辑函数变换为与或表达式,再用卡诺图化简。YACDCD(AB)AC(CD)ACDCD(AB)AC(CD)(ACD)(CDAB)(ACCD)(ACADCCDABCDABD)(ACCD)ACADACDACDCCDABCCDABCDABCD由逻辑表达式作卡诺图,如图题3.8(5a)所示。由卡诺图得最简与或表达式YCD方法二:先作反函数YACDCD(AB)AC(CD)的卡诺图,如图题3.8(5b)所示;然后将图题3.8(5b)卡诺图中的“0”变为“1”,“1”变为“0”,即得到原函数YACDCD(AB)AC(CD)的卡诺图,如图题3.8(5a)所示。

CDCDAB00011110AB00011110001101000010011101010010111101110010101101100010图题3.8(5a)图题3.8(5b)由卡诺图得最简与或表达式YCD实际上,直接在反函数的卡诺图中圈“0”,即可得到原函数的最简与或表达式。两种方法,结果相同,但方法二比方法一要简单。(6)F(A,B,C)m(0,1,5,7)由标准与或表达式作卡诺图,如图题3.8(6)所示。由卡诺图得最简与或表达式F(A,B,C)ABACCDAB00011110BC001111A000111100110001011010110110110101001图题3.8(6)图题3.8(7)(7)F(A,B,C,D)m(0,1,2,3,5,7,8,10,13,15)由标准与或表达式作卡诺图,如图题3.8(7)所示。由卡诺图得最简与或表达式F(A,B,C,D)ABBDBD(8)F(A,B,C,D)m(1,6,8,9,11,12)d(0,2,3,13,14,15)由标准与或表达式作卡诺图,如图题3.8(8a)所示。圈法一:由卡诺图题3.8(8a)得最简与或表达式

F(A,B,C,D)ACBDBCD圈法二:由卡诺图题3.8(8b)得最简与或表达式F(A,B,C,D)ACBDACDCDCDAB00011110AB0001111000×1××00×1××010001010001111×××111×××101110101110图题3.8(8a)图题3.8(8b)同一题,两种结果,说明逻辑函数的最简与或表达式不是唯一的。(9)F(A,B,C,D)m(0,3,4,9,10,12,13)d(1,2,6,7,8,11,14)由标准与或表达式作卡诺图,如图题3.8(9)所示。由卡诺图得最简与或表达式F(A,B,C,D)BCDACCDCDAB00011110AB00011110001×1×0001100110××0101×011110×1101××10×1×11011××图题3.8(9)图题3.8(10)YABCDACDABCCD(10)BCDAC0由逻辑表达式作卡诺图,如图题3.8(10)所示。由卡诺图得最简与或表达式F(A,B,C,D)DAB[题3-9]用卡诺图化简将下列逻辑函数为最简或与表示式(1)Y(ABCD)(ABD)(ABD)(2)Y(ABC)(ABD)(BCD)(ABCD)

(3)F(A,B,C,D)M(0,1,2,3,8,10)(4)F(A,B,C,D)M(2,3,4,6,7)D(10,11,12,13,14,15)(5)F(A,B,C,D)m(0,1,2,3,4,6,8)d(10,11,12,13,14)解:(1)Y(ABCD)(ABD)(ABD)由逻辑表达式作卡诺图,如图题3.9(1)所示。由卡诺图得最简或与表达式Y(ABCD)(BD)CDCDAB00011110AB00011110000110001011011011011001111111110000100110101111图题3.9(1)图题3.9(2)(2)Y(ABC)(ABD)(BCD)(ABCD)由逻辑表达式作卡诺图,如图题3.9(2)所示。由卡诺图得最简或与表达式Y(AB)(BD)(ACD)(3)F(A,B,C,D)M(0,1,2,3,8,10)由逻辑表达式作卡诺图,如图题3.9(3)所示。由卡诺图得最简或与表达式F(A,B,C,D)(AB)(BD)CDCDAB00011110AB00011110000000001×0001111101010011111111××××1001101011××图题3.9(3)图题3.9(4)

(4)F(A,B,C,D)M(2,3,4,6,7)D(10,11,12,13,14,15)由逻辑表达式作卡诺图,如图题3.9(4)所示。由卡诺图得最简或与表达式F(A,B,C,D)(AC)(BD)(5)F(A,B,C,D)m(0,1,2,3,4,6,8)d(10,11,12,13,14)由逻辑表达式作卡诺图,如图题3.9(5)所示。由卡诺图得最简或与表达式F(A,B,C,D)(AD)(BD)CDAB0001111000111101100111××0×1010××图题3.9(5)[题3-10]用卡诺图判别逻辑函数Y和Z之间的关系:(1)YABACBCZABACBC(2)Y(ABC)(ABCD)ZABCD解:(1)YABACBCZABACBC由逻辑表达式分别作Y和Z的卡诺图,如图题3.10(1a)和图题3.10(1b)所示。BCBCA00011110A0001111000001011101011111000图题3.10(1a)图题3.10(1b)由两卡诺图中对应小方格满足“0”变为“1”,“1”变为“0”的关系,得逻辑函数Y和Z之间的互为反函数关系。

(2)Y(ABC)(ABCD)ZABCD由逻辑表达式Y(ABC)(ABCD)ABABCDBCDABCCD和ZABCD分别作卡诺图,如图题3.10(2a)和图题3.10(2b)所示。CDCDAB00011110AB00011110000010000010010010010010111111111111100010100010图题3.10(1a)图题3.10(2b)由两卡诺图中对应小方格完全相同,,得逻辑函数Y和Z之间的为恒等关系。[题3-11]已知下列逻辑函数,试用卡诺图分别求出YY、YY和YY:121212YABCABCABC1(1)YABCABCABCABC2YACDACDABDBCD1(2)YABCBCCD2解:YABCABCABC1(1)YABCABCABCABC2由逻辑表达式分别作Y1和Y2卡诺图,如图题3.11(1a)和图题3.11(1b)所示。BCBCA00011110A0001111001110010001000011110图题3.11(1a)图题3.11(1b)由卡诺图得逻辑表达式YYABCABCABCABCABCABC12YYABC12

YYABCABCABCABCABC12YACDACDABDBCD1(2)YABCBCCD2由逻辑表达式分别作Y、Y和Y卡诺图,如图题3.11(1a)、图题3.11(1b)和图题1223.11(1c)所示。CDCDCDAB00011110AB00011110AB00011110000010001000000111011011011011010100110110111011110100100110101000100111图题3.11(2a)图题3.11(2b)图题3.11(2c)由卡诺图得逻辑表达式YYABCDABCDABCDABCDABCDABCD12ABCDABCDABCDABCDABCDABCDYYABCDABCDABCDABCD12YYABCDABCDABCDABCDABCDABCD12ABCDABCD[题3-12]列出以下各题的真值表,并写出逻辑函数的标准与或式:(1)某四变量逻辑函数,其中变量A、B、C、D为表示1位十进制数X的8421BCD码,当X为奇数时,逻辑函数Y为0;否则Y为1。(2)X为输入变量,Y为输出函数。X输入为4位二进制数,Y输出也为4位二进制数。当X<8时,Y=X+1;当X≥8时,Y=X-1。解:(1)设变量A、B、C、D为表示1位十进制数X的8421BCD码。根据题意,列出真值表,如表题3.12(1)所示。由真值表得标准与或表达式YABCDABCDABCDABCDABCDABCDABCDABCDABCDABCDABCD0或Y(A,B,C,D)m(0,2,4,6,8)d(10,11,12,13,14,15)

表题3.12真值表XABCDY0000011000102001013001104010015010106011017011108100019100101010×无1011×效1100×码1101×1110×1111×(2)设十进制数变量X对应的四位二进制数变量为X3X2X1X0,十进制数输出Y对应的四位二进制数输出为Y3Y2Y1Y0。根据题意,列出真值表,如表题3.12(2)所示。由真值表得标准与或表达式Y3(X3,X2,X1,X0)m(7,9,10,11,12,13,14)Y2(X3,X2,X1,X0)m(3,4,5,6,8,13,15)Y1(X3,X2,X1,X0)m(1,2,5,6,8,11,12,14,15)Y0(X3,X2,X1,X0)m(0,2,4,6,8,10,12,14,15)表题3.13真值表XYX3X2X1X0Y3Y2Y1Y0000000010001001000100011001101000100010101010110

01100111011110001000011110011000101010011011101011001011110111001110101111110111A[题3-13]给出逻辑图P3-1的逻辑函数表达式,并列=1=1Y1B出真值表。解:&CY2(1)直接根据逻辑图P3-1得出逻辑函数表达式&&YABC1YAB(AB)C题3.13图P3-12根据逻辑函数列出真值表,如表题3.13所示。表题3.2(3)ABCY1Y20000000110010100110110010101011100111111第4章VHDL[题4-1]试述VHDL程序中实体和结构体的相互关系。实体和结构体的作用都是用于描述设计对象。其不同点在于,实体用于描述该设计对象与外部电路的接口。结构体用于描述设计对象的内部结构、具体实现以及实体端口间的逻辑关系。

[题4-2]函数和过程的作用是什么?有什么区别?函数和过程都是子程序的一种类型,子程序可以在结构体或程序包的任何位置被调用,便于代码的复用,增强代码可读性。过程的参数表有输入参数、输出参数和双向参数,过程被调用时是作为一种语句而单独存在,过程调用后可以有多个返回值;函数参数表仅定义输入参数,函数是作为表达式的一部分被调用,函数调用后只有一个返回值。[题4-3]试说明条件信号赋值语句与IF语句的异同。条件信号赋值语句中无标点,只有最后有分号,必须放在结构体中,是并行语句。IF语句中有分号,必须放在进程中,是顺序语句。[题4-4]试说明选择信号赋值语句与CASE语句的异同。选择信号赋值语句中间是逗号,最后是分号,必须放在结构体中,是并行语句。CASE语句中间是分号,必须放在进程中是,顺序语句。[题4-5]在VHDL中有几种数据对象?分别是什么?VHDL中有三种数据对象,分别是常量(Constant)、变量(Variable)、信号量(Signal)。[题4-6]顺序语句和并行语句的主要区别是什么?顺序语句是主要用于行为描述的,只能出现在进程(Process)和子程序中,其执行方式与书写的顺序有关。并行语句是主要用于数据流描述或者结构描述的,各种并行语句在结构体中的执行是同步进行的,其执行方式与书写的顺序无关。[题4-7]元件例化的作用是什么?元件例化就是将预先设计好的设计对象定义为一个元件,然后利用特定的语句(元件例化语句)将此元件与当前的设计对象中的指定端口连接,从而为当前设计对象引入一个新的低一级的设计层次。[题4-8]用元件例化的方式设计一个三输入与门?ENTITYgate2andisport(in1,in2:INSTD_LOGIC;out1:OUTSTD_LOGIC);ENDgate2and;ARCHITECTUREdataflowOFgate2andISBEGINout1<=in1ANDin2;ENDdataflow

将该VHDL文件以gate2and.vhd命名,放在文件夹gate下,并作为gate工程的底层文件。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYgate3andISPORT(a,b,c:INSTD_LOGIC;y:OUTSTD_LOGIC);ENDgate3and;ARCHITECTUREstructureOFgate3andISCOMPONENTgate2andPORT(in1,in2:INSTD_LOGIC;out1:OUTSTD_LOGIC);ENDCOMPONENTgate2and;SIGNALs:STD_LOGIC;BEGINu1:gate2andPORTMAP(a,b,s);u2:gate2andPORTMAP(s,c,y);ENDstructure;将该VHDL文件以gate3and.vhd命名,放在文件夹gate下,并作为gate工程的顶层文件。[题4-9]试比较C语言和VHDL语言的区别。VHDL是硬件描述语言,主要用于描述数字系统的结构、行为、功能和接口,用来组建硬件内部结构连接的。C语言是软件语言,主要用于控制CPU进行各种运算。前者是并行的,后者是顺序执行的。VHDL编译后生成的网表文件写入FPGA后,会改变FPGA内部实际电路硬件连接结构。C语言编译后生成的可执行文件写入存储器中,能指定CPU进行的具体操作,但是不会对CPU内部硬件电路连接结构造成变化(假设C语言编写的程序在通用计算机或嵌入式MCU上运行,VHDL描述的电路最终映射到FPGA)。[题4-10]试设计一个具有高电平使能控制的2线-4线译码器。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYdecoder2_4ISPORT(inp:INSTD_LOGIC_VECTOR(1DOWNTO0);en:INSTD_LOGIC;outp:OUTSTD_LOGIC_VECTOR(3DOWNTO0));ENDdecoder2_4;ARCHITECTUREBehavioralOFdecoder2_4ISBEGINPROCESS(en,inp)BEGINIF(en="1")THENCASEinpISWHEN"00"=>outp<="0001";

WHEN"01"=>outp<="0010";WHEN"10"=>outp<="0100";WHEN"11"=>outp<="1000";WHENOTHERS=>outp<="ZZZZ";ENDCASE;ELSEoutp<="0000";ENDIF;ENDPROCESS;EndBehavioral;[题4-11]试画出下面实体描述的视图符号entityhtisport(en:inbit;a:instd_logic_vector(2downto0);d:instd_logic_vector(7downto0);y:outstd_logic);endentityht;enyahtd图中en,a,d均为输入端口,y为输出端口。[题4-12]试设计一个JK边沿触发器。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYjkffISPORT(clk:INSTD_LOGIC;rst:INSTD_LOGIC;J,k:INSTD_LOGIC;q:OUTSTD_LOGIC);ENDjkff;ARCHITECTUREaOFjkffISSIGNALiq:STD_LOGIC;BEGINPROCESS(clk,rst)BEGINIF(rst="1")THEN

iq<="0";ELSIF(rising_edge(clk))THENIF((j="1")and(k="1"))THENiq<=notiq;ELSIF((j="1")and(k=’0’))THENiq<="1";ELSIF((j="0")and(k=’1’))THENiq<="0";ELSEiq<=iq;ENDIF;ENDIF;ENDPROCESS;q<=iq;ENDa;[题4-13]试写出一位全加器的VHDL程序,其结构体用行为描述法写。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALLENTITYfull_adderISPORT(x,y,cin:INSTD_LOGIC;sum,cout:OUTSTD_LOGIC);ENDfull_adder;ARCHITECTUREbehave_adderOFfull_adderISBEGINPROCESS(x,y,cin)BEGINIF(xORyORcin)=’0’THENsum<=‘0’;cout<=‘0’;ELSIF(xANDyANDcin)=’1’THENsum<=‘1’;cout<=‘1’;ELSIF(xXORyXORcin)=’0’THENsum<=‘0’;

cout<=‘1’;ELSEsum<=‘1’;cout<=‘0’;ENDIF;ENDPROCESS;ENDbehave_adder;第5章逻辑门电路[题5-1]TTL门电路的电压传输特性曲线上可以反映出数字电路的哪些主要技术参数?解:门电路的电压传输特性曲线描述了逻辑门在空载条件下的输出电压和输入电压之间的对应关系,曲线上可以反映出数字电路的标准高低逻辑电平值VH和VL,关门电平VOFF、开门电平VON和阈值电压VT,输入信号噪声容限VNL和VNH。[题5-2]如图P5-1(a)~(f)所示的各TTL门电路,关门电阻ROFF为750Ω,开门电阻RON为3.3kΩ,试判断出哪些门电路可正常工作,哪些不能正常工作,并写出可正常工作门电路的输出逻辑表达式。470ΩAYaAYbAYcBBB&430Ω3.9KΩ470Ω(a)(b)(c)AYd悬空AYeYfB&AB&B270Ω3.9KΩ(d)(e)(f)图P5-1[题5-2](a)-(f)图解:将低电平输入的最大电阻称为关门电阻ROFF,相当于TTL门电路输入端接低电平;输入端电阻R小于关门电阻ROFF时,将输入高电平的最小电阻称为开门电阻RON。若TTL门的输入端电阻R大于开门电阻RON,相当于该输入端为高电平。本题中关门电阻ROFF为750Ω,开门电阻RON为3.3kΩ,所以,只有(a)(d)(f)可正常工作,其表式如下:YABABABaYABdYABABf[题5-3]如果将TTL逻辑门电路的输出采用下列接法会产生什么样的结果,试说明原因?(1)输出直接接地;(2)输出端直接接电源VCC=+5V;(3)多个输出端并接一起;

解:(1)如果将TTL逻辑门输出直接接地,在输出高电平时会烧坏逻辑门输出级的拉电路部分。(2)如果将TTL逻辑门输出直接接VCC=+5V,在输出低电平时会烧坏逻辑门输出级的推电路部分。(3)如果多个TTL逻辑门输出端并接一起,当一个门的输出为高电平而另一个门的输出为低电平时,在电源和地之间形成一个低阻通路,产生一个很大电流IHL,会使导通门输出低电平升高,破坏了电路原有的逻辑关系,因功耗过大损坏截止门中的导通管T4,造成逻辑门损坏。所以,推拉结构的TTL门电路输出端是不允许直接连在一起使用。[题5-4]为什么TTL集成逻辑电路的输入端悬空相当于输入高电平,TTL集成或非门如有多余输入端,能否与其它输入端并接使用?能否接电源VCC或悬空?为什么?解:TTL集成逻辑电路的输入端悬空相当于输入高电平,因为悬空等同在其输入端按入了一个无穷大电阻,远超过它的开门电阻。TTL或非门多余输入端可以与其它输入端并接使用,如多余的输入端接电源VCC或悬空,其逻辑值为1,而或非门逻辑功能为有1出0,封锁了该逻辑门,所以,或非门多余的输入端不允许接电源VCC或悬空。[题5-5]OC门、三态门各有什么特点?它们各有什么用途?解:OC门是开路门,使用时需在输出端外接负载电阻和电源,其主要用途是实现线与、电平转换和驱动大电流载。三态门的输出状态有0、1和高阻三种取值,主要应用为构成单双向的总线传输。[题5-6]下列各种门电路的输出端是否可以并接使用(输入端的状态不一定相同)?如果可以并接,试说明并接的功能。(1)推拉输出TTL电路;(2)TTL电路的OC门和CMOS电路的OD门;(3)TTL和CMOS电路的三态门;解:(1)推拉输出TTL电路的输出端是不能并联使用的,如果并接使用,当一个门的输出高电平而另一个门的输出为低电平时,这样,破坏了电路原有的逻辑关系,还因功耗过大造成逻辑门损坏。(2)TTL电路OC门和CMOS电路OD门的输出端可以并接使用,可以实现线与、电平转换和驱动大电流负载。(3)TTL和CMOS电路的三态门,其输出端可以并接使用,可以实现单向或双向总线数据传输。[题5-7]指出如图P5-2所示TTL门电路输出与输入之间的逻辑关系,哪些是正确的?哪些是错误的?并将接法错误进行改正。

AAAB&YaBYbB&YcVcc悬空Ya=ABYb=A+BYa=AB(a)(b)(c)AAB&BYd悬空YeCDYe=AB+CDYb=A+B(d)(e)图P5-2[题5-7](a)-(e)图解:(c)(d)可正常工作,其表式如下:YABcYABd(a)(b)(e)多余输入端处理不正确,所以,不能正常工作。改正如下:(a)多余输入端接高电平或与其它输入并接使用,(b)多余输入端接低电平,(e)多余输入端都接高电平或与其它输入端并接。[题5-8]如图P5-3所示的TTL电路中,哪些能实现YABA悬&=1B空YaYbA1B1(b)(a)VccRA1YdA&YcB1B&(c)(d)图P5-3[题5-8](a)-(d)解:只有(b)(c)能实现YAB逻辑运算,其表式如下:YABABABABbYcABAB[题5-9]采用集电极开路OC门驱动LED发光二极管,电路如图P5-4所示,发光二极管工作电流IF为20mA,导通电压VP=2.2V。试求

+5VRA1图P5-4(1)当OC门输入低电平时,其门电路输出电压为多少?(2)为了保证发光二极管正常工作,限流电阻R应取值多少?解:(1)OC门输入低电平时,集电极开路的非门其输出级为关闭状态,所以OC门此时输出电压为5V。(2)只有在OC门输入高电平时,使OC门输出为低电平时,LED才导通发光;否则LED中无电流流通,不发光。为保证电路正常工作,R应满足:5VV0.3V5V2.2V0.3VPR125I20mAF限流电阻R应取值为125[题5-10]比较TTL和CMOS逻辑电路各有什么优缺点?解:数字集成电路按晶体管的性质分为TTL和CMOS两大类,TTL电路是电流控制器件,其电路的工作速度快,传输延迟时间短(5-10ns),但是功耗大。CMOS电路为电压控制器件,以功耗低而著称,尤以其优良的特性成为目前应用最广泛的集成电路,但电路的工作速度慢。传输延迟时间长(25-50ns),COMS电路本身的功耗还与输入信号脉冲频率有关,频率越高,芯片集越热,CMOS的噪声容限比TTL大,抗干扰能力更强。COMS电路的具有锁定效应:当由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。这种效应就是锁定效应。当产生锁定效应时,COMS的内部电流能达到40mA以上,很容易烧毁芯片。[题5-11]试说明CMOS逻辑电路输入端不能悬空?解:CMOS逻辑电路的输入端不允许悬空,因为输入阻抗高,易受外界噪声干扰,悬空会使电位不定,破坏正常的逻辑关系,使电路产生误动作,也容易造成栅极感应静电而击穿器件。[题5-12]分析如图P5-5所示电路的逻辑功能,并写输出逻辑表达式。VDDVDDT2T2A&FaENAFbTGT1T1T0EN1(a)(b)图P5-5

解:(1)(a)为三态结构的CMOS缓冲门,使能端高电路有效,逻辑表达式为:FAa(2)(b)为三态结构的CMOS非门,使能端高电路有效,逻辑表达式为:FAa第6章组合逻辑电路[题6-1]试分析图P6-1所示电路的逻辑功能。A&&F11&B解:(a)FABBAABABABA=B可见电路(a)实现同或的逻辑功能。S0S1S2S3=1=1=1=1BA0A1A2A3解:有图分析可知,(b)电路是一个原码/反码的发生器,当B0时SA为原码输出。当B1时SA为反码输出。[题6-2]试分析图P6-2所示电路的逻辑功能。A=1=1BY0C&Y1&&解:(1)由电路写出逻辑表达式YABC0YABCA()B1(2)由逻辑表达式列出真值表输入输出ABCSC0000000110010100110110010101011100111111可见电路为一位的二进制全加器,其中A和B为两个加数,C为低位到本位的进位输

入,Y和Y分别为本位和数及向高位进位。01[题6-3]写出图P6-3所示电路的逻辑表达式,并化简为最简与或表达式。CA0Y0&F1BA1Y1AA2Y2Y3&F2Y41STAY5STBY6&F3STCY7解:根据电路图可以写出表达式FYYYmmmmmm1067067067ABCABCABC+ABCABFYYYYmmmmmmmm2124712471247ABCABCABCABCABCABCFYYYmmmmmm3157157157ABCABCABCACBC[题6-4]写出图P6-4所示电路的逻辑表达式,并化简为最简与或表达式。BA0AA11ST1YF11D0C11D11D21D32ST2YF2D202D12D212D3解:该电路是由8选1数据选择器74LS151构成的组合逻辑电路。(1)分析图示电路,得到8选1数据选择器数据输入端数据1D2D2DC0121DD20101DC21DD2133(2)写出双4选1数据选择器输出逻辑表达式1YAAD1AAD1AAD1AAD11001011021032YAA2DAA2DAA2DAA2D100101102103(3)令AAB,A,将数据带入双4选1数据选择器输出逻辑表达式可得:10F1YABCABCABABCACAB1F2YABCABCABACABBC2

[题6-5]写出图P6-5所示电路的逻辑表达式。D0D1D1D2F=YD3D4D5D6D7STYAA2BA1CA0解:该电路是由8选1数据选择器74LS151构成的组合逻辑电路。(1)分析图示电路,得到8选1数据选择器数据输入端数据DDDDD0156DDDDD2347(2)写出8选1数据选择器输出逻辑表达式YAAADAAADAAADAAAD2100210121022103AAADAAADAAADAAAD2104210521062107(3)令AA,,BACA,将数据带入8选1数据选择器输出逻辑表达式可得:210FYABCDABCDABCDABCDABCDABCDABCDABCDmmmmm+++mmm02579101215[题6-6]在只有原变量输入条件下,用最少的与非门实现以下函数。解:FABCABCABCABC=ABCABACABC+=ABCBCABCAABCBCABCAABC由上式可画出逻辑图A&&&FC&B[题6-7]采用扩展法,用两片2-4线译码器和门电路实现以下函数,写出设计全过程,并画出电路图。FABC..ABCABCABCmmmmmmmm112471247解FABCABCABCmmmmmm2356356

F1F2&&Y0Y1Y2Y3Y4Y5Y6Y7Y0Y1Y2Y3Y0Y1Y2Y3(1)(2)ST1A1A0ST2A1A01A2A1A0[题6-8]试用3线-8线的译码器74LS138和与非门实现下列逻辑函数,画出逻辑电路图。FACACABC1FACBC2解:①将FF、化为最小项之和形式12FACACABCABCABCABCABCABC1mmmmm02346FACBCABCABCABCABC2mmmm2567②令AAA,BA,C,将mm~用译码器的输出Y表示,因此有21007iFmmmmmYYYYY10234602346FmmmmYYYY225672567③根据上式可画出FF、的逻辑电路如图。12CA0Y0BA1Y1&F1AA2Y2Y3Y41STAY5&F2STBY6STCY7[题6-9]试用一片八选一数据选择器及门电路实现下列逻辑函数,分别用代数法和降维图法实现,画出逻辑电路图。FABCD(,,,)m(1,5,6,7,9,11,12,13,14)解(1)用代数法①写出逻辑函数F的最小项表达式FABCDABCDABCDABCDABCDABCDABCDABCDABCDABCDABCDABCABCDABCDABCABCD

②写出74LS151输出逻辑函数Y的表达式YAAADAAADAAADAAAD2100210121022103AAADAAADAAADAAAD2104210521062107mDmDmDmDmDmDmDmD0011223344556677③设AA、BA、CA,且FY。比较F和Y两式中的最小项,若F式中210的最小项为m,则Y式中对应m最小项的数据D1,若F式中没有的最小项为m,iiij则Y式中对应mj最小项的数据Dj0,由此可得DDDDD0245D01DD136DD7○4由式上画出逻辑电路D00D1D2F=Y1D3D4D5D6D1D70STYAA2BA1CA0解:(2)用降维图法①作出F的卡诺图和降维图,把D作为3变量降维图的记图变量。CDAB00011110000100BC010111A00011110111101X=D0D01D1001101DDD1函数卡诺图3变量降维图;②将8选1数据选择器卡诺图与函数降维图比较可得:A1A0A200011110BCA000111100D0D1D3D20D01D1D4D5D7D61DDD1

DDDDD0245D01DD136DD7③由式上画出逻辑电路同代数法。[题6-10]试用一片四选一数据选择器及门电路实现下列逻辑函数,分别用代数法和降维图法实现,画出逻辑电路图.。FABCD(,,,)m(1,5,6,7,9,11,12,13,14)解(1)用代数法①写出逻辑函数F的最小项表达式FABCDABCDABCDABCDABCDABCDABCDABCDABCDABCDABCDCDCD()ABCDCD()ABCDCDCD()ABCDABC(D))ABDABC(D②写出1/274LS153输出逻辑函数Y的表达式YAADAADAADAAD100101102103mDmDmDmD00112233③设AA、BA,且FY。比较F和Y两式中的最小项,若F式中的最小项10为mi,则Y式中对应mi最小项的数据Di1,若F式中没有的最小项为mj,则Y式中对应mj最小项的数据Dj0,由此可得DCDCDDDCDDDDCD0123④由式上画出逻辑电路BA0AA1ST&D0F=YYC1D1DD2&D3解:(2)用降维图法①作出F的卡诺图和降维图,把D和C分别作为3变量降维图和2变量降维图的记图变量。

CDAB00011110000100BCB010111AA0001111001111101X=D0D01DX=C0CDC+D1001101DDD11DC+D②将4选1数据选择器卡诺图与函数降维图比较可得:A0BA10001A010D0D10CDC+D1DC+D1D2D3DCDCDDDCDDDDCD0123③由式上画出逻辑电路同代数法。[题6-11]使用一片四选一数据选择器及门电路实现下列五变量逻辑函数,采用代数法实现,画出逻辑电路图.。解(1)写函数表达式FABDABEABCABDEABC=ABDE()ABC(DE)ABCABDEABCDEABC②写出四选一数据选择器输出逻辑函数Y的表达式YAADAADAADAAD100101102103mDmDmDmD00112233③设AA、BA,且FY。比较F和Y两式中的最小项,若F式中的最小项10为mi,则Y式中对应mi最小项的数据Di1,若F式中没有的最小项为mj,则Y式中对应mj最小项的数据Dj0,由此可得DDEDCDED0DC0123④由式上画出逻辑电路

AA1BA0STCD3F=YYD2&D1D&D0E[题6-12]在ABC、、三个输入信号中,A的优先权最高,B次之,C最低,它们的输出分别用YYY、、表示,要求同一时间内只有一个信号输出。如有两个或三个信号同时输ABC入时,则只有优先权最高的信号输出,使用门电路设计一个能实现此要求的逻辑电路。解:(1)根据题意可列出真值表。真值表ABCY2Y1Y0000000001001010010011010100100101100110100111100(2)由真值表写出最简输出逻辑函数表达式。YABC0YABCABC=AB1YABCABCABCABCA=2(3)画逻辑图。Y2A1&Y1B1&Y0C[题6-14]试用VHDL设计一个半加器,要求采用布尔方程描述方法。解:VHDL描述的半加器libraryieee;useieee.std_logic_1164.all;entityh_adderisport(a,b:instd_logic;so,co:outstd_logic);endh_adder;architecturehaofh_adderisbeginso<=axorb;

co<=aandb;endha;[题6-15]设计一个1位十进制数指示器,输入为8421BCD码,当输入数值大于5时输出为1。要求采用两种方法实现:(1)用逻辑门设计电路;(2)用VHDL设计电路。解(1)用逻辑门设计电路设输入的8421BCD码用ABCD表示,Y为输出。真值表XABCDY0000001000102001003001104010005010106011017011118100019100111010×无1011×效1100×码1101×1110×1111×CDAB0001111000000001001111××××A1B&Y1011××CYABC解(2)用VHDL设计电路libraryieee;useieee.std_logic_1164.all;entityzsqisport(a,b,c,d:instd_logic;y:outstd_logic);endzsq;architecturezs1ofzsqisbeginy<=aor(bandc);endzs1;

第7章集成触发器[题7-1]解:RS触发器有置0、置1和保持三种功能。nn1QSRQdd特性方程为SR1dd特性表如下:nn1SdRdQQ说明000两输入端从0同时变为1后001触发器状态不确定1000触发器置010100101触发器置101111100触发器状态保持不变1111[题7-2]解:输出端Q的波形如下:SdRdQ[题7-3]解:输出端Q的波形如下:CPSRQ[题7-4]JK触发器有置0、置1、翻转和保持四种功能。同步JK触发器的特性表nn1CPJKQQ说明0××Qnn1n×QQ保持10000n1nQQ保持1001110100n1010Q0置01111001n11101Q1置1111101n1nQQ翻转11110

n1nnQJQKQ特性方程为:[题7-5]D触发器有置0、置1两种功能。n1QD特性方程为:同步D触发器的特性表如下所示:nn1CPDQQ说明0××QnCP=0时,无论D为何值,均维持现状10001010CP=1时输出状态和D相同11011111[题7-6]解:高电平有效和上升沿有效D触发器Q的波形分别为Q1,Q2.CPDQ1Q2[题7-7]解:CP1234567RdRdRdA=11DQSdC1QCPSdASdQ[题7-8]解:

CPJKQ[题7-9]解:CPAQ0Q1[题7-10]解:CPQaQbcde[题7-11]解:CPQ0Q1[题7-12]解:libraryieee;useieee.std_logic_1164.all;entitydcfqisport(d,clk,reset:instd_logic;

q:outstd_logic);enddcfq;architectureartofdcfqisbeginprocess(clk)isbeginif(clk"eventandclk=‘0’)thenif(reset=‘0’)thenq<=‘0’;elseq<=d;endif;endif;endprocess;endart;[题7-13]解:libraryieee;useieee.std_logic_1164.all;entitytfqisport(t,clk:instd_logic;q,qb:outstd_logic);endtfq;architectureartoftfqisSIGNALq_temp,qb_temp:std_logic;BEGINPROCESS(clk)BEGINIF(clk’eventANDclk=’1’)THENIF(t=’1’)THENq_temp<=NOTq_temp;qb_temp<=NOTqb_temp;ELSEq_temp<=q_temp;qb_temp<=qb_temp;ENDIF;ENDIF;q<=q_temp;qb<=qb_temp;ENDPROCESS;ENDartt[题7-14]解:libraryieee;useieee.std_logic_1164.all;entityjkffisport(j,k,clk,rd,sd:instd_logic;q,qn:outstd_logic);endjkff;architectureartofjkffis

signalqq:std_logic;beginprocess(clk,j,rd,sd,k)isbeginifsd=‘0’andrd=‘1’thenqq<=‘1’;elsifrd=‘0’andsd=‘1’thenqq<=‘0’;elsif(clk"eventandclk=‘1’)thenif(j=‘0’andk=‘1’)thenqq<=‘0’;elsif(j=‘1’andk=‘0’)thenqq<=‘1’;elsif(j=‘1’andk=‘1’)thenqq<=notqq;endif;endif;q<=qq;qn<=notqq;endprocess;endart;第8章时序逻辑电路[题8-1]试分析图P8-1所示时序逻辑电路的逻辑功能,列出状态转换真值表,画出状态转换图和时序图。图P8-1nn解:输出方程:Y=QQ10驱动方程J=K=001nJ=K=XQ110Qn+1=Qn00状态方程:n+1nnQ=(XQ)Q110题8-1状态转换真值表CP脉冲现态次态输出CP脉冲现态次态输出顺序QnQnQn+1Qn+1Y顺序QnQnQn+1Qn+1Y10101010000010000110101100111101210110210010311001301000

X0=X=1题8-1(a)(b)状态转换图,(c)时序图[题8-2]试分析图P8-2所示电路的逻辑功能。列出状态转换真值表,画出状态转换图和时序图。图P8-2nn解:输出方程:Y=QQ20J=K=001驱动方程nnnJ=QQ1102,K=Q0nnnJ=QQ,K=Q21020Qn+1=Qn00n+1nnnnn状态方程:Q1=QQQ021+QQ01n+1nnnnnQ2=QQQ102+QQ02题8-2状态转换真值表

CP脉冲现态次态输出顺序QnQnQnQn+1Qn+1Qn+1Y210210000000101001010020100110301110004100101151010000Q2Q1Q0/Y/0/0000001010/0/0/1/0101100011题8-2状态转换图[题8-3]试分析图P8-3所示电路的逻辑功能。列出状态转换真值表,画出状态转换图和时序图。图P8-3解:CP=CPn0输出方程Y=Q2时钟方程:nCP==CPQ120J=K=1Qn+1=Qn0000nn+1nnnnnn驱动方程J=Q112,K=1状态方程:Q11=QJ11+K1Q=Q2Q1=Q2+Q1nnn+1nnnnnnnJ=Q21,K=Q21Q2=J2Q2+K2Q2=QQ12+QQ12=Q1题8-3状态转换真值表

CP脉冲现态次态输出时钟条件顺序QnQnQnQn+1Qn+1Qn+1YCPCPCP21021021000000010↑↑↓10010100↓↓↓20100110↑↑↓30111000↓↓↓41001011↑↑↓51010001↓↓↓无效1101111↑↑↓状态1111001↓↓↓//111111题8-3状态转换图及时序图01[题8-4]试用74LS161同步置数功能构成一个十进制计数器,其状态在自然二进制码0110~1111之间循环。解:十进制计数器,即M10,初态为0110,则DDDD0110。主循环中有效态是3210SS,由于初态不为0,因此只能用反馈置数法。74LS161LD是同步置数,因此计到614SQQQQ1110状态时给LD一个置数信号,LDQQQ,电路图如图所示。1432103211111Q0Q1Q2Q3&1CTTCOCTP74LS161CPCRLDD0D1D2D301101题8-4电路图[题8-5]试用74LS160同步置数和异步清零功能构成一个六进制计数器。解:六进制计数器,即M10,初态为0,则DDDD0000。主循环中有效态是SS,32100574LS160LD是同步置数,因此计到SQQQQ0101状态时给LD一个置数信号,53210LDQQ;异步清零,因此计到SQQQQ0110状态时给LD一个清零信号,2053210

LDQQ。电路图如图所示。210110Q0Q1Q2Q31010Q0Q1Q2Q3&&1CT1TCTCOTCTPCTCO74LS160P74LS160CPCPLDCRD0D1D2D3CRLDD0D1D2D31XXXX10000(a)异步清零法(b)同步置数法题8-5电路图[题8-6]试用74LS190异步置数功能构成一个七进制计数器。解:七进制计数器,即M7,初态为0000,则DDDD0000。主循环中有效态是SS,32100674LS190LD是异步置数,因此计到SQQQQ0111状态时给LD一个置数信号,73210LDQQQ,电路图如图所示。210111&0CTQ0Q1Q2Q3RCUD/74LS190COBO/CPDDDD0123LD0000题8-6电路图[题8-7]试用74LS290异步置数功能构成一个八进制计数器。解:八进制计数器,即M8,初态为0000,则DDDD0000。主循环中有效态是SS,32100774LS290是异步置数,因此计到SQQQQ1000状态时给一个置数信号,83210RRQ,电路图如图所示。0AB03Q0Q1Q2Q3CP0CP74LS290CP10S9AS9BR0AR0B题8-7电路图[题8-8]试用74LS191异步置数功能构成一个减法计数器,其状态在自然二进制码1110~0110之间循环。解:初态为1110,则DDDD1110,74LS191LD是异步置数,因此计到3210SQQQQ0101状态时给LD一个置数信号,LDQQ,电路图如图所示。5321031

1010≥10CTQ0Q1Q2Q3RC1UD/74LS191COBO/CPDDDD0123LD0111题8-8电路图[题8-9]试用两片74LS161反馈清零法构成一个四十二进制的计数器。解:同步连接,整体清零法。01010100""""Q0Q1Q2Q3Q0Q1Q2Q3&1CTTCOCTTCOCT74LS161CT74LS161PP(1)(2)LDCR"""D"LDCRD0D1D2D3D0D1D23XXXXXXXXCP题8-9电路图先将两片74LS161接成一个二百五十六进制的计数器,再用整体反馈清零法。74LS161是异步清零,"""""SQQQQQQQQ00101010,CRQQQ4232103210131[题8-10]试用两片74LS290构成一个二十五进制的计数器。[题8-11]试用下降沿JK触发器设计一个递增同步六进制计数器。要求计数器的状态转换代码具有相邻性(相邻两组代码中只有一位代码不同),且代码不包含全0和全1的码组。根据题意列出电路的状态转移真值表和卡诺图;写出状态方程、驱动方程,输出方程,检查启动特性,设计电路能自启动;画出设计的逻辑电路。解:题8-11状态转换表现态次态输出CP脉冲nnnn1n1n1Q2Q1Q0Q2Q1Q0Y000101101011010020101100311010004100101051010011n1n1n1根据表画出次态Q、Q、Q和输出Y的卡诺图,如图所示。210

n+1n+1Q2nnQ1nnQ1Q0Q1Q0Qn00011110Qn00011110220×0010×111110×1100×0(a)(b)n+1Q0QnQnYnn10Q1Q0Qn00011110n000111102Q20×1000×000111×0101×0(c)(d)图8-11次态和输出的卡诺图(a)n1;(b)Qn1;(c)Qn1;(d)YQ210Qn1QQQnnnQQnn210202nnn1nnnn输出方程:YQQ,状态方程:QQQQQ2012121n1nnnnQQQQQ01010n1nn将状态方程和JK触发器的特性方程QJQKQ进行比较,从而求得驱动方程:JQQnn,KQn21020nnJQ,KQ1212nnJQ,KQ0101111/1000Q2Q1Q0/Y/0/0/0001011010/0/1/0/0101100110查电路能自启动:题8-11状态转换图设计电路图略[题8-12]试用边沿JK触发器和门电路设计一个同步五进制计数器,其状态编码如图P8-4状态图所示。根据题意列出电路的状态转移真值表和卡诺图;写出状态方程、驱动方程,输出方程,检查启动特性,设计电路能自启动;画出设计的时序逻辑电路。

Q2Q1Q0/Y/1/1000001010/0/0/1100011图P8-4解:题8-12状态转换真值表现态次态输出CP脉冲顺序QnQnnn+1Qn+1Qn+121Q0Q210Y0000001110010101201001103011100141000000n+1n+1Q2Q1nnnnQ1Q0Q1Q0nQn00011110Q2000111102000100010110×××10×××(a)(b)n+1QYnn0nnQ1Q0Q1Q0nQn00011110Q2000111102010010111010×××10×××(c)(d)图8-12次态和输出的卡诺图(a)n1;(b)Qn1;(c)Qn1;(d)YQ210Qn1QQQnnn2102nnnn1nnnn输出方程:YQQQ,状态方程:QQQQQ21010101n1nnQQQ020n1nn将状态方程和JK触发器的特性方程QJQKQ进行比较,从而求得驱动方程:nnJQQ,1K2102nnJQ,KQ1010nJQ,1K020将3个无效状态101、110、111代入状态方程计算后,获得的次态010、010、000均

为有效状态。因此电路能自启动。设计电路图略。[题8-13]试用上升沿边沿D触发器和与非门设计一个脉冲序列为100110的序列脉冲产生电路,其状态编码如图P8-5状态图所示。根据题意列出电路的状态转移真值表和卡诺图;写出状态方程、驱动方程,输出方程,检查电路自启动特性;画出设计的序列脉冲产生电路。Q2Q1Q0/Y/1/0101000001011/×/0/0/×/1/1010100110111图P8-5解:题8-13状态转换真值表现态次态输出CP脉冲顺序QnQnnn+1n+1n+121Q0Q2Q1Q0Y000000111001011020111110311111014110100151000000101010X无效态010100Xn+1n+1Q2Q1nnnnQ1Q0Q1Q0nQ2n00011110Q20001111000011001101001110110(a)(b)n+1QYnn0nnQ1Q0Q1Q0nQn00011110Q2000111102011100100×1000010×11(c)(d)图8-13次态和输出的卡诺图(a)n1;(b)Qn1;(c)Qn1;(d)YQ210

nn1QQ21nnnnnn1输出方程:YQQQQ,状态方程:QQ202110n1nnnnQQQQQ02120n1将状态方程和D触发器的特性方程QD进行比较,从而求得驱动方程:nDQ21nDQ10nnnnDQQQQ02120电路能自启动。设计电路图略。[题8-14]试用VHDL设计一个4位二进制可逆计数器,该计数器具有同步预置数功能。libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;useieee.std_logic_arith.all;entityt814isport(cp,ld,u_d:instd_logic;d:instd_logic_vector(3downto0);q:outstd_logic_vector(3downto0));endt814;architecturebehaveoft814issignaliq:std_logic_vector(3downto0);beginprocess(cp,ld,u_d)beginelsif(cp"eventandcp="1")thenif(ld="0")theniq<=d;elsif(u_d="0")theniq<=iq+1;elsif(u_d="1")theniq<=iq-1;endif;q<=iq;endprocess;endbehave;[题8-15]试用VHDL设计一个双向移位寄存器。libraryieee;useieee.std_logic_1164.all;entityshifterisport(clk:instd_logic;data:instd_logic_vector(7downto0);shift_left:instd_logic;shift_right:instd_logic;reset:instd_logic;mode:instd_logic_vector(1downto0);qout:bufferstd_logic_vector(7downto0));endentityshifter;architectureartofshifteris

beginprocess(clk)beginif(clk"eventandclk="1")thenif(reset="1")thenqout<="00000000";--同步复位功能的实现elsecasemodeiswhen"01"=>qout<=shift_right&qout(7downto1);--右移一位when"10"=>qout<=qout(6downto0)&shift_left;--左移一位when"11"=>qout<=data;--并行输入whenothers=>null;endcase;endif;endif;endprocess;endarchitectureart;[题8-16]用VHDL设计一个模为12的加法计数器,要求该计数器能够同步清零,异步置数,而且有计数使能端和进位输出端,并用QuartusII软件进行仿真,并给出详细的仿真波形图。libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitycntm12isport(clk,en,cr,sh:instd_logic;d:instd_logic_vector(3downto0);co:outstd_logic;q:bufferstd_logic_vector(3downto0));endentitycntm12;architectureartofcntm12isbeginco<="1"when(q="1011"anden="1")else"0";process(clk,cr)isbeginif(sh="0")thenq<=d(3downto0);elsif(clk"eventandclk="1")thenif(cr="0")thenq<="0000";elsif(en="1")thenif(q="1011")thenq<="0000";elseq<=q+1;endif;endif;endif;endprocess;endarchitectureart;第9章脉冲产生与整形22[题9-1]解:(1)VV128VTDD33

11VV124VTDD33VVV844TTT(2)VV5VTCO11VV52.5VTCO22VVV52.52.5TTT[题9-2]解:T1.1RC1~10S令C=100uF得R=(10~100)Kw15V848.1KVDDRD63THOUTuOu2TR555I100K57CODISuCGNDC100uF10.01uF111[题9-3]解:f9337Hz5T0.7(R2RC)0.7(5.110.2)1012[题9-4]解:ucotuotw1tw2otVVVDDTTTttRClnRClnWW1212VVVDDTT1fVVVDDTTRClnRCln12VVVDDTT[题9-5]解:

AUT+UT-BUT+UT-UO4[题9-6]解:t1.1RC1.110000101.1sWuItwIVIH4VotuCVDD8VotuOVOHtwoVOLot[题9-7]T0.7(RRC)56uS1211f17.85KHzT0.7(RRC)12tRW11q50%TRR12T0.7RC28uSw11ucotuoot

tRW11[题9-8]解:q25%得R=30K2TRR1211由f10000得C2uFT0.7(10K60)KC电路如下:VDD10KR841VCCRD7VDISOUT3uoD130KR26TH555VD252COTRGND2ufC10.01uF[题9-9]解:(1)图中555(1)构成的是单稳态触发器和555(2)构成的是多谐振荡器。电路工作原理:当按下S开关,555(1)的2脚输入一负脉冲,电路进入暂稳态,输出u由O低电平变为高电平,555(2)的4脚得电压,多谐振荡器起振,喇叭发出声音。(2)如果要改变音响的音调,应改变555(2)中R或R的阻值或电容C的容量。342第10章半导体存储器[题10-1]试说明RAM和ROM的区别。解:ROM为只读存储器,工作时存储的数据只能读出,而不能写出数据,断电以后,所存数据不会丢失。随机存储器RAM,工作时既能读出信息又能写入信息。其优点是读、写方便,使用灵活,用于存放需经常改变的信息,但断电以后所存储的数据将随之丢失。[题10-2]RAM有几种不同的类型。解:ROM可分为掩膜只读存储、可编程只读存储器,紫外线可擦除可编程只读存储器,电擦除可编程只读存储和快闪存储器存储器。[题10-3]PROM、EPROM和EEPROM各有什么特点?解:PROM、EPROM和EEPROM都是可编程只读存储器,但它们各有如特点:PROM的存储数据由用户写入,但只能写一次。EPROM的存储数据由用户写入,用紫外线擦除存储的数据,可以多次改写存储的数据。EEPROM的存储数据由用户写入,写入的数据可电擦除,用户可以多次改写存储的数据,使用方便。

[题10-4]2048×8位的存储芯片,地址线和数据线各有几位,有多少个基本存储单元?解:2048×8位的存储芯片,其地址线为11位,数据线为8位,共有2048×8个基本存储单元。[题10-5]试用PROM实现8421BCD转换为格雷码。解:1、列出8421BCD码转换为格雷码的真值表8421BCD码格雷码ABCDG3G2G1G0000000000001000100100011001100100100011001011110011010100111101110001001100110002、画出用PROM实现的逻辑图W0W1W2W3W4W5W6W7W8W9A1B1C1D1&G0≥1G1G2G3[题10-6]试用PROM实现下列逻辑函数,画出阵列图。YABCDBCD1YABCDACBD2YACDABCDBCD3解:(1)将函数化为标准与-或式Ym1(5,7,15)Ym2(1.2,3,4,5,6,7,8,9,10,11,12,13,14)Ym3(3,7,11,14)(2)确定存储单元内容由函数Y1、Y2和Y3的标准与-或式知:将相应存贮单元填1,即对应字线的存贮单元填1。(3)画出用PROM实现的逻辑图

W0W1W2W3W4W5W6W7W8W9W10W11W12W13W14W15A1B1C1D1&&Y1≥1Y2Y3[题10-7]试将2048×2位的RAM扩展为2048×8位的RAM,并画出接图。解:字数够,字长不够,需进行位扩展,2048×8/2048×2=4,需要4片2048×2RAM芯片,其电路如下:I/O0I/O1I/O2I/O3I/O4I/O5I/O6I/O7A0A1...A10R/WCSA0A1...A10R/WCSA0A1...A10R/WCSA0A1...A10R/WCSA0A..1.A10R/WCS[题10-8]试用2K×8位的RAM扩展为8K×8位的RAM,并画出接线图。解:字数不够,字长够,需进行字扩展,8K×8位/2K×8=4,需要4片2K×8RAM芯片,字数扩展需增加地址线,其电路如下:I/O1I/O3I/O5I/O7I/O0I/O2I/O4I/O6A0A1...A10R/WCSA0A1...A10R/WCSA0A1...A10R/WCSA0A1...A10R/WCSA0A..1.A10R/WA11译A12码CS器[题10-9]现有1K×4位的RAM芯片若干,因设计需要4K×8位的RAM电路,试问:(1)需要多少个1K×4位的RAM芯片?(2)画出设计的连接电路。解:(1)字数和字长不够,需进行字数和字长同时扩展,4K×8/1K×4=8,需要8片1K×4位的RAM芯片,先字长扩展,再字数扩展。(2)扩展设计的电路如下:

I/O0I/O1I/O2I/O3I/O4I/O5I/O6I/O72114211421142114A0A1...A9R/WCSA0A1...A9R/WCSA0A1...A9R/WCSA0A1...A9R/WCSA0A..1.A9R/WA10A11译码CS器2114211421142114A0A1...A9R/WCSA0A1...A9R/WCSA0A1...A9R/WCSA0A1...A9R/WCS第11章数模和模数转换器[题11-1]在图11-4所示权电阻网络DAC中,若n=4,开关S1支路中的权电阻为20KΩ,试求其它三个支路中的电阻值。n2解:S1支路阻值R2R20K,n=4,求得R=5K,则:S141R25K40K;S043R25K10K;S244R25K5K。S3[题11-2]设DAC的输出电压为0~2.5V,试求12位D/A转换器的分辨率为多少?解:n位DAC的分辨率为V11LSB分辨率n12V2-12-1FSR1最小可分辨电压2.5V0.6mV122-1[题11-3]若ADC输入的模拟电压不大于5V,则基准电压VREF应为多大?如果转换成8位二进制代码,它能分辨最小的模拟电压为多大?16位转换呢?解:基准电压VREF也为5V,转换为8位二进制代吗时,能分辨的最小模拟电压约为:V5VREF19.6mVn82-12-1V5VREF16位时的最小模拟电压分辨率为:76Vn162-12-1[题11-4]向8位集成DAC0832输入二进制数据“10010110”,采用5V供电,可输出多大模拟电压?

D(10010110)2解:VV5V3.24VOUTnREF822[题11-5]什么是量化、量化值、量化单位及量化误差?答:将取样后的样值电压变为量化单位整数倍的过程称为量化;将量化的样值电压变换成与其成正比的数字量即为量化值;通常将数字信号最低位(LSB)为1时(即00……01)对应的模拟电压作为量化单位,用Δ表示;量化时,不能被Δ整除的样值电压的非整数部分的余数会被舍去,从而产生量化误差。[题11-6]实现AD转换需要哪四个步骤?答:实现AD转换需要经过取样、保持、量化、编码四个步骤[题11-7]试比较并联比较型、逐次逼近型和双积分型三种ADC的主要优点和缺点,指出它们各自在什么场合下采用?并联比较型速度最快,但价格也最高;双积分型精度最高,转换速度最慢;逐次逼近型速度和精度比较适中。在需要高速采样的场合,使用并联比较型,如视频数据数字化;在需要高精度且速度要求不高的场合,使用双积分型,如数字万用表;结合速度和精度的优势,逐次逼近型应用最为广泛,足够满足绝大多数应用。[题11-8]接在AD0809IN1通道上的模拟电压为2.3V,采用5V供电,得到的数字量为多少?822.3解:D118(01110110)25故数字量为01110110.[题11-9]请根据AD0809的工作原理及过程,用VHDL完成图11-13所示的AD0809的控制程序设计。解:下面给出AD0809的VHDL状态机例程libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entityMachine_0809isport(Din:instd_logic_vector(7downto0);---接收0809的采样值Dout:outstd_logic_vector(7downto0);---将0809采样的数据输出Addr:outstd_logic_vector(2downto0);---控制0809通道地址ALE,Start,OE:outstd_logic;---0809的控制信号ADCp:bufferstd_logic;---0809的时钟信号EOC,clk,rst:instd_logic);---外部控制信号endMachine_0809;architecturebehvofMachine_0809issignalData:std_logic_vector(7downto0);typestateis(st0,st1,st2,st3,st4);signalns,ps:state;

signallock,Mclk:std_logic;beginAddr<="000";REG:process(Mclk)begin--ifrst="1"thenps<=st0;ifMclk"eventandMclk="1"thenps<=ns;endif;endprocessREG;COM:process(ps)begincasepsiswhenst0=>ALE<="0";Start<="0";OE<="0";lock<="0";ns<=st1;whenst1=>ALE<="1";Start<="1";OE<="0";lock<="0";ns<=st2;whenst2=>ALE<="0";Start<="0";OE<="0";lock<="0";ifEOC="0"thenns<=st2;elsens<=st3;endif;whenst3=>ALE<="0";Start<="0";OE<="1";lock<="0";ns<=st4;whenst4=>ALE<="0";Start<="0";OE<="1";lock<="1";ns<=st0;whenothers=>ns<=st0;endcase;endprocessCOM;Latch:process(lock)beginiflock"eventandlock="1"thenData<=Din;endif;endprocessLatch;P3:process(clk)variablecnt:std_logic_vector(5downto0);beginifclk"eventandclk="1"thencnt:=cnt+1;endif;--endif;Mclk<=cnt(2);---状态机状态周期为2ns*8=16ns,AD0809的去start信号为高电平的最短停留时间

ADCp<=cnt(5);endprocess;Dout<=Data;endbehv;[题11-10]设计一个正弦波发生器,通过计数器连续读取ROM中预存的波形码数据,送给DAC,转换为模拟电压后再经低通滤波器做平滑滤波,合成线性度较好的正弦波。(正弦波频率不做要求)解:一个周期内正弦波码表样点越多,波形越好,这里采用256点正弦波存入ROM。使用8位二进制计数器作为地址发生器顺序访问,将读出的ROM数据直接送给DAC即可。256点正弦波码表样值数据如下:正弦波(0700~07FFH)808386898D909396-999C9FA2A5A8ABAEB1B4B7BABCBFC2C5-C7CACCCFD1D4D6D8DADDDFE1E3E5E7E9-EAECEEEFF1F2F4F5F6F7F8F9FAFBFCFD-FDFEFFFFFFFFFFFFFFFFFFFFFFFFFEFD-FDFCFBFAF9F8F7F6F5F4F2F1EFEEECEA-E9E7E5E3E2DFDDDAD8D6D4D1CFCCCAC7-C5C2BFBCBAB7B4B5AEABA8A5A29F9C99-9693908D89868380807C7976726F6C69-6663605D5A5755514E4C484543403D3A-383533302E2B29272522201E1C1A1816-151311100E0D0B0A0908070605040302-02010000000000000000000000000102-02030405060708090A0B0D0E10111315-16181A1C1E20222527292B2E30333538-3A3D404345484C4E5155575A5D606366-696C6F7276797C80第12章可编程逻辑器件及其应用[题12-1]可编程逻辑器件的主要分类依据是什么?可以划分为哪几个大类?答:按集成度、阵列结构、编程工艺来进行划分[题12-2]比较PAL、GAL、CPLD及FPGA可编程逻辑器件各自的特点。答:PAL的或阵列是固定的,只有与阵列可编程;GAL是在PAL的基础上“进化”而来,开始采用EEPOM工艺,从而可以进行重复编程,克服了上述三种器件只能一次编程的问题;CPLD即复杂可编程逻辑器件,是在PAL、GAL基础上发展起来的;

FPGA即现场可编程门阵列,是一种新型高性能可编程逻辑器件,它一般采用SRAM工艺。[题12-3]GAL和PAL的相同点是什么?最大的不同是什么?答:相同点是都采用阵列结构不同点是GAL对输出I/O进行了较大改进,增加了OLMC(OutputLogicMacroCell,输出逻辑宏单元),为逻辑电路设计提供了极大的灵活性。[题12-4]就编程原理而言,FPGA与PAL和GAL有什么不同。答:FPGA基于SRAM工艺,可以在线编程;PAL基于熔丝工艺,只能一次编程GAL基于EEPROM工艺,可以反复擦除编程[题12-5]简述CPLD/FPGA的原理、特点与应用。答:CPLD和FPGA都是基于反复可编程的思路发展起来的,前者基于乘积项结构,具有典型的组合逻辑电路特征,后者基于查找表结构,具有典型的时序逻辑电路特征。[题12-6]简述FPGA的基本结构。答:FPGA的结构较为复杂,不同厂商产品的基本构架都可简化为6个部分,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。[题12-7]FPGA与CPLD都是大规模可编程逻辑器件,它们的结构有什么不同?使用上有什么区别?答:FPGA基于查找表结构、CPLD基于乘积项结构;使用上FPGA更适合用作时序逻辑电路设计,如算法设计;CPLD更适合组合逻辑电路设计,如时序控制。[题12-8]CPLD/FPGA的几大供应厂商是哪几个?答:ALTERA、Xilinx、ACTEL、Lattice[题12-9]目前市场份额最大的两大CPLD/FPGA供应厂商是哪两个?它们各自使用什么软件平台?答:ALTERA,使用QuartusII;Xilinx,使用ISE。[题12-10]简述使用QuartusII软件进行FPGA开发的基本流程。原理图/HDL文本编辑功能仿真综合逻辑综合器结构综合器FPGA/CPLDFPGA/CPLD时序与功能器件和电路系统适配门级仿真FPGA/CPLD编程下载第13章数字系统设计基础[题13-1]试画出8位可逆计数器的状态图,并用VHDL语言进行描述。解:状态图略。VHDL源代码如下:

libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitycnt_8isport(clk:instd_logic;--时钟输入端口k:instd_logic;--加减控制输入端口clr:instd_logic;--清零端口en:instd_logic;--使能控制端口m:instd_logic;--置数控制端口n:instd_logic_vector(7downto0);--置数输入q:outstd_logic_vector(7downto0)--数值输出);endcnt_8;architecturecnt_8_archofcnt_8issignalqq:std_logic_vector(7downto0);beginprocess(clk,clr,k,n)beginifm="1"thenqq<=n;--检测是否允许置数elsifclr="1"then--检测是否清零qq<="00000000";elsifclk"eventandclk="1"then--检测时钟上升沿ifen="1"then--允许计数ifk="1"then--加法计数qq<=qq+"1";elseqq<=qq-"1";--减法计数endif;endif;endifendprocess;process(qq)beginq<=qq;--将计数值向端口输出endprocess;endcnt_8_arch;[题13-2]在数字信号的接收中,有时需要接收一组特定的串行数字信号,接收该信号的电路称为序列信号检测器。用状态机的设计方法描述一个序列信号检测器,成功接收并检测到序列信号“10011101”后,输出一个标志信号位。画出状态图,给出相应的VHDL代码。解:状态图略VHDL源代码如下:libraryieee;

useieee.std_logic_1164.all;entitysequence_dectectorisport(clk,rst,d:inbit;--clk为时钟信号,rst为复位控制信号,d为输入待检测信号q:outbit);--q为标志位endsequence_dectector;architecturebehaviorofsequence_dectectoristypestateis(state1,state2,state3,state4,state5,state6,state7,state8);signalpresent_state,next_state:state;beginprocess(rst,clk)--状态机时序逻辑部分的设计beginif(rst="1")thenpresent_state<=state1;--复位elsif(clk"eventandclk="1")thenpresent_state<=next_state;--时钟上升沿状态更新endif;endprocess;process(d,present_state)--状态机中组合逻辑部分的设计begincasepresent_stateiswhenstate1=>q<="0";if(d="1")thennext_state<=state2;elsenext_state<=state1;endif;whenstate2=>q<="0";if(d="0")thennext_state<=state3;elsenext_state<=state1;endif;whenstate3=>q<="0";if(d="0")thennext_state<=state4;elsenext_state<=state1;endif;whenstate4=>q<="0";if(d="1")thennext_state<=state5;elsenext_state<=state1;endif;whenstate5=>q<="0";if(d="1")thennext_state<=state6;elsenext_state<=state1;

endif;whenstate6=>q<="0";if(d="1")thennext_state<=state7;elsenext_state<=state1;endif;whenstate7=>q<="0";if(d="0")thennext_state<=state8;elsenext_state<=state1;endif;whenstate8=>if(d="1")thennext_state<=state1;q<="1";elsenext_state<=state1;q<="0";endif;endcase;endprocess;endbehavior;[题13-3]设计一个具备定时和信息显示功能的微波炉控制器。要求该微波炉控制器能够在任意时刻取消当前工作,复位为初始状态;可以根据需要设置烹调时间的长短,系统最长的烹调时间为59分59秒,开始烹调后,能够显示剩余时间的多少;能够显示微波炉控制器的烹调状态。解:设计分析:根据设计要求,该微波炉控制器可由以下四个电路模块组成:状态控制电路,其功能是控制微波炉工作过程中的状态转换,并发出相关控制信号;数据装载电路,其功能是根据控制信号选择定时时间,测试数据或计时完成信息的载入;计时电路,其功能是对时钟进行减法计数,提供烹调完成时的状态信号;显示译码电路,其功能是显示微波炉控制器的各状态信息。设clk为时钟输入信号,时钟上升沿敏感;reset为复位信号,高电平有效时系统复位清零;test为数码显示管测试信号,高电平有效,用于测试显示管是否正常工作;set_t为烹调时间设置信号,高电平有效时允许设置烹调时间;data为定时时间输入信号,用于设置烹调时间的长短,其由高到低分别表示定时时间分、秒的十位,个位;start为烹调开始信号,高电平有效时开始烹调;输出信号cook指示微波炉状态,高电平时表示烹调进行时;sec0、sec1、min0、min1分别表示秒个位、秒十位、分个位、分十位。VHDL源代码如下:(1)状态控制电路的VHDL实现如下:libraryieee;useieee.std_logic_1164.all;useieee.std_logic_arith.all;entitycontrolleris

port(reset,set_t,start,test,clk,done:instd_logic;cook,ld_test,ld_clk,ld_done:outstd_logic);endcontroller;architecturertlofcontrolleristypestatesis(idle,lamp_test,set_clock,timer,done_msg);signalnxt,cur:states;beginprocess(clk,reset)beginifreset=‘1’thencur<=idle;elsif(clk’eventandclk=‘1’)thencur<=nxt;endif;endprocess;process(clk,cur,set_t,start,test,done)beginnext<=idle;ld_test<=’0’;ld_done<=’0’;ld_clk<=’0’;cook<=’0’;casecuriswhenlamp_test=>ld_test<=’1’;cook<=’0’;whenset_clock=>ld_clk<=’1’;cook<=’0’;whendone_msg=>ld_done<=’1’;cook<=’0’;whenidle=>

iftest=’1’thennxt<=lamp_test;ld_test<=’1’;elsifset_t=’1’thennxt<=set_clock;ld_clk<=’1’;elsifstart=’1’anddone=’0’thennxt<=timer;cook<=’1’;endif;whentimer=>ifdone=’1’thennxt<=done_msg;ld_done<=’1’;elsenxt<=timer;cook<=’1’;endif;endcase;endprocess;endrtl;(2)数据装载电路的VHDL实现如下:libraryieee;useieee.std_logic_1164.all;useieee.std_logic_arith.all;entityloaderisport(ld_test,ld_clk,ld_done:instd_logic;datain:instd_logic_vector(15downto0);dataout:outstd_logic_vector(15downto0);load:outstd_logic);endloader;architecturertlofloaderis

beginprocess(datain,ld_test,ld_clk,ld_done)constantalls:std_logic_vector(15downto0):=”1000100010001000”;constantdone:std_logic_vector(15downto0):=”1010101111001101”;variabletemp:std_logic_vector(2downto0);beginload<=ld_testorld_doneorld_clk;temp:=ld_test&ld_done&ld_clk;casetempiswhen“100”=>dataout<=alls;when“010”=>dataout<=done;when“001”=>dataout<=datain;whenothers=>null;endcase;endprocess;endrtl;(3)计时电路的VHDL实现如下:--十进制减法计数器libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitycnt10isport(clk,load,en:instd_logic;datain:instd_logic_vector(3downto0);q:outstd_logic_vector(3downto0);carry_out:outstd_logic);endcnt10;architecturertlofcnt10issignaltmp:std_logic_vector(3downto0);begin

process(clk,load,en)beginifload="1"thentmp<=datain;elsif(clk’eventandclk=’1’)thenifen="1"theniftmp<=”0000”thentmp<=”1001”;elsetmp<=tmp-‘1’;endif;endif;endif;endprocess;process(clk,tmp)beginif(clk’eventandclk=’1’)theniftmp<=”0000”thencarry_out<=’1’;elsecarry_out<=’0’;endif;endif;endprocess;q<=tmp;endrtl;--六进制减法计数器libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitycnt6isport(clk,load,en:instd_logic;datain:instd_logic_vector(3downto0);q:outstd_logic_vector(3downto0);

carry_out:outstd_logic);endcnt6;architecturertlofcnt6issignaltmp:std_logic_vector(3downto0);beginprocess(clk,load,en)beginifload="1"thentmp<=datain;elsif(clk’eventandclk=’1’)thenifen="1"theniftmp<=”0000”thentmp<=”0101”;elsetmp<=tmp-‘1’;endif;endif;endif;endprocess;process(clk,tmp)beginif(clk’eventandclk=’1’)theniftmp<=”0000”thencarry_out<=’1’;elsecarry_out<=’0’;endif;endif;endprocess;q<=tmp;endrtl;(4)计数器电路模块设计libraryieee;

useieee.std_logic_1164.all;entitycounterisport(cook,load,clk:instd_logic;datain:instd_logic_vector(15downto0);sec0,sec1,min0,min1:outstd_logic_vector(3downto0);done:outstd_logic);endcounter;architecturertlofcounteriscomponentcnt10isport(clk,load,en:instd_logic;datain:instd_logic_vector(3downto0);q:outstd_logic_vector(3downto0);carry_out:outstd_logic);endcomponentcnt10;componentcnt6isport(clk,load,en:instd_logic;datain:instd_logic_vector(3downto0);q:outstd_logic_vector(3downto0);carry_out:outstd_logic);endcomponentcnt6;signalclk0:std_logic;signals0:std_logic;signals1:std_logic;signals2:std_logic;signals3:std_logic;beginu1:cnt10portmap(clk,load,cook,data(3downto0),sec0,s0);u2:cnt6portmap(s0,load,cook,data(7downto4),sec1,s1);u3:cnt10portmap(s1,load,cook,data(11downto8),min0,s2);u4:cnt6portmap(s2,load,cook,data(15downto12),min1,s3);done<=s0ands1ands2ands3;

endrtl;(5)顶层模块的VHDL实现如下:libraryieee;useieee.std_logic_1164.all;entitytopisport(reset,set_t,start,test,clk:instd_logic;data:instd_logic_vector(15downto0);sec0,sec1,min0,min1:outstd_logic_vector(3downto0);cook:outstd_logic);endtop;architecturertloftopiscomponentcontrollerisport(reset,set_t,start,test,clk,done:instd_logic;cook,ld_test,ld_clk,ld_done:outstd_logic);endcomponentcontroller;componentloaderisport(datain:instd_logic_vector(15downto0);ld_test,ld_clk,ld_done:instd_logic;dataout:outstd_logic_vector(15downto0);load:outstd_logic);endcomponentloader;componentcounterisport(clk,load,cook:instd_logic;datain:instd_logic_vector(15downto0);sec0,sec1,min0,min1:outstd_logic_vector(3downto0);done:outstd_logic);endcomponentcounter;signalcook_tmp:std_logic;signaltest_tmp:std_logic;signalclk_tmp:std_logic;

signaldone_tmp:std_logic;signalload_tmp:std_logic;signaldone:std_logic;signaldata_tmp:std_logic_vector(15downto0);begincook<=cook_tmp;u1:controllerportmap(reset,set_t,start,test,clk,done,cook_tmp,test_tmp,clk_tmp,done_tmp);u2:loaderportmap(data,test_tmp,clk_tmp,done_tmp,data_tmp,loda_tmp);u3:counterportmap(cook_tmp,load_tmp,clk,data_tmp,sec0,sec1,min0,min1,done);endrtl;[题13-4]设计一块数字秒表,能够精确反映计时时间,并完成复位、计时功能。秒表计时的最大范围为1小时,精度为0.01秒。秒表可得到计时时间的分、秒、0.1秒等度量,且各度量单位可以正确进位;当复位清零有效时,秒表清零并做好计时准备。在任何情况下,只要按下复位开关,秒表都要无条件地进行复位操作,即使在计时过程中也要无条件地清零;设置秒表启动/停止开关。按下该开关,秒表即刻开始计时,并得到计时结果;放开该开关时,计时停止。解:设计分析:根据上述设计要求,可以预先设计若干个不同进制的计数器单元模块,然后将其进行例化组合来得到数字秒表系统。要满足数字秒表的精度,首先要获得精确的计时基准信号,这里的系统精度要求为0.01秒,因此必须设置周期为0.01秒的时钟脉冲。0.01秒、0.1秒、秒、分等计时单位之间的进位转换可以通过不同进制的计数器实现。设置十进制计数器和六进制计数器,每位计数器均能输出相应计时单位计数结果,其中,十进制计数器可以实现0.01秒、0.1秒、秒、分为单位的计数,六进制计数器可以实现以10秒、10分为单位的计数。把各级计数器级联,即可同时显示0.01秒、0.1秒、1秒、1分钟。级联可分为串行进位方式和并行进位方式。在串行进位方式中,以低位片的进位输出信号作为高位片的时钟输入信号。在并行进位方式中,以低位片的进位输出信号作为高位片的工作状态信号(计数的使能信号en),两片的clk端同时接计数输入信号。VHDL源代码如下:--十进制计数器设计libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitycounter10isport(clr,clk,en:instd_logic;co:outstd_logic;q:outstd_logic_vector(3downto0));endcounter10;architecturertlofcounter10is

signalqtemp:std_logic_vector(3downto0);beginprocess(clr,clk,en)beginif(clr="1")thenqtemp<="0000";elsif(clk"eventandclk="1")thenif(en="1")thenifqtemp="1001"thenqtemp<="0000";elseqtemp<=qtemp+1;endif;endif;endif;endprocess;process(qtemp)beginif(qtemp="1001")thenco<="1";elseco<="0";endif;endprocess;q<=qtemp;endrtl;--六进制计数器设计libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitycounter6isport(clr,clk,en:instd_logic;co:outstd_logic;q:outstd_logic_vector(3downto0));endcounter6;architecturertlofcounter6issignalqtemp:std_logic_vector(3downto0);beginprocess(clr,clk,en)beginif(clr="1")thenqtemp<="0000";elsif(clk"eventandclk="1")thenif(en="1")then

ifqtemp="0101"thenqtemp<="0000";elseqtemp<=qtemp+1;endif;endif;endif;endprocess;process(qtemp)beginif(qtemp="0101")thenco<="1";elseco<="0";endif;endprocess;q<=qtemp;endrtl;--数字秒表顶层模块设计libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitystopwatchisport(clr1,clk1,en:instd_logic;qout:outstd_logic_vector(23downto0));endstopwatch;architecturertlofstopwatchiscomponentcounter10isport(clr,clk,en:instd_logic;co:outstd_logic;q:outstd_logic_vector(3downto0));endcomponentcounter10;componentcounter6isport(clr,clk,en:instd_logic;co:outstd_logic;q:outstd_logic_vector(3downto0));endcomponentcounter6;signalco1,co2,co3,co4,co5:std_logic;--begin--元件例化,通过计数器级联实现数字秒表u1:counter10portmap(clk=>clk1,clr=>clr1,en=>en,q=>qout(3downto0),co=>co1);u2:counter10portmap(clk=>co1,clr=>clr1,en=>en,q=>qout(7downto4),co=>co2);u3:counter10portmap(clk=>co2,clr=>clr1,en=>en,q=>qout(11downto8),co=>co3);

u4:counter6portmap(clk=>co3,clr=>clr1,en=>en,q=>qout(15downto12),co=>co4);u5:counter10portmap(clk=>co4,clr=>clr1,en=>en,q=>qout(19downto16),co=>co5);u6:counter6portmap(clk=>co5,clr=>clr1,en=>en,q=>qout(23downto20));endrtl;[题13-5]设计一个满足日常生活所需功能的出租车计费器。该计费器能实现计费功能。车起步开始计费,首先显示起步价,起步费为3.00元,车在行驶3公里以内,只收起步价。车行驶超过3公里后,每公里2元,车费依次累加。当总费用达到或超过40元时,每公里收费4元。当遇到红灯或客户需要停车等待时,则按时间计费,计费单价为每20s收费1元;实现计费器预置功能,能够预置起步费、每公里收费、车行加费里程、计时收费等;可以模拟汽车行驶、停止、暂停等状态,并根据不同状态进行计费;以十进制显示出租车行驶路程与车费。解:设计分析:根据设计要求,整个出租车计费系统按功能主要分为速度模块、计程模块、计时模块和计费模块。速度模块:通过对速度信号sp的判断,决定变量kinside的值。kinside即是进行100m所需要的时钟周期数,然后每行进100m,则产生一个脉冲clkout。计程模块:由于一个clkout信号代表行进100m,故通过对clkout计数,可以获得共行进的距离kmcount。计时模块:在汽车启动后,当遇到顾客等人或红灯时,出租车采用计时收费的方式。通过对速度信号sp的判断决定是否开始记录时间。当sp=0时,开始记录时间。当时间达到足够长时则产生timecount脉冲,并重新计时。一个timecount脉冲相当于等待的时间达到了时间计费的长度。这里选择系统时钟频率为500hz,20s即计数值为1000。计费模块由两个进程组成。其中,一个进程根据条件对enable和price赋值:当记录的距离达到3公里后enable变为1,开始进行每公里收费,当总费用大于40元,则单价price由原来的2元每公里变为4元每公里;第二个进程在每个时钟周期判断timecount和clkout的值。当其为1时,则在总费用上加上相应的费用。该电路系统结构框图如下所示:判断priceKmmoney总费用Speed模块clkout模块判断KilometersTime模块总里程timecount模块'

您可能关注的文档

- 数字电子技术第三章习题答案.doc

- 数字电子技术课后习题答案(全部).doc

- 数字电路与系统设计课后答案.pdf

- 数字电路与逻辑设计课后答案邹红.pdf

- 数字电路习题解答.doc

- 数字电路逻辑设计课后答案.docx

- 数字通信原理课后习题答案.doc

- 数字逻辑习题答案 毛法尧 第二版.doc

- 数字逻辑第四章课后答案.doc

- 数字集成电路教程课后答案.pdf

- 数学书籍推荐.docx

- 数学新浙教版八年级5.1《常量与变量》同步练习题【带详解答案】.doc

- 数学模型第三版(高等教育出版社)课后习题答案.doc

- 数学模型第三版)课后习题答案.doc

- 数学模型第三版_课后习题答案.doc

- 数学模型第四版课后答案姜启源版.doc

- 数学物理方程与特殊函数(王元明)课后答案.pdf

- 数学物理方程习题解答案.doc

相关文档

- 施工规范CECS140-2002给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程

- 施工规范CECS141-2002给水排水工程埋地钢管管道结构设计规程

- 施工规范CECS142-2002给水排水工程埋地铸铁管管道结构设计规程

- 施工规范CECS143-2002给水排水工程埋地预制混凝土圆形管管道结构设计规程

- 施工规范CECS145-2002给水排水工程埋地矩形管管道结构设计规程

- 施工规范CECS190-2005给水排水工程埋地玻璃纤维增强塑料夹砂管管道结构设计规程

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程(含条文说明)

- cecs 141:2002 给水排水工程埋地钢管管道结构设计规程 条文说明

- cecs 140:2002 给水排水工程埋地管芯缠丝预应力混凝土管和预应力钢筒混凝土管管道结构设计规程 条文说明

- cecs 142:2002 给水排水工程埋地铸铁管管道结构设计规程 条文说明